### **INFORMACIJE**

Strokovno društvo za mikroelektroniko elektronske sestavne dele in materiale

# MIDEM

1.2009

Strokovna revija za mikroelektroniko, elektronske sestavne dele in materiale Journal of Microelectronics, Electronic Components and Materials

INFORMACIJE MIDEM, LETNIK 39, ŠT. 1(129), LJUBLJANA, marec 2009

LNIV

Laboratorij za načrtovanje integriranih vezij

FAKULTETA ZA ELEKTROTEHNIKO

UNIVERZA V LJUBLJANI

### **INFORMACIJE**

### **MIDEM**

1 • 2009

INFORMACIJE MIDEM

LETNIK 39, ŠT. 1(129), LJUBLJANA,

MAREC 2009

INFORMACIJE MIDEM

VOLUME 39, NO. 1(129), LJUBLJANA

**MAREC 2009**

Revija izhaja trimesečno (marec, junij, september, december). Izdaja strokovno društvo za mikroelektroniko, elektronske sestavne dele in materiale - MIDEM. Published quarterly (march, june, september, december) by Society for Microelectronics, Electronic Components and Materials - MIDEM.

Glavni in odgovorni urednik

**Editor in Chief**

Dr. Iztok Šorli, univ. dipl.inž.fiz., MIKROIKS, d.o.o., Ljubljana

Tehnični urednik **Executive Editor**

Dr. Iztok Šorli, univ. dipl.inž.fiz., MIKROIKS, d.o.o., Ljubljana

Uredniški odbor **Editorial Board**

Dr. Barbara Malič, univ. dipl.inž. kem., Institut "Jožef Stefan", Ljubljana Prof. dr. Slavko Amon, univ. dipl.inž. el., Fakulteta za elektrotehniko, Ljubljana Prof. dr. Marko Topič, univ. dipl.inž. el., Fakulteta za elektrotehniko, Ljubljana

Prof. dr. Rudi Babič, univ. dipl.inž. el., Fakulteta za elektrotehniko, računalništvo in informatiko Maribor

Dr. Marko Hrovat, univ. dipl.inž. kem., Institut "Jožef Stefan", Ljubljana Dr. Wolfgang Pribyl, Austria Mikro Systeme Intl. AG, Unterpremstaetten

Časopisni svet International Advisory Board Prof. dr. Janez Trontelj, univ. dipl.inž. el., Fakulteta za elektrotehniko, Ljubljana,

PREDSEDNIK - PRESIDENT Prof. dr. Cor Claeys, IMEC, Leuven

Dr. Jean-Marie Haussonne, EIC-LUSAC, Octeville

Darko Belavič, univ. dipl.inž. el., Institut "Jožef Stefan", Ljubljana

Prof. dr. Zvonko Fazarinc, univ. dipl.inž., CIS, Stanford University, Stanford

Prof. dr. Giorgio Pignatel, University of Padova

Prof. dr. Stane Pejovnik, univ. dipl.inž., Fakulteta za kemijo in kemijsko tehnologijo, Ljubljana

Dr. Giovanni Soncini, University of Trento, Trento

Prof. dr. Anton Zalar, univ. dipl.inž.met., Institut Jožef Stefan, Ljubljana Dr. Peter Weissglas, Swedish Institute of Microelectronics, Stockholm

Prof. dr. Leszek J. Golonka, Technical University Wrocław

Naslov uredništva Headquarters

Uredništvo Informacije MIDEM

MIDEM pri MIKROIKS

Stegne 11, 1521 Ljubljana, Slovenija + 386 (0)1 51 33 768 + 386 (0)1 51 33 771 e-pošta: lztok.Sorli@guest.arnes.si http://www.midem-drustvo.si/

Letna naročnina je 100 EUR, cena posamezne številke pa 25 EUR. Člani in sponzorji MIDEM prejemajo Informacije MIDEM brezplačno. Annual subscription rate is EUR 100, separate issue is EUR 25. MIDEM members and Society sponsors receive Informacije MIDEM for free.

Znanstveni svet za tehnične vede je podal pozitivno mnenje o reviji kot znanstveno-strokovni reviji za mikroelektroniko, elektronske sestavne dele in materiale. Izdajo revile sofinancirajo ARRS in sponzorji društva.

Scientific Council for Technical Sciences of Slovene Research Agency has recognized Informacije MIDEM as scientific Journal for microelectronics, electronic components and materials.

Publishing of the Journal is financed by Slovene Research Agency and by Society sponsors.

Znanstveno-strokovne prispevke objavljene v Informacijah MIDEM zajemamo v podatkovne baze COBISS in INSPEC.

Prispevke iz revije zajema ISI® v naslednje svoje produkte: Sci Search®, Research Alert® in Materials Science Citation Index™

Scientific and professional papers published in Informacije MIDEM are assessed into COBISS and INSPEC databases.

The Journal is indexed by ISI® for Sci Search®, Research Alert® and Material Science Citation Index™

Po mnenju Ministrstva za informiranje št.23/300-92 šteje glasilo Informacije MIDEM med proizvode informativnega značaja.

Grafična priprava in tisk

Printed by

BIRO M, Ljubljana

Naklada

1000 izvodov

Circulation

1000 issues

Poštnina plačana pri pošti 1102 Ljubljana

Slovenia Taxe Percue

| JDK621.3:(53+54+621+66), ISSN0352-9045                                                                                                                                                                                          |    | Informacije MIDEM 39(2009)1, Ljubljana                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ZNANSTVENO STROKOVNI PRISPEVKI                                                                                                                                                                                                  |    | PROFESSIONAL SCIENTIFIC PAPERS                                                                                                                                                                   |

| G. Cijan, T. Tuma, S. Tomažič, Á. Bűrmen:<br>Hitra optimizacija neujemanja MOS tranzistorjev –<br>primerjava različnih pristopov                                                                                                | 1  | G. Cijan, T. Tuma, S. Tomažič, Á. Bűrmen:<br>Fast MOS Transistor Mismatch Optimization – A<br>Comparison Between Different Approaches                                                            |

| A. Levstek, M. Pirc:<br>SMD filmski kondenzatorji za integracijske<br>A/D pretvornike                                                                                                                                           | 7  | A. Levstek, M. Pirc:<br>SMD Film Capacitors For Integrating A/D Converters                                                                                                                       |

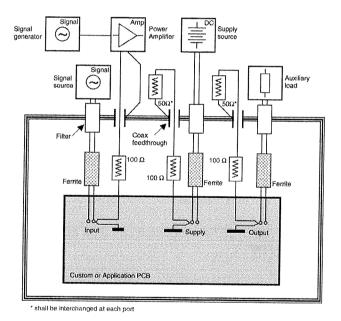

| J. Koselj, D. Strle:<br>Elektromagnetna združljivost v<br>integriranih vezjih: pregled                                                                                                                                          | 16 | J. Koselj, D. Strle:<br>Electromagnetic Compatibility in Integrated<br>Circuits: A Review                                                                                                        |

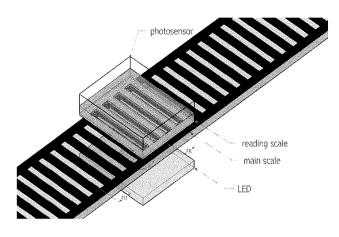

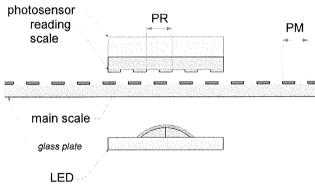

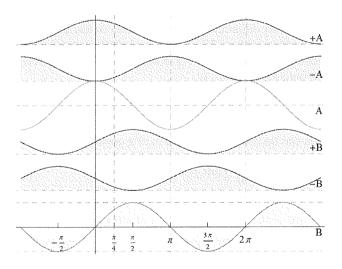

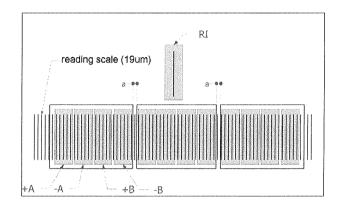

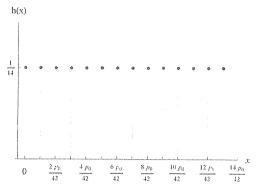

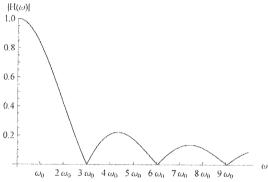

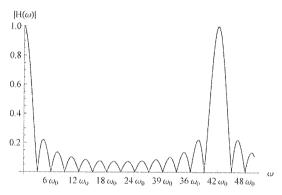

| J. Rozman, A. Pleteršek:<br>Optični dekodirnik z izboljšano linearnostjo                                                                                                                                                        | 22 | J. Rozman, A. Pleteršek:<br>Optical Encoder Head With Improved Linearity                                                                                                                         |

| M.Bizjak:<br>Izklop trifaznega kratkostičnega toka s tripolnim<br>nizkonapetostnim odklopnikom                                                                                                                                  | 28 | M.Bizjak:<br>Breaking of Three-phase Short-circuit Current by<br>Three-pole Molded-case Circuit Breaker                                                                                          |

| A. Jarc, J. Perš, P. Rogelj, S. Kovačič:<br>Učinkovito vzorčenje za vrednotenje kriterijskih<br>funkcij za 2-d togo poravnavo slik                                                                                              | 33 | A. Jarc, J. Perš, P. Rogelj, S. Kovačič:<br>Efficient Sampling for the Evaluation Protocol for 2-d<br>Rigid Registration                                                                         |

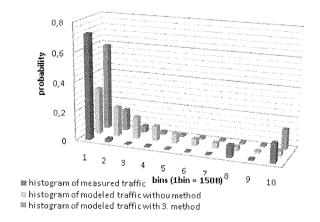

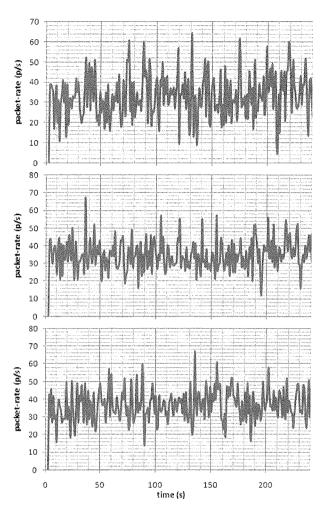

| M. Fras, J. Mohorko, Ž. Čučej:<br>Nov pristop k modeliranju samo-podobnega prometa<br>v simulacijah                                                                                                                             | 41 | M. Fras, J. Mohorko, Ž. Čučej:<br>A New Approach to the Modeling of Network Traffic in<br>Simulations                                                                                            |

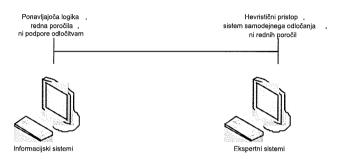

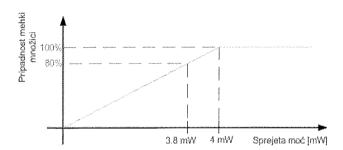

| S. Klampfer, J. Mohorko, Ž. Čučej:<br>Ekspertni sistem za analizo rezultatov simulacij<br>taktičnih radijskih omrežij                                                                                                           | 46 | S. Klampfer, J. Mohorko, Ž. Čučej:<br>Expert System for Analysis of Tactical<br>Radio Networks Simulations                                                                                       |

| I. Fajfar, T. Tuma, Á. Bűrmen, J. Puhan:<br>Pristop k učenju programiranja vgrajenih<br>sistemov z vrha navzdol                                                                                                                 | 53 | I. Fajfar, T. Tuma, Á. Bűrmen, J. Puhan:<br>A Top Down Approach to Teaching Embedded<br>Systems Programming                                                                                      |

| MIDEM prijavnica                                                                                                                                                                                                                | 61 | MIDEM Registration Form                                                                                                                                                                          |

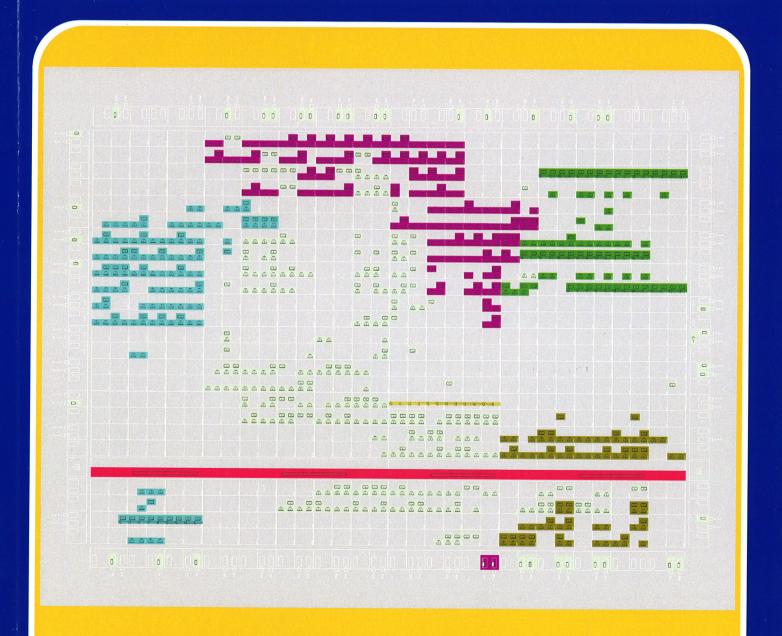

| Slika na naslovnici: Programirljivo vezje FPGA iz družine Xilinx Spartan-3, v katerem je implementirano vezje za prenos video signala. Z barvami je prikazana zasedenost logičnih blokov vezja FPGA s posameznimi sklopi vezja. |    | Front page: Programmable Xilinx Spartan-3 family FPGA Integrated Circuit With an Implemented Video Transmission Circuit. Occupied Logic Blocks are Shown in Colours According to Their Occupancy |

and Function.

### Obnovitev članstva v strokovnem društvu MIDEM in iz tega izhajajoče ugodnosti in obveznosti

Spoštovani,

V svojem več desetletij dolgem obstoju in delovanju smo si prizadevali narediti društvo privlačno in koristno vsem članom. Z delovanjem društva ste se srečali tudi vi in se odločili, da se v društvo včlanite. Življenske poti, zaposlitev in strokovno zanimanje pa se z leti spreminjajo, najrazličnejši dogodki, izzivi in odločitve so vas morda usmerili v povsem druga področja in vaš interes za delovanje ali članstvo v društvu se je z leti močno spremenil, morda izginil. Morda pa vas aktivnosti društva kljub temu še vedno zanimajo, če ne drugače, kot spomin na prijetne čase, ki smo jih skupaj preživeli. Spremenili so se tudi naslovi in način komuniciranja.

Ker je seznam članstva postal dolg, očitno pa je, da mnogi nekdanji člani nimajo več interesa za sodelovanje v društvu, se je Izvršilni odbor društva odločil, da stanje članstva uredi in vas zato prosi, da izpolnite in nam pošljete obrazec priložen na koncu revije.

Naj vas ponovno spomnimo na ugodnosti, ki izhajajo iz vašega članstva. Kot član strokovnega društva prejemate revijo »Informacije MIDEM«, povabljeni ste na strokovne konference, kjer lahko predstavite svoje raziskovalne in razvojne dosežke ali srečate stare znance in nove, povabljene predavatelje s področja, ki vas zanima. O svojih dosežkih in problemih lahko poročate v strokovni reviji, ki ima ugleden IMPACT faktor.S svojimi predlogi lahko usmerjate delovanje društva.

Vaša obveza je plačilo članarine 25 EUR na leto. Članarino lahko plačate na transakcijski račun društva pri A-banki : 051008010631192. Pri nakazilu ne pozabite navesti svojega imena!

Upamo, da vas delovanje društva še vedno zanima in da boste članstvo obnovili. Žal pa bomo morali dosedanje člane, ki članstva ne boste obnovili do konca leta 2009, brisati iz seznama članstva.

Prijavnice pošljite na naslov:

MIDEM pri MIKROIKS

Stegne 11

1521 Ljubljana

Ljubljana, marec 2009

Izvršilni odbor društva

## FAST MOS TRANSISTOR MISMATCH OPTIMIZATION – A COMPARISON BETWEEN DIFFERENT APPROACHES

Gregor Cijan<sup>1</sup>, Tadej Tuma<sup>2</sup>, Sašo Tomažič<sup>3</sup>, Árpád Bűrmen<sup>4</sup>

<sup>1</sup> Regional Development Agency of Northern Primorska, Šempeter pri Gorici, Slovenia <sup>2,3,4</sup> University of Ljubljana, Faculty of Electrical Engineering, Ljubljana, Slovenia

Key words: MOS transistor mismatch, optimization, mismatch simulation, integrated circuits

**Abstract:** In this paper two different approaches for calculating the standard deviation of circuit performance measures caused by MOS transistor mismatch are presented. The short CPU time needed for mismatch evaluation makes it possible to include the proposed approaches in a circuit optimization loop as a criterion subject to optimization. Both mismatch evaluation methods were tested on four different circuits. The optimized circuits were compared to the circuits obtained from an optimization run where the list of criteria did not include mismatch. The results show that a significant reduction of standard deviations is obtained when mismatch evaluation is included in the optimization loop.

## Hitra optimizacija neujemanja MOS tranzistorjev – primerjava različnih pristopov

Kjučne besede: neujemanje MOS tranzistorjev, optimizacija, simulacija neujemanja, integrirana vezja

Izvleček: V članku sta predstavljena dva različna pristopa za izračun standardnih deviacij lastnosti vezja, ki jih povzroča neujemanje identično načrtovanih MOS tranzistorjev. Glavna prednost opisanih pristopov je hiter izračun standardnih deviacij lastnosti vezja, ki so posledica neujemanja. To je ključnega pomena, če želimo posledice neujemanja vključiti v kriterijsko funkcijo optimizacijskega postopka. Oba pristopa sta bila preizkušena z optimizacijo štirih različnih vezij. Lastnosti tako dobljenih vezij smo primerjali z lastnostmi vezja dobljenega z optimizacijskim postopkom, ki ni vključeval učinkov neujemanja. Primerjava je pokazala, da je tovrstna vključitev neujemanja v optimizacijsko zanko smiselna, saj se standardna devicija lastnosti vezja občutno zmanjša.

### 1 Introduction

Mismatch is an effect that arises in IC fabrication and is a limiting factor of the accuracy and reliability of many analog integrated circuits. The main reason for mismatch is the stochastic nature of the fabrication process. Due to mismatch two equally designed transistors exhibit different electrical behaviour. Consequently the operating point and other circuit characteristics differ from their desired values. Mismatch can be divided into a systematic and a stochastic component. The systematic component is not considered in this paper because it can be reduced to great extend with proper layout /1/, /2/. The stochastic component is caused by random microscopic device architecture fluctuations. It can be reduced with better process control and larger transistor areas /3/, /4/. Most often the Gaussian distribution is used for modelling the stochastic variations of model parameters. The amount of mismatch can be expressed with standard deviation ( $\sigma$ ) of transistor model parameters.

Mismatch can be modelled in many different ways /3/-/6/. Because of the limited availability of mismatch model parameters only some of them can be used for general purpose. One of the simplest models is the Pelgrom model (1) /3/.

$$\sigma(\Delta P) = \frac{A_P}{\sqrt{WL}} \tag{1}$$

In this model the standard deviation ( $\sigma$ ) of the parameter difference ( $\Delta P$ ) between two identically drawn transistors

depends on parameter  $A_P$  (which in turn is technology-dependent) and effective channel dimensions W and L. In the optimization runs presented in this paper we used (1) because it is simple and the technology-dependent parameters are available in the literature /7/. In /8/ it is shown that the model (1) is suitable for the  $0.18\mu m$  technology. Due to the limited availability of mismatch parameters, this model is still frequently used for mismatch evaluation. In this paper two different methods of mismatch simulation are presented and tested on four different circuits.

Most commonly used transistor parameters in mismatch modelling (mismatch parameters) are threshold voltage ( $V_T$ ) and current factor ( $\beta$ ). The standard deviation of  $V_T$  and  $\beta$  can be expressed as

$$\sigma\left(\Delta V_T\right) = \frac{A_{V_T}}{\sqrt{WL}} \tag{2}$$

$$\sigma\left(\frac{\Delta\beta}{\beta}\right) = \frac{A_{\beta}}{\sqrt{WL}} \tag{3}$$

The technology dependant parameters  $A_{Vt}$  and  $A_{\beta}$  for different types of technologies are available in /7/.

### 2 Mismatch optimization

A robust circuit exhibits adequate performance in all corners. A corner defines a group of different process variations. The performance of the circuit is expressed with the cost function which is a sum of penalties /9/. Each measure has a goal and if the measured value deviates from this

goal, a penalty which is proportional to the violation, is added to the cost function. The goal is to minimize the cost function taking into account all corners. For this purpose the Constrained simplex /9/ optimization method has been used, which performs remarkably well on circuit optimization problems /10/.

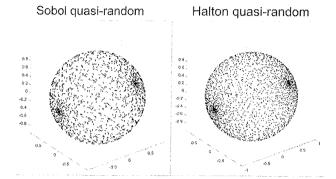

To include mismatch in the optimization as yet another criterion, it has to be simulated first. The goal of mismatch simulation is to obtain a standard deviation of circuit properties caused by the stochastic nature of transistor model parameters. This standard deviation can be included in the cost function. In this paper two different approaches for mismatch simulation are presented. The first one is the sensitivity-based approach and the second one is the minmax approach. In both approaches a design of an operational amplifier will be used for better understanding. Consider an operational amplifier where a designer is interested in the standard deviation of the output voltage caused by the stochastic nature of the transistor model parameters. Beside the offset voltage performance measures like swing at gain, bandwidth, phase margin, etc. are also important in the design process. All these performance measures are circuit properties but only offset voltage is relevant for mismatch analysis.

### 2.1 Sensitivity-based approach

The sensitivity-based approach assumes that mismatch parameters are not correlated and that the changes caused by the stochastic nature of model parameters are within the bounds where the circuit behaves linearly. The evaluation of the standard deviations of the circuit properties can be divided in three major steps:

- Step 1: Calculate the standard deviation of every relevant transistor parameter (mismatch parameter).

- Step 2: Calculate the sensitivity of circuit properties to all mismatch parameters.

- Step 3: Calculate the approximated standard deviation of the circuit property.

In a circuit composed of k MOS transistors only  $n \le k$  MOS transistors are relevant to the mismatch analysis.  $m = 2 \cdot n$  standard deviations must be calculated (n standard deviations for the threshold voltages and n standard deviation for the current factors). The remains  $k \cdot n$  MOS transistors belong usually to the start up circuit or power down control.

In step 2 the sensitivity ( $\alpha$ ) of a circuit property  $P_X$  (in our example this is the output offset voltage) to every mismatch parameter is calculated. The sensitivity indicates how much the variation of a mismatch parameter affects circuit property  $P_X$ . The sensitivity is calculated using the perturbation approach (4)

$$\alpha_i = \frac{P_X(\delta_i) - P_X(0)}{\delta_i} \qquad i = 1, ..., m$$

(4)

Where  $P_x(0)$  is the value of the circuit property when all mismatch parameters are set to their nominal values while

the  $P_x(\delta_i)$  is the value of the circuit property when one mismatch parameter is perturbed. The perturbed value (for example  $V_T$ ) is the sum of the nominal value and one standard deviation ( $\delta_i = V_T + \sigma(\Delta V_T)$ ) of the respective mismatch parameter.

Assuming that mismatch parameters are uncorrelated the standard deviation of a circuit property can be expressed as:

$$\sigma^{2}(P_{X}) = \sum_{i=1}^{m} \alpha_{i}^{2} \cdot \sigma_{i}^{2}$$

(5)

The sensitivity-based approach requires m+1 circuit simulations to calculate the sensitivities. One simulation is needed for the nominal mismatch parameter values and m simulations are needed for the perturbed circuits.

### 2.2 Min-Max approach

With this approach we estimate the extreme value of a circuit property P. We assume P has an extreme when all mismatch parameters are at their extreme values. This is true if P is a monotonic function of the mismatch parameters. Which extreme value  $(+\sigma \text{ or } -\sigma)$  a mismatch parameter should take in order for P to take its extreme value depend on the sensitivity. Just like with the sensitivity-based approach we assume that mismatch parameters are not correlated. Once the upper (max) and lower (min) extreme of P are obtained, the upper bound on the standard deviation of the circuit property can be calculated. The min-max approach can be divided in 4 steps.

- Step 1: Calculate the standard deviation of every mismatch parameter.

- Step 2: Obtain the signs of the sensitivities to all mismatch parameters.

- Step 3: Measure the extreme (min and max) values.

- Step 4: Calculate the upper bound on the standard deviation.

Step 1 and step 2 are very similar to the corresponding steps in the sensitivity-based approach. To obtain the signs of the sensitivities m+1 simulations are necessary (m is the number of mismatch parameters). In step 3 the extreme values of the circuit properties are calculated. This is done using two simulations per circuit property (one for the upper and one for the lower extreme). To measure the upper extreme ( $P_{max}$ ) we increase (or decrease) the value of every mismatch parameter by one standard deviation if the sensitivity is positive (if the sensitivity is negative). The same is done for the lower extreme ( $P_{min}$ ), except that the reasoning is opposite. For positive sensitivity the value of the mismatch parameter is decreased and for negative sensitivity it is increased. In step 4 the upper bound on the standard deviation can now be calculated (6).

$$\sigma(P_X) \le M_{\sigma}(P_X) = \left| \frac{P_{\text{max}} - P_{\text{min}}}{2} \right| \tag{6}$$

### 3 Examples

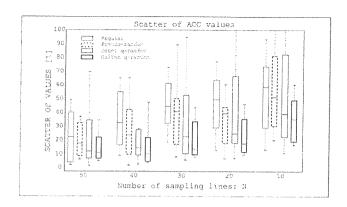

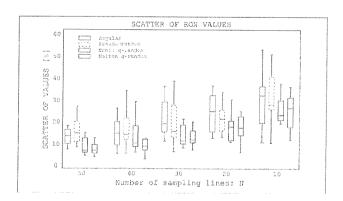

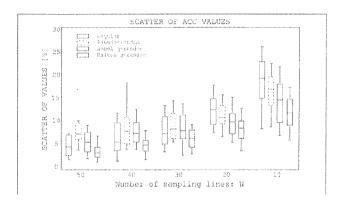

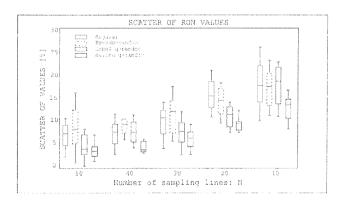

The proposed approaches for mismatch evaluation were included in the optimization loop and the obtained results were compared with the results of the optimization run without mismatch evaluation. The comparison was done on four different circuits:

- Bandgap reference circuit (BGR)

- Operational amplifier (OPA)

- Beta multiplier reference circuit (BMR)

- Comparator (COMP)

The first optimization run (A) considers only performance measures, while the second and the third run (B, C) include mismatch. In the second run (B) the sensitivity-based approach is used for evaluating the mismatch and in the third run (C) the min-max approach is used. All circuits in this paper have been simulated using the SPICE OPUS simulator and the BSIM3 model of a 0,18  $\mu m$  process technology. To obtain robust circuits every circuit has been simulated in three different corners. Every corner was described with the corresponding temperature, supply voltage, MOS transconductance, etc.

### 3.1 Bandgap reference (BGR)

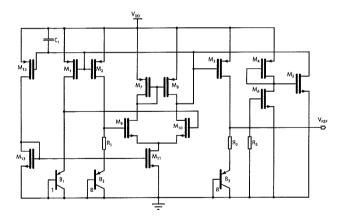

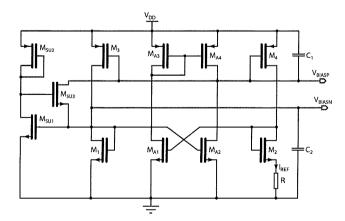

A stable voltage reference is very important in many circuits. A bandgap voltage reference (BGR) is capable of providing a voltage almost independent of temperature and supply voltage fluctuations. In this paper we optimized a 1-V low power CMOS bandgap reference based on resistive subdivision (Figure 1) which is in detail described in /11/.

Fig 1: Bandgap voltage reference (BGR)

It is known that sample to sample variations (mismatch) are larger than the variations caused by the temperature or supply voltage fluctuation. Therefore mismatch is a dominating factor determining the absolute accuracy of the bandgap reference circuit /11/.

The optimization parameters were the three resistances  $(R_1-R_3)$  and the channel dimensions (width and length) of all MOS transistor except transistors  $M_4-M_6$  which constitute the start up circuit. The list of performance measures

and parameters was the same for all of the three optimization runs. The cost function was composed of the following performance measures:

- output voltage change when the temperature varies from -20°C to 50°C,

- output voltage change when the supply voltage varies from 1V to 1,6V,

- circuit area.

- standard deviation of the output voltage caused by mismatch.

Table 1 lists the results of the optimization. The first and the second column contains the names and the desired values of the performance measures while the others list the results of optimization runs A, B and C. The standard deviation  $\sigma$  ( $V_{REF}$ ) is calculated from 1000 Monte Carlo simulations.

Table 1: Comparison of three different optimization runs (BGR-circuit)

|       |                                                      | Desired | Optimization processes |       | esses |

|-------|------------------------------------------------------|---------|------------------------|-------|-------|

|       |                                                      | value   | BGR-A                  | BGR-B | BGR-C |

| Meas. | Max (dV <sub>REF</sub> /dV <sub>DD</sub> )<br>[mV/V] | < 4     | 1,80                   | 3,04  | 3,39  |

| Z     | Max (dV <sub>REF</sub> /dT) [mV/°]                   | < 0,15  | 0,15                   | 0,15  | 0,14  |

| Perf. | Area [µm²]                                           | < 6000  | 3521                   | 5996  | 5985  |

| ٩     | σ (V <sub>REF</sub> ) [mV]                           | < 7     | 16,2                   | 7,05  | 6,67  |

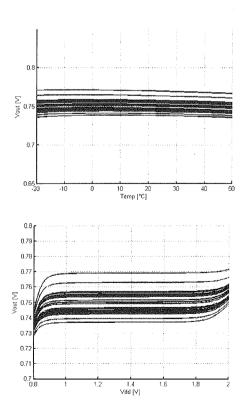

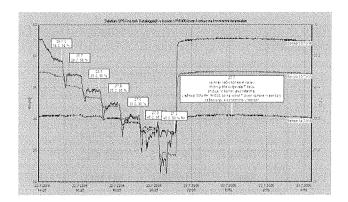

It can clearly be seen that including mismatch effects in the cost function results in the enlargement of the transistors area and the reduction of the reference voltage variation caused by mismatch. The maximal reference voltage slope with respect to the supply voltage increases, while the maximal slope with respects to the temperature remains almost unchanged. Despite the large reduction of the standard deviation (more than 2 times) all the results are still within the specified bounds. Figure 2 shows 30 Monte Carlo simulations of the circuit obtained from run A where mismatch was neglected. If we compare this figure to figure 3 where the results of run B are plotted the reduction of the standard deviation is clearly visible.

### 3.2 Operational amplifier (OPA)

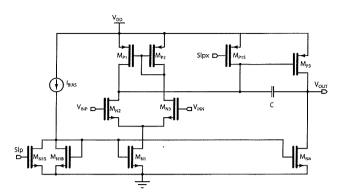

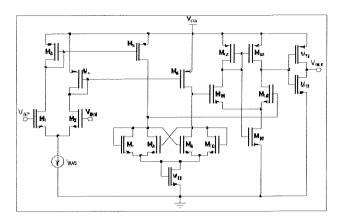

The operational amplifier is one of the fundamental building blocks of analog integrated circuits. Due to mismatch an operational amplifier exhibits a random offset voltage. In this paper the operational amplifier from figure 4 was optimized.

The optimization parameters were the capacitance of the capacitor and the channel dimensions (width and length) of all transistors except  $M_{\text{N1S}}$  and  $M_{\text{P1S}}$ , which are used for shutting down the amplifier. All performance measures and their goals (desired value) are listed in table 2. The standard deviation  $\sigma(V_{\text{OUT}})$  is calculated from 1000 Monte-Carlo simulations.

Fig 2: Variation of the BGR output voltage with respect to the temperature and the supply voltage when mismatch is not included in the optimization loop (30 samples).

Fig 3: Variation of the BGR output voltage with respect to the temperature and the supply voltage when mismatch is included in the optimization loop (30 samples).

Fig 4: Operational amplifer (OPA)

Table 2: Comparison of three different optimization runs (OPA-circuit)

|          |                            | Desired | Optimization processes |       | cesses |

|----------|----------------------------|---------|------------------------|-------|--------|

|          |                            | value   | OPA-A                  | OPA-B | OPA-C  |

| Si       | Swing at gain [V]          | > 2     | 2,58                   | 2,24  | 2,18   |

| measures | Phase margin [°]           | > 45    | 61,8                   | 65,7  | 67,2   |

| eas      | Unity gain b.w. [MHz]      | >18     | 32,7                   | 20,3  | 43,1   |

|          | Gain [dB]                  | > 70    | 72,1                   | 83,5  | 85,3   |

| Perf.    | Area [µm²]                 | < 250   | 233,8                  | 249,7 | 249,8  |

| Ы        | σ (V <sub>ουτ</sub> ) [mV] | < 1,8   | 4,44                   | 1,87  | 1,70   |

The results of the three optimization runs are listed in table 2. We can see that for the circuit obtained from the first run (without mismatch) the output voltage has a standard deviation of 4,44 mV (offset). Both optimization runs that included mismatch produced better results. In runs B and C the standard deviation of the output voltage was reduced by a factor of 2,3 or more. Most of the remaining performance measures stayed within the desired range.

### 3.3 Beta-multiplier reference (BMR)

The Beta-multiplier circuit is used for providing a stable and temperature independent current reference for a whole range of circuits like operational amplifiers, comparators, etc. It can also be used as a voltage reference circuit.

Fig 5: Beta multiplier reference (BMR)

The circuit in figure 5 can provide a stable current ( $I_{REF}$ ) that flows through resistance R. This current is fairly stable with respect to temperature and supply voltage variations.

One can mirror the reference current using gate voltages  $V_{BIASP}$  and  $V_{BIASN}$ . The optimization goals were to minimize the variation of the current caused by the change of temperature and supply voltage. The optimization parameters were the resistance R and channel dimensions of all transistors except transistors that constitute the start up circuit ( $M_{SU1}$ ,  $M_{SU2}$ ,  $M_{SU3}$ ). The results of the three optimization runs are listed in table 3. The standard deviation  $\sigma$  ( $I_{REF}$ ) is calculated from 1000 Monte Carlo simulations.

Table 3: Comparison of three different optimization runs (BMR-circuit)

|          |                                                    | Desired | Optimi | zation pro | cesses |

|----------|----------------------------------------------------|---------|--------|------------|--------|

|          |                                                    | value   | BMR-A  | BMR-B      | BMR-C  |

|          | Max (dl <sub>REG</sub> /dV <sub>DD</sub> ) [μΑ /V] | < 0,4   | 0,31   | 0,30       | 0,49   |

| Meas     | Max (dl <sub>REG</sub> /dT) [µA /°]                | < 0,06  | 0,047  | 0,053      | 0,060  |

|          | I <sub>REG</sub> [µA]                              | = 20    | 19,9   | 20,0       | 20,0   |

| Perf     | Area [µm²]                                         | < 500   | 490    | 497        | 513    |

| <u> </u> | σ (I <sub>REG</sub> ) [μΑ]                         | < 1     | 3,45   | 0,99       | 0,53   |

The first two performance measures (dI<sub>REG</sub>/dV<sub>DD</sub> and dI-REG/dT) provide the information on the output current maximum variation with respect to the supply voltage and temperature variations. The third measure is the value of the reference current while the last two are the circuit area and the standard deviation of the reference current caused by mismatch. From table 3 it can clearly be seen that the standard deviation ( $\sigma(I_{REG})$ ) from runs B and C (where mismatch was included in the cost function) is more than 3 times smaller than the one obtained in run A. All the design requirements are fulfilled except the area in run C where a small goal violation occurs. The standard deviation obtained in run C is nearly two times smaller then the goal. The reason is that min-max approach calculates the maximum value of the standard deviation, which is in this example 2 to 3 times bigger than the real standard deviation (see table 5). Due to this the weight of this performance measure is effectively bigger than the weight of the circuit area.

### 3.4 Comparator (COMP)

The comparator from Figure 6 is a decision-making circuit. The output voltage ( $V_{\text{out}}$ ) switches from 0V to  $V_{dd}$  when  $V_{INP}$  is greater than  $V_{INN}$ . The output switches back to 0V when  $V_{INP}$  becomes smaller than  $V_{INN}$ . The output does not switch instantly when the difference  $V_{INP}$ - $V_{INN}$  changes sign meaning that there is some hysteresis present in the circuit. Mismatch causes that the width of the hysteresis to vary randomly. The optimization run which includes mismatch attempts to remove the variation of hysteresis.

The optimization parameters were the channel dimensions of all transistors. The results of the optimization runs are listed in table 4.

The first performance measure (Delay time LH) measures the time form the moment when  $V_{INP}$  crosses  $V_{INN}$  and the moment when  $V_{OUT}$  reaches 90% of the difference between the initial and the final value. The second measure (Delay time HL) is the same as previous with the difference that

Fig 6: Comparator (COMP)

Table 4: Comparison of three different optimization runs (COMP-circuit)

|          |                             | Desired | d Optimization processes |        |        |

|----------|-----------------------------|---------|--------------------------|--------|--------|

|          |                             | value   | COMP-A                   | COMP-B | COMP-C |

|          | Delay time LH [ns]          | < 5     | 3,68                     | 4,94   | 5,80   |

|          | Delay time HL [ns]          | < 5     | 3,87                     | 3,38   | 4,66   |

|          | Rise time [ns]              | < 0,3   | 0,17                     | 0,13   | 0,11   |

| l e      | Fall time [ns]              | < 0,3   | 0,18                     | 0,18   | 0,26   |

| measures | Hysteresis [mV]             | < 1     | 0,83                     | 0,56   | 1,95   |

| ĕ        | Positive slope [mV]         | < 1     | 0,93                     | 0,46   | 0,40   |

|          | Negative slope [mV]         | < 1     | 0,51                     | 0,46   | 0,40   |

| Perf.    | Overshoot [mV]              | < 50    | 13,7                     | 6,18   | 8,26   |

|          | Undershoot [mV]             | < 50    | 6,63                     | 8,52   | 4,18   |

|          | Area [µm ]                  | < 90    | 85,4                     | 89,5   | 88,1   |

| <u> </u> | σ (V <sub>HIST</sub> ) [mV] | < 5     | 10,2                     | 5,29   | 4,50   |

the falling edge of  $V_{OUT}$  is measured (when  $V_{OUT}$  reaches 10% of the difference between the initial and final value). The rise time is the time needed for the output to rise from 10% to 90% of the difference and the fall time is measured between the points where the output crosses the 90% and 10% level of the difference. The fifth measure is the width of the hysteresis, while the last two measures provide the slope of the hysteresis. From the results it can be seen that almost all the design requirements are fulfilled and that the standard deviation of the hysteresis is reduced to half if mismatch is considered in the optimization run.

### 3.5 Comparison of the approaches for mismatch evaluation

In table 5 the standard deviations of the circuit properties affected by mismatch are listed for all four circuits. For every circuit the computational effort of the mismatch evaluation has been calculated for all three methods: Monte-Carlo, sensitivity-based approach and min-max approach.

Table 5 shows that the mismatch effect calculated with the sensitivity-based approach is close to the value obtained from 1000 Monte Carlo simulations. The min-max approach overestimates the mismatch. This can also be seen from table 5. Typically the min-max approach results in 2 to 4 times larger values than Monte-Carlo analysis. The main difference between the two presented approaches and Monte-Carlo approach is the number of simulations need-

Table 5: Comparison between of different approaches for mismatch evaluation

|             | Monte Carlo<br>Approach | Sensitivity-Based<br>Approach | Min-Max<br>Approach |

|-------------|-------------------------|-------------------------------|---------------------|

| BGR-A [mV]  | 16,2                    | 16,3                          | 43,6                |

| BGR-B [mV]  | 7,05                    | 7,04                          | 19,3                |

| BGR-C [mV]  | 6,67                    | 6,71                          | 17,5                |

| OPA-A [mV]  | 4,45                    | 4,40                          | 9,59                |

| OPA-B [mV]  | 1,87                    | 1,87                          | 4,49                |

| OPA-C [mV]  | 1,70                    | 1,71                          | 4,03                |

| BMR-A [µA]  | 3,45                    | 3,39                          | 7,53                |

| BMR-B [µA]  | 0,99                    | 0,99                          | 2,71                |

| BMR-C [µA]  | 0,53                    | 0,52                          | 1,64                |

| COMP-A [mV] | 10,2                    | 9,59                          | 34,8                |

| COMP-B [mV] | 5,29                    | 4,99                          | 19,9                |

| COMP-C [mV] | 4,50                    | 5,57                          | 12,5                |

ed to evaluate the standard deviation of a circuit property. To obtain the actual value of the standard deviation of a circuit property 1000 or more Monte-Carlo simulations are needed. The sensitivity-based approach is significantly faster since it needs only m+1 simulations (where m is the number of mismatch parameters) to obtain similar values as Monte-Carlo approach. The min-max approach also gives satisfying results with only m+3 simulations.

### 4 Conclusion

With the reduction of transistor dimensions the mismatch is becoming the dominating factor of the accuracy of many analog circuits. In the examples it was shown how mismatch can be included in circuit optimization. Two different ways of mismatch evaluation were presented. The sensitivity-based approach returns more realistic values while on the other hand the min-max approach results in the upper (lower) bound of a circuit performance measures. Optimization runs using these two methods have been conducted on four different circuits and the results were compared to the results of an optimization run where mismatch was neglected. The comparison shows that significant improvements of circuit performance can be achieved. Both optimization runs where mismatch was included resulted in circuits that exhibited similar performance.

### 5 Acknowledgment

The research has been supported by the Ministry of Higher Education, Science and Technology of Republic of Slovenia within programme P2-0246 – Algorithms and optimization methods in telecommunications.

### 6 References

/1/ M.F. Lan, A. Tammineedi, R. Geiger, Current mirror layout strategies for enhancing matching performance, Analog Integrated Circuits and Signal Processing, vol. 28, pp. 9-26, 2001

- /2/ C. He, X. Dai, H. Xing, D. Chen, New layout strategies with improved matching performance, Analog Integrated Circuits and Signal Processing, vol. 49, pp. 281-289, 2006

- /3/ M.J.M. Pelgrom, A.C.J. Duinmaijer, A.P.G. Welbers, Matching properties of MOS transistors, IEEE Journal of Solid-State Circuits, vol. 24, pp. 1433-1439, 1989

- /4/ J. Bastos, M. Steyaert, A. Pergoot, W. Sensen, Mismatch characterization of submicron MOS transistors, Analog Integrated Circuits and Signal Processing, vol. 12, pp. 95-106, 1997

- /5/ M. Conti, P. Crippa, S. Orcioni, C. Turchetti, Parametric yield formulation of MOS IC's affected by mismatch effect, IEEE Transaction on Computer-Aided Design of Integrated Circuits and systems, vol. 18, pp. 582-596, 1999

- /6/ U. Grünebaum, J. Oehm, K. Schumacher, Mismatch modelling and simulation – a comprehensive approach, Analog Integrated Circuits and Signal Processing, vol. 29, pp. 165-171, 2001

- /7/ Peter R. Kinget., Device mismatch and tradeoffs in the design of analog circuits, IEEE Journal of Solid-State Circuits, vol. 40, pp. 1212-1224, 2005

- /8/ R. Difrenza, P. Llinares, G. Ghibaudo, The impact of short channel and quantum effects on the MOS transistor mismatch, Solid-State Electronics, vol. 47, pp. 1161-1165, 1997

- /9/ A. Buermen, D. Strle, F. Bratkovic, J. Puhan, I. Fajfar, T. Tuma, Automated robust design and optimization of integrated circuit by means of penalty functions, Aeu-International Journal of Electronics and Comunications, vol. 57, pp. 47 - 56, 2003

- /10/ J. Puhan, T. Tuma, I. Fajfar, Optimization methods in SPICE: a comparison, ECCTD '99: proceedings, eds. C. Beccarti et. al. (Stresa, Italy, 1999), pp. 1279-1282.

- /11/ K. Lasanen, V. Korkala, E. Räisänen-Ruotsalainen, J. Kostamovaara, Design of a 1-V low power bandgap reference based on resistive subdivision, Circuit and Systems, vol. 3, pp. 564 567, 2002

Gregor Cijan RRA severne Primorske d.o.o. Nova Gorica Mednarodni prehod 6, SI-5290 Šempeter pri Gorici E-mail: gregor.cijan@rra-sp.si Telefon: (01) 4768 322

izr. prof. dr. Tadej Tuma Univerza v Ljubljani, Fakulteta za elektrotehniko Tržaška 25, SI-1000 Ljubljana E-mail: tadej.tuma@fe.uni-lj.si Telefon: (01) 4768 329

prof. dr. Sašo Tomažič Univerza v Ljubljani, Fakulteta za elektrotehniko Tržaška 25, SI-1000 Ljubljana E-mail: saso.tomazic@fe.uni-lj.si Telefon: (01) 4768 432

doc. dr. Árpád Bűrmen Univerza v Ljubljani, Fakulteta za elektrotehniko Tržaška 25, SI-1000 Ljubljana E-mail: arpadb@fides.fe.uni-lj.si Telefon: (01) 4768 322

Prispelo (Arrived): 27.11.2007 Sprejeto (Accepted): 19.03.2009

## SMD FILM CAPACITORS FOR INTEGRATING A/D CONVERTERS

Andrej Levstek, Matija Pirc

### Faculty of Electrical Engineering, University of Ljubljana, Ljubljana, Slovenia

Key words: integrating A/D converter, SMD film capacitor, dielectric absorption, humidity, surface resistance, polymer dielectric

Abstract: Lead free technology has significantly influenced the choice of commercially available capacitors, especially those intended for surface mount. A case study of the appropriate SMD capacitor selection for a high accuracy integrating A/D converter is presented. The converter is part of a smart sensor that encompasses a simple microcontroller and an analog transducer, which is in this case a platinum resistor. An overview of traditional and new polymer dielectric materials is given with the emphasis on the commercial selection of SMD capacitors. Trends of the film capacitor industry in the recent years are explained through the physical properties of the materials used and the imposed legislative restrictions. The often overlooked pitfalls of capacitor selection are sequentially described. The effect of the dielectric absorption of the charge on the conversion error is theoretically analyzed for the intermittent mode of operation. Inaccuracy due to the recovery of the absorbed charge is eliminated by the use of a polyphenylene sulfide (PPS) film capacitor; however, at high humidity some capacitive sensors exhibit abnormal deviations.

Based on some additional experiments, we determine the influence of the capacitor's parallel resistance on the conversion result. The synergic impact of high humidity and temperatures, and flux residues on the surface resistance of stacked capacitors is proven by experimental measurements carried out in a climatic chamber. The experimental measurements of SMD capacitor insulation resistance show that naked stacked capacitor construction is not suitable for a relative humidity above 80%. In such cases, slightly larger encapsulated SMD capacitors must be used to maintain the desired high accuracy.

### SMD filmski kondenzatorji za integracijske A/D pretvornike

Kjučne besede: integracijski A/D pretvornik, folijski SMD kondenzator, dielektrična absorpcija, površinska upornost, polimerni dielektrik

Izvleček: Prepoved uporabe svinca v tehnologiji izdelave tiskanih vezij je pomembno vplivala na tržno ponudbo kondenzatorjev, namenjenih za površinsko montažo. V prispevku je podan potek izbire ustreznega kondenzatorja za integracijski A/D pretvornik z visoko ločljivostjo. Sam D/A pretvornik je del inteligentnega senzorja, ki ga sestavlja mikrokrmilnik in ustrezen analogni merilni pretvornik, v opisanem primeru je to platinski upor. V delu je najprej podan pregled polimernih dielektrikov s poudarkom na njihovi rabi za SMD komponente. Trendi zadnjih let v industriji kondenzatorjev za elektroniko, so opisani s stališča fizikalnih lastnosti dielektričnih filmov in prepovedi rabe svinca v elektronskih napravah. Spregledane pomanjkljivosti izbranega tipa, so podane zaporedno, kot so se pojavljale pri razvoju. Izpeljali smo analitično zvezo med dielektrično absorpcijo kondenzatorja in pogreškom posamične pretvorbe. Merilno napako zaradi sproščanja absorbiranega naboja v času pretvorbe, smo odpravili z uporabo polifenil sulfidnega (PPS) kondenzatorja.

Z eksperimenti v klimatski komori smo ugotovili, da imajo nekatera vezja nenormalno velika odstopanja, ki nastanejo zaradi vpliva vlage na gole PPS kondenzatorje. Izpeljali smo analitično zvezo med velikostjo skupne upornosti med sponkama kondenzatorja in merilno napako. Ugotovili smo sinergični vpliv vlage, temperature in ostankov fluksa na površinsko upornost nezaščitenih kondenzatorjev, ki so izdelani z zlaganjem metaliziranega filma. Meritve izolacijske upornosti so pokazale, da takšni kondenzatorji niso primerni za vlažnosti zraka nad 80 %. Za precizni integrator so primernejši dimenzijsko nekoliko večji SMD kondenzatorji v plastičnem ohišju.

### 1. Introduction

Electronic integrators offer a simple solution for achieving an accurate A/D conversion of low voltage levels whenever the speed of conversion doesn't play a significant role. Dual slope integrating A/D converters can be implemented by low cost digital microcontroller and a simple additional analog circuit. Such A/D converters can be used for accurate conversion voltages that are proportional to slowly varying physical quantities like temperature or atmospheric humidity.

Conversion errors due to the non-idealities of the analog components, i.e., the input offset voltage of the operational amplifier (opamp), are minimized by a simple solution, so that low-cost analog components can be used. The choice of utilized capacitor seems unimportant since the value of capacitance does not appear in the conversion equations at all /1/. Such an approach is over-simplified but this fact does not become obvious until experi-

mental measurements of prototypes under various climatic conditions are performed. The physical dimensions of electronic circuits are steadily decreasing, which is a consequence of the growing demand for hand-held devices. The introduction of surface-mount technology (SMT), which became widely used around the year 1990, engendered important changes in the field of high performance metallized film capacitors. The small size of SMD capacitors has raised many problems in their construction, because of the intense heat transfer from the metallized soldering pads to the plastic dielectric film during the reflow soldering process.

The first widely used SMD capacitors were multilayer ceramic chips (MLCC). This construction and the high relative dielectric constant of the ceramics result in such capacitors having a high capacitance packing density and relatively low equivalent serial resistance (ESR). The inorganic nature of the dielectric used in MLCCs minimizes the impact of the thermal stress during soldering. Polymer

film capacitors are much more affected by the raised temperature levels because of the thermoplastic nature of the dielectric film. The choice of SMD polymer film capacitors on the electronic components market is predominated by trough-hole film types and by ceramic SMD chips. As a consequence, film capacitors are rather expensive, therefore cheaper alternatives are used wherever it is possible.

In the next chapter an overview of the important polymer dielectric materials is given, followed by a case study of the capacitor selection for an integrating A/D converter. Finally, the results of practical experiments are presented. The comments on the outcomes and some practical hints for the selection of appropriate SMD polymer film capacitors conclude the paper.

### 2. Materials for film capacitors

The traditionally used plastic materials for dielectric films in capacitors are polystyrene (PS), polyester (PE), polycarbonate (PC) and polypropylene (PP). These materials are used for film capacitors with low loss and stable capacitance in the range from 1 nF up to 10  $\mu\text{F}$ . Film capacitors below 1 nF are offered only by a small number of producers; and especially SMD types are very rare. The range of capacitances below 100 pF is almost exclusively covered by C0G ceramic capacitors (Table 2), which are featured with a low capacitance temperature coefficient  $\alpha_{C}$  and the dissipation factor  $\tan\delta$ .

### 2.1 Polystyrene capacitors

For years, polystyrene (PS) capacitors were the best choice for critical analog applications. In the middle of the 1990s the production of PS capacitors slowly ceased. There were several reasons that caused polystyrene capacitors to disappear from production. The maximal operating temperature of PS film and capacitors is very low, only 85°C (see Table 1). Additionally, the low heat resistance of PS film allows neither the construction of SMD components nor the vacuum-deposition of aluminum, hence only film/foil capacitors were (are) produced. This construction lacks the self-healing capability, i.e., the ability to clear faults (such as pores or impurities in the film) under the influence of voltage. Although PS capacitors have low absorption of moisture, they can be easily damaged by printed board cleaning solvents. PS capacitors that are still available from old stocks are not intended for new designs. New materials like polyphenylene sulfide (PPS) should be used instead of PS.

#### 2.2 Polycarbonate capacitors

Polycarbonate (PC) metallized film and film/foil capacitors were traditionally the logical choice for high performance applications for operation at elevated temperatures. This material is featured with a negligible temperature coefficient  $\alpha_{\rm C}$  for temperatures in the range of 20°C  $\div$  40°C, which is the common operating temperature range of pre-

cision electronic equipment. In spite of the higher operating temperatures of this film, commercially available PC capacitors for surface mount were never produced. In the year 2000, the major producer of PC capacitors WIMA from Germany /2/, ceased their production after finding it unprofitable. This decision caused the major producer of capacitor grade PC film, Bayer AG, to stop its production upon completion of the final order. Nevertheless, PC film capacitors are still available and produced at least by Electronic Concepts Inc. form USA with its own in-house produced dielectric film /3/. Polycarbonate film is almost the perfect material for high performance capacitors but is very sensitive to moisture absorption, thus good encapsulation is required to protect the dielectric film against humidity. Hermetically sealed PC capacitors are available only with wired trough-hole terminals and are primarily intended for military applications.

### 2.3 Polyester capacitors

Polyester films have become the standard dielectric for capacitors in electronic applications. Polyester film for capacitors is biaxially oriented polyethylene terephthalate (PET) developed by DuPont in the mid-1950s and is well-known under the trade name Mylar. This material has good mechanical and electrical properties for temperatures in the range from -55°C to +125°C. Their high dielectric strength, and the highest dielectric constant among commercially used dielectric films, make PET capacitors cheap and volume-effective. Metallized PET film capacitors are produced in any combination of the construction alternatives given in Table 1.

Table 1: Manufacturing and construction alternatives of PET capacitors

| Parameter                | Alternative |             |  |

|--------------------------|-------------|-------------|--|

| Environmental protection | Naked       | Protected   |  |

| Mounting terminals       | SMD         | Trough hole |  |

| Construction             | Stacked     | Wound       |  |

| RoHS compliance          | Yes         | No          |  |

These capacitors are the most frequently used type of plastic film capacitors in electronic circuits – primarily for DC or low frequency purposes – because the dissipation factor  $\tan\delta$  of polyester is the highest among contemporary film materials. Even though it is not a high quality material, in many respects, PET films perform much better than multilayer ceramic capacitors (MLCC) using X7R or Z5U dielectric ceramics. Some producers, e.g., AVX /4/, offer PET-HT capacitors with an improved temperature range of up to +125°C with a nominal voltage derating factor of 1.25 %/°C above  $T_R$  = 105°C, which represents an increase of 20°C with respect to the standard types.

### 2.4 Polypropylene capacitors

Polypropylene (PP) film has, for many years, been used for high performance applications, especially for medium and high power electronic circuits where high impulse current capability is required. This material has very low dielectric absorption DA making a PP capacitor the best choice for the charge-storing device in precision integrators, sample and hold amplifiers and other electronic circuits that retain analog signals in the form of electric charge. Additionally, PP capacitors are characterized by a constant temperature coefficient  $\alpha_{\rm C}$  = -200 ppm/°C and the second highest volume resistivity among dielectric film materials (Table 2). The main deficiency of PP is its somewhat limited temperature range, which prevents the construction of PP as an SMD component. Standard PP capacitors use metallized film and film/metal foil construction for self-healing and high impulse current capability, respectively.

### 2.5 Polyphenylene sulfide capacitors

Polyphenylene sulfide (PPS), a dielectric material with excellent electrical and thermal properties, was invented by Toray/Japan. This chemical company started the production of capacitor grade PPS film in 1988 under the trade name of Torelina®, and is still the only producer. In the same year PPS capacitors were made commercially available by WIMA/Germany, but their production was plagued with many difficulties. In 2001 WIMA /2/ temporarily ceased their production due to problems connected with inconsistent film quality and availability. A detailed examination of self-healing of different metallized polymer films by Walgenwitz et. al. /5/ has shown only insignificant distinctions among PET, PEN and PPS. In any case, achieving self-healing in PPS film is not a particular problem. The problematic availability of PC capacitors, the European Council Directive on the Restriction of Hazardous Substances (RoHS Directive, 2002/95/EC) /6/, and good the mechanical properties of biaxially oriented PPS film at higher temperatures have prompted numerous activities for the reliable production of PPS capacitors. The construction of SMD film capacitors has become very demanding due to the elevated melting point of leadless soldering compounds. After the break in 2000 WIMA restored the production of PPS capacitors, encouraged by a mixture of technological and commercial factors. After 2001 both trough hole and SMD types of PPS metallized capacitors were made generally available by several manufacturers.

PPS has excellent electrical properties that exceed PC in many aspects. Almost no sensitivity to humidity and a far higher operating temperature range are the most important attributes of PPS when compared to PC. Despite the advantages of PPS film (expressed by the figures in Table 2), this material has two shortcomings. Firstly, it is expensive and secondly, it is produced only by Toray/Japan, which may cause hitches in its supply.

### 2.6 Polyethylene naphtalate capacitors

Polyethylene naphtalate (PEN) was not used for film capacitors until 2000. The RoHS directive adopted by the EC in 2003 caused producers of electronic components to utilize substitutes for the existing materials as these could not stand the thermal stress generated by elevated soldering temperatures without significant degradation. The electrical properties of PEN film are very similar to those of PET, but the overall performance of PEN is inferior - provided that the maximum operating temperature is not taken into account /7/. PEN capacitors are larger than the corresponding PET types because the dielectric constant  $\varepsilon_r$  and the dielectric strength  $E_B$  of PEN are lower. The ratio of PEN capacitor size to the corresponding PET capacitor is between 1.5 and 2. PEN film SMD capacitors are in compliance with the RoHS directive, and are suitable for IR or vapor phase reflow processes. PEN capacitors are

Table 2: Properties of capacitor dielectric materials

| Parameter                                        | Unit             | nit              |                  |                  | Dielectric       |                  |                  |                  |                  |                  |

|--------------------------------------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| Farameter                                        | Offic            | PS               | РС               | PET              | PEN              | PP               | PPS              | PTFE             | C0G              | X7R              |

| Dielectric constant ε <sub>r</sub>               |                  | 2.2              | 2.9              | 3.3              | 3.0              | 2.2              | 3.0              | 2.0              | 1240             | 7002000          |

| Dielectric strength                              | V/μm             | 100              | 200              | 400              | 300              | 600              | 250              | 150              | 200              |                  |

| C temperature coefficient $\alpha_{\mathcal{C}}$ | Ppm/°C           | -120             | ±80              | +600             | +200             | -300             | -150             | -80              | ±30              | ±1000            |

| Dissipation factor tano (1 kHz)                  | 10 <sup>-4</sup> | 5                | 15               | 80               | 80               | 5                | 20               | 1                | 15               | 350              |

| Volume resistivity ρ                             | $\Omega$ cm      | 10 <sup>18</sup> | 10 <sup>16</sup> | 10 <sup>17</sup> | 10 <sup>17</sup> | 10 <sup>18</sup> | 10 <sup>17</sup> | 10 <sup>19</sup> | 10 <sup>17</sup> | 10 <sup>16</sup> |

| Dielectric absorption DA                         | %                | 0.01             | 0.1              | 0.5              | 1.2              | 0.02             | 0.05             | 0.01             | 0.6              | 2.5              |

| Operating temperature $T_{min}/T_{max}$          | °C               | -55<br>125       | -55<br>100       | -55<br>105       | -55<br>125       | -55<br>100       | -55<br>140       | -55<br>200       | -55<br>125       | -55<br>125       |

| Self-healing                                     |                  | no               | yes              | yes              | yes              | yes              | yes              | no               | no               | no               |

| SMD configuration                                |                  | no               | no               | yes              | yes              | no               | yes              | no               | yes              | yes              |

also featured with improved temperature stability with respect to PET. The capacitance temperature coefficient  $\alpha_{\rm C}$  of PEN is approximately only one third of the  $\alpha_{\rm C}$  of PET. The dielectric absorption DA of PEN is the biggest among the polymer film dielectrics. Its value of approximately 1 % is the order of magnitude of DA specified for MLCCs using X7R ceramics.

### 2.7 Other dielectric materials

Three types of dielectric materials, that have not been mentioned previously, are also listed in Table 2. Polytetrafluoroethylene (PTFE) better known under DuPont Company's trade name Teflon®, is an excellent insulating material, but PTFE film capacitors are very rare. Proper metallization of PTFE film is very difficult, this material is very expensive and films of a thickness < 6  $\mu m$  are not commercially available /7/. PTFE capacitors are used in high power applications where their high operating temperature range and low dissipation factor justify their high price.

The data on ceramic dielectric materials in Table 2 are given for comparison, since MLCC chips are very popular and cheap. In fact only COG ceramics, also known as NPO, are a real match for polymer films as far as stable high performance capacitors go. In addition to the materials discussed, X7R ceramics offer a cost and room efficient solution when large capacitances in small packages with low equivalent serial resistance (ESR) are required.

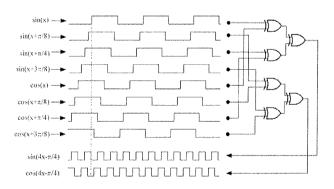

### Capacitor for integrating A/D converter

### 3.1 Four slope integration

Dual slope integration is a well-known method for accurate A/D conversion /1/. Accuracy and resolution are two distinctive features of such A/D converters. The resolution of integrating converters is determined by the ratio between the period of the clock that is used for counting and the time of integration, which is measured in clock periods. Arbitrary resolution can be achieved by appropriate selection of these two parameters, but at high resolutions conversion times can become unacceptably long, since maximal counter frequencies are limited. On the other hand, the accuracy of the result is determined by the used reference, if everything else is done ideally.

Integrating A/D conversion is very useful for measuring slowly varying quantities, e.g., strain, temperature, humidity, illumination etc. Furthermore, smart sensors with digital output can be designed as a combination of a standard microcontroller, an integrating A/D converter, and an analog sensor of a physical quantity. Low cost uncalibrated sensor devices may be used, without compromising the accuracy of the final result because the deficiencies of the analog sensing device are compensated numerically. The required signal conditioning data are obtained by calibra-

tion in the final stage of production and consequently stored in the nonvolatile portion of memory.

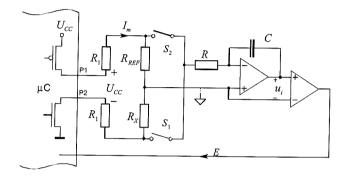

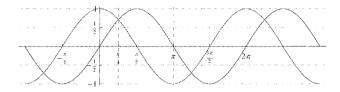

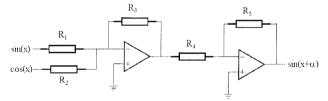

The pitfalls of capacitor selection are illustrated by the case of the small resistive temperature sensor. The important, i.e., the analog part of the smart sensor is shown by the simplified schematic diagram in Figure 1.

Fig. 1: Integrating A/D converter

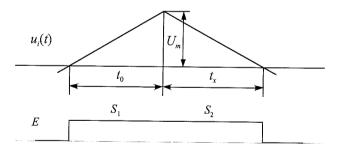

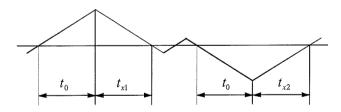

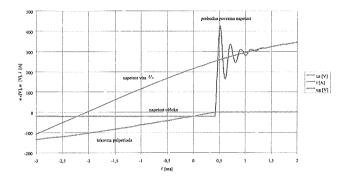

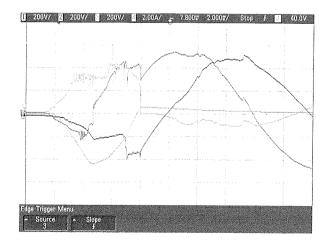

The conversion is initiated by closing switch  $S_1$  for fixed time  $t_0$  determined by a certain number of clock periods. The integrator output voltage  $u_i$  ramps up, reaching a maximum value that is proportional to the voltage across the sensor resistance  $R_X$ . At the end  $S_1$  is opened and  $S_2$  is closed. The output ramps down with a slope that is proportional to the voltage of a very stable resistor  $R_{REF}$ . When the integrator voltage becomes negative with respect to analog ground, the timer inside the microcontroller is stopped by the negative edge of the comparator output E. The plots of main converter signals are shown in Figure 2.

Fig. 2: Time diagram:  $u_i$  integrator output, E comparator output

The peak integrator voltage can be expressed by

$$U_m = I_m R_x \cdot \frac{t_0}{RC} = I_m R_{REF} \cdot \frac{t_x}{RC} \tag{1}$$

where  $I_m$  represents the measuring current through the sensor  $R_X$  and reference resistor  $R_{REF}$ , respectively. From the unknown resistance of the sensor is given by

$$R_x = R_{REF} \frac{t_x}{t_0} \tag{2}$$

meaning that only the stability of  $R_{REF}$  has influence on the result accuracy. This would be true if the opamp and comparator were ideal. The dual slope principle is not sensi-

tive to the instability of the integrator time constant RC as long as the constant remains unaltered during conversion time  $t_0 + t_x$ . The integrator peak voltage  $U_m$  given by remains unaffected by the comparator input offset voltage, since the counting of both times, charging  $t_0$  and discharging  $t_x$ , are started and stopped at the same integrator voltage, respectively. The actual conversion is started by closing  $S_2$  until the integrator output  $u_i$  becomes negative then both switches ( $S_1$  and  $S_2$ ) are toggled. The charging time  $t_0$  counter is not triggered until the rising edge of the comparator output E.

The input offset voltage  $U_0$  of the opamp in the integrator induces an error that can be expressed as

$$\Delta R_X = \frac{2U_0}{I_m} \tag{3}$$

with  $I_m$  denoting the measuring current (Figure 1). As it is shown in /8/ this error is compensated by reversing the polarity of the measuring current  $I_m$ , which is done by negation of the logic outputs P1 an P2 (Figure 1). The accurate result is the mean of the results obtained with both polarities of the current  $I_m$

$$R_x = R_{REF} \, \frac{t_{x1} + t_{x2}}{2 \, t_0} \tag{4}$$

The procedure with four slopes of integration, shown in Figure 3, doubles the required conversion time, but low cost opamps with offset voltages  $|U_0| \le 1$  mV may be used.

Fig. 3: Plot of the integrator output  $u_i(t)$  in the four slope A/D converter

#### 3.2 Dielectric absorption

The analyzed integrator is part of an intelligent resistive sensor of small physical dimensions ( $25 \times 9$  mm), therefore small passive components are used. The long integration time, which is necessary to achieve the prescribed resolution, and the low supply voltage require relatively large capacitance C = 100 nF that prevents the integrator output from reaching saturation. The first logical choice was an X7R ceramic chip capacitor, characterized by its small dimensions and SMD package. The value of capacitance appears neither in eqn. nor in , therefore the temperature coefficient and tolerance are not important for this purpose.

Experimental tests have shown poor accuracy in the intermittent mode of operation. The sensor was designed for battery powered systems, so the analog part of the circuit is powered only when the conversion takes place. Dielec-

tric absorption of the capacitor has been overlooked, and the effect of the absorbed charge has not been noticed in continuous mode since the capacitor mean voltage is zero.

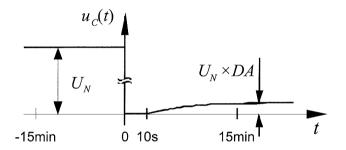

For the great majority of capacitor applications the dielectric absorption coefficient *DA* is not an important parameter. It matters only in some sample and hold circuits, and as is obvious, in integrators that operate once in a while and have long integrating times. This phenomenon can be measured as a small voltage that reappears across the open capacitor terminals after a charged capacitor has been thoroughly discharged. When voltage is applied to the capacitor plates a certain small part of the stored charge becomes bound on the surface of the dielectric. The process of charge recovery is governed by pretty long time constants that depend merely on the used dielectric material. Measurement of the absorption coefficient *DA* according to the standard MIL-C-19978 D /9/ is depicted in Figure 4.

Fig. 4: Timing and definition of voltages associated with the measuring of the dielectric absorption  $(U_N \text{ denotes nominal voltage}).$

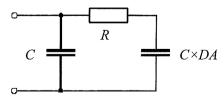

The effects of dielectric absorption in electric circuits are studied by suitable models that replace the capacitor in question. These models /10/, /11/ can be quite complex but in most cases a simple model shown in Figure 5 is sufficient for basic understanding. For commonly used dielectrics, 50% of the final voltage is recovered in 1 to 10 seconds, whereas it can take as much as 15 minutes to reach within 5% of the final value.

Fig. 5: The basic model of the dielectric absorption in capacitors

The resistance in the model of Figure 6 is given by

$$R = \frac{\tau}{DAC} \tag{5}$$

where t denotes the dominant recovery time constant and  $\it DA$  is the absorption coefficient (Table 2). The values of  $\tau$  for particular materials are usually not specified and have

to be determined by experimental measurements if a greater accuracy than the generally presumed range from 1 to 10 s is desired.

Detailed analysis has shown that the integrating capacitor was charged almost to supply voltage ( $U_{cc}$  = 3.3 V) when the negative supply pin of the amplifier chip was not tied to ground to reduce supply current. The error caused by recovered charge is drastically reduced by the four slope integration method. The error of n-th successive measurement after the amplifier is turned on is given by

$$\frac{\Delta R_X}{R_X} = \frac{U_{C0} DA}{2U_m} \left( 1 - e^{-\frac{T}{\tau}} \right)^2 e^{-\frac{2T}{\tau}(n-1)} \tag{6}$$

where  $U_{C0}$  is the integrating capacitor initial voltage,  $T = t_0$ +  $t_X$  is the conversion time of one polarity,  $\tau$  is the dominant time constant of the absorbed charge recovery, and  $U_m$  is the peak voltage of the integrator (Figure 2). The used ceramic chip capacitor has turned out to be completely inadequate for accurate temperature measurements on the basis of platinum resistors. Errors due to the dielectric absorption of the consecutive resistance measurements of the platinum resistor  $R_x$  (Pt 1000) are shown in Table 3. The results are expressed as temperature errors in °C using the temperature coefficient of platinum 3850 ppm/°C. The values in Table 3 are calculated using for two different absorption coefficients, whereas the other parameters are the same:  $U_{C0} = 3.3 \text{ V}$ ,  $U_m = 1 \text{ V}$ ,  $\tau = 3 \text{ s}$ , T = 1s. The errors calculated for X7R ceramics are in good agreement with the measurements, which have initiated more detailed analyses.

Table 3: Error of consecutive A/D conversions expressed in temperature

| Consecutive     | Δ <i>T</i> [°C] |                       |  |

|-----------------|-----------------|-----------------------|--|

| measurement no. | DA = 2.5% (X7R) | DA = 0.05% (PPS)      |  |

| 1               | 0.860           | 17×10 <sup>-3</sup>   |  |

| 2               | 0.442           | 8.84×10 <sup>-3</sup> |  |

| 3               | 0.227           | 4.54×10 <sup>-3</sup> |  |

| 4               | 0.116           | 2.33×10 <sup>-3</sup> |  |

| 5               | 0.059           | 1.19×10 <sup>-3</sup> |  |

The theoretical error caused by the absorption of PPS film SMD capacitor is smaller than the desired resolution of the design, therefore raw conversion data, i.e., timer counts that measure time  $t_x$ , have been observed. The raw results of consecutive conversions (after power up) are within plus minus one count, provided that the temperature is constant.

### 4. Tests in climatic chamber

### 4.1 Naked PPS SMD capacitor

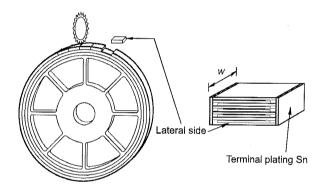

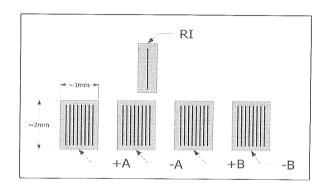

Encouraged by the theoretical results (Table 3) an adequate substitution for the X7R MLCC has been found in the form of the stacked PPS film capacitor. These capacitors are almost a perfect choice and feature a very low absorption coefficient DA and very low dissipation  $\tan\delta < 5 \cdot 10^{-4}$  in the temperature range from -25°C to 80°C. The data for PPS shown in Table 2 are rather misleading because the worst values over the whole temperature range are given. In addition, PPS capacitors are available as small SMD components that save space on the PCB and fit on solder pads provided for the former ceramic capacitor. The construction of naked stacked film capacitors is shown in Figure 7. The lateral side is usually left without any coating /4/.

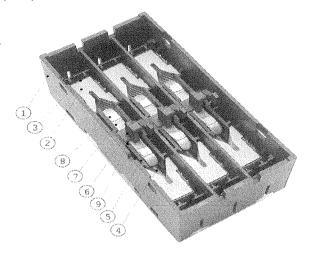

Fig. 6: Production and construction of stacked naked PPS film chip capacitors

In stacked-film production technology, large rings of metallized film are wound onto core wheels with diameters up to 60 cm. Then the rings are sawed apart obtaining well defined width (dimension W in Figure 6). In this way, capacitances with very low tolerances are obtained, since the active body is very homogenous, without the air pockets which are typical of flattened wound bodies. Actual measurements have proved that PPS capacitors have negligible dielectric absorption; hence no differences have been detected between the results of the first and immediately repeated measurements.

Upon the verification of the calibrated sensors, some of them returned values that were up to 2°C lower than the actual temperature in the chamber, which was 12°C. Among the 120 devices under test, about 10% were bad, i.e.,  $|\Delta T| > 0.1$ °C. It turned out that humidity inside the chamber had run out of control. At temperatures around 12°C the humidity had exceeded 90%. The deviation of certain circuits was obviously influenced by humidity, so protection against moisture should improve the performance of the PCB in humid environments. Polyurethane coating applied to the assembled PCBs did not help. The deviations of the bad circuits remained unacceptable.

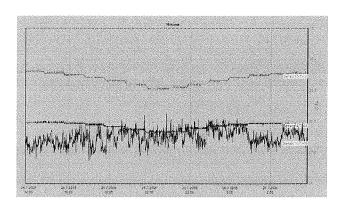

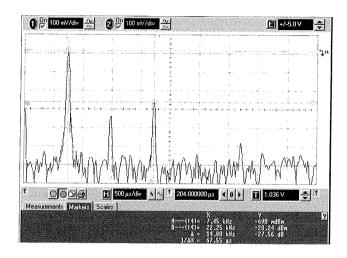

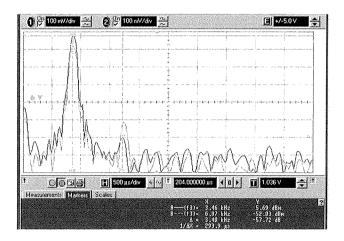

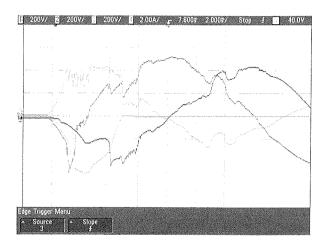

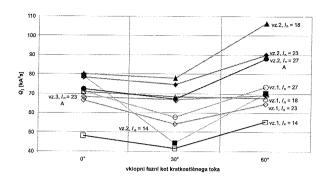

Since it was not clear which part of the circuit was affected by humidity, several experiments were carried out. The results in Figure 8 show that high humidity and temperature affect the four slope A/D converter. In this experiment the temperature dependent resistors (Pt1000) of three sensors were kept outside the climatic chamber at a constant temperature, while the PCBs were exposed to temperatures increasing in increments at high humidity and decreasing at low humidity, respectively. As one can note from the plots in Figure 7, the impact of the temperature increments in the presence of high humidity is not the same for all circuits, but when humidity is low the circuits are left virtually unaffected.

Fig. 7: Measurement results of three sensors with naked PPS capacitors: at high humidity RH = 90% the chamber temperature was increased in 5°C increments from 15°C to 45°C, then the air was dried to RH = 30% and the temperature was decreased to 15°C, again in decrements of 5°C. Each step of this temperature reduction lasted 1hour.

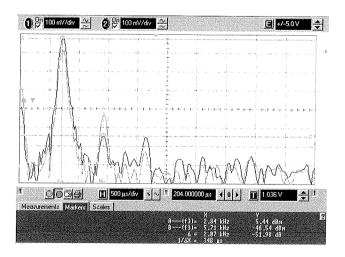

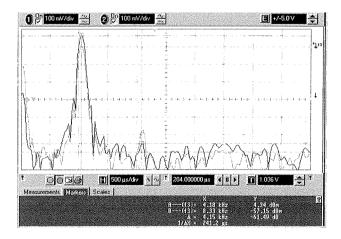

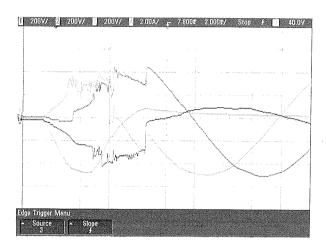

Next, the integrating PPS chip capacitors of the three tested samples were replaced by encapsulated PET capacitors with wire terminals and then the same experiment was repeated. The plots that are shown in Figure 8 reliably indicate that certain PPS chip capacitors were affected by high humidity and not the PCB itself. The results registered by the third sensor are meaningless since a fault occurred during the replacement of the capacitor. The steps in the upper and middle plot are a consequence of the temperature coefficients of each reference resistor  $R_{\it REF}$ , because the sensors were kept at different, i.e., constant temperatures during the test.

### 4.2 The influence of humidity on insulation resistance

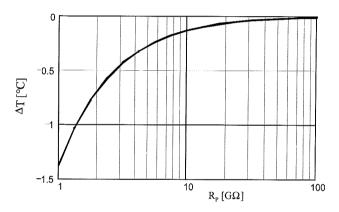

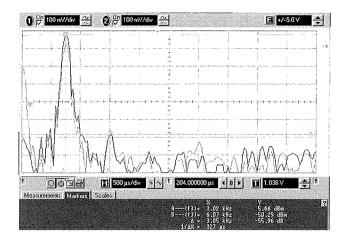

Obviously, some of the used PPS capacitors were influenced by moisture. The influence of absorbed moisture on capacitance was excluded by empirical immersion tests, so only the surface resistance between capacitor terminals  $R_P$  remains as the possible cause of inaccurate conversion, if this resistance is decreased due to air humidity.

Fig. 8: Measurement results of three sensors with encapsulated PET capacitors: at RH=90% the chamber temperature was increased in increments of 5°C from 15°C to 45°C (the left half of the diagram), then the air was dried to RH=30% and the temperature was decrementally reduced down to 15°C.

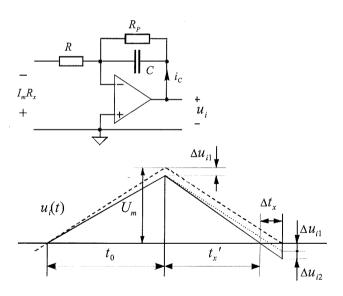

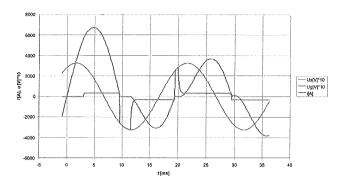

Firstly, we have to estimate the order of magnitude of such a decrease of resistance that could cause the observed inaccuracies. As is shown in Figure 9, the parallel resistance represents a leak for the charge stored in the integrating capacitor. The sensitivity can either be derived from the exact analytic solution, or a few simple approximations can be used. The latter alternative is presented as follows.

Fig. 9: Integrator with insulation resistance  $R_P$  (above), plot of integrator output voltage  $u_i$  with (——) and without  $R_P$  (---) (bellow)

At the end of the first step of conversion the peak integrator output is reduced by

$$\Delta u_{i1} = \frac{\Delta q}{C} = -\frac{1}{C} \int_{t}^{t+t_0} \frac{u_i(t)}{R_P} dt = -\frac{1}{2} \cdot \frac{U_m t_0}{R_P C}$$

(7)

with  $\Delta q$  denoting the charge that leaks through  $R_P$  and  $U_m$  is the voltage that would be reached if there were no leak-

age, i.e.,  $R_P \rightarrow \infty$ . The shape of  $u_i(t)$  in is considered straight and  $\Delta u_{i1} = U_m$  is neglected in the integral. During the second step of conversion,  $u_i(t)$  decreases faster than in the ideal case (Figure 9) and after discharging for  $t_0$  it would become negative. The relative error of the conversion

$$\frac{\Delta t_x}{t_x} = \frac{\Delta u_{i1} + \Delta u_{i2}}{U_m} = \frac{2\Delta u_{i1}}{U_m} = -\frac{t_0}{R_P C}$$

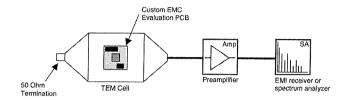

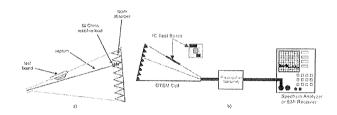

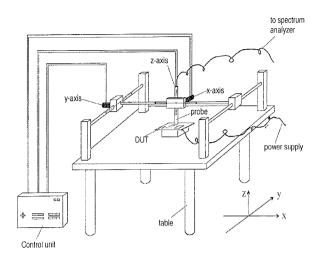

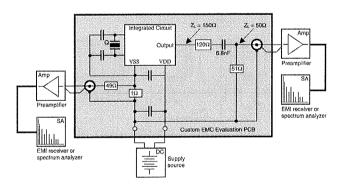

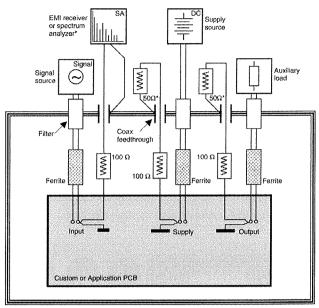

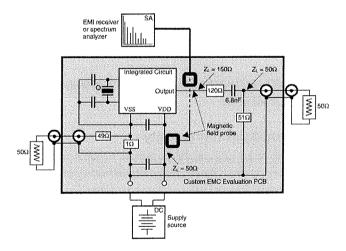

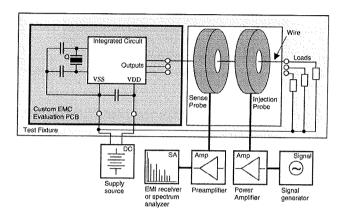

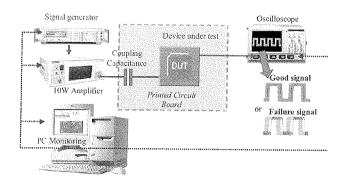

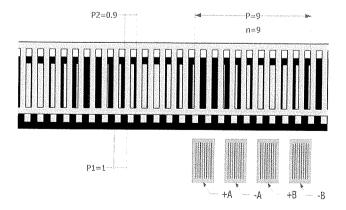

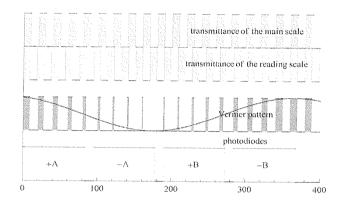

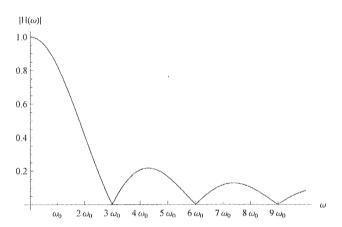

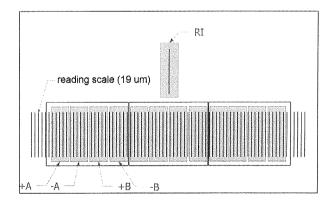

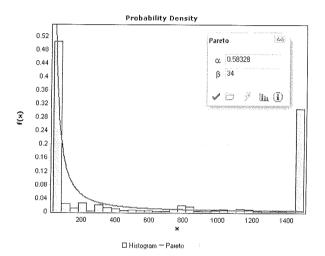

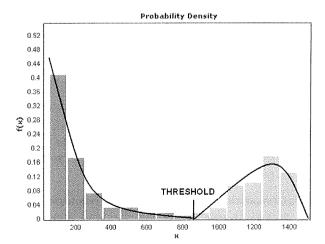

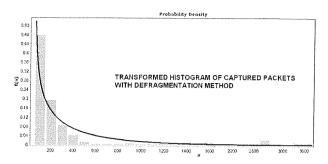

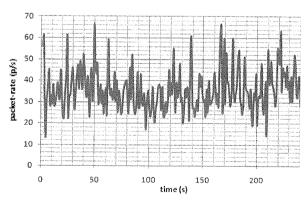

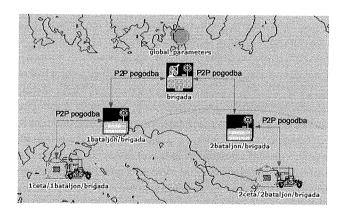

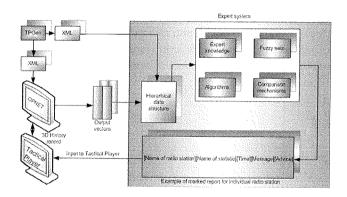

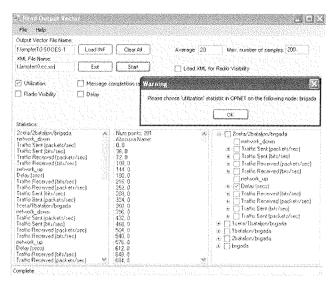

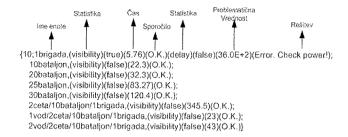

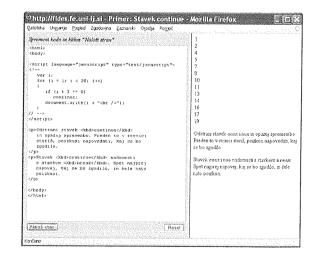

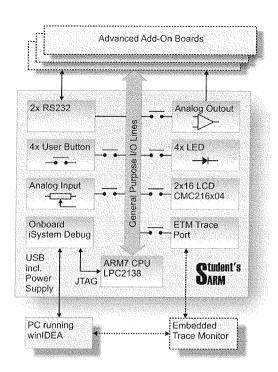

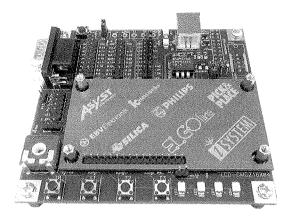

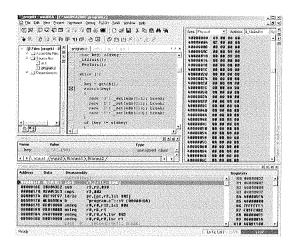

(8)