Strokovno društvo za mikroelektroniko elektronske sestavne dele in materiale

4.2005

Strokovna revija za mikroelektroniko, elektronske sestavne dele in materiale Journal of Microelectronics, Electronic Components and Materials

INFORMACIJE MIDEM, LETNIK 35, ŠT. 4(116), LJUBLJANA, december 2005

## INFORMACIJE

## **MIDEM**

**4** ° 2005

INFORMACIJE MIDEM

LETNIK 35. ŠT. 4(116). LJUBLJANA.

DECEMBER 2005

INFORMACIJE MIDEM

VOLUME 35, NO. 4(116), LJUBLJANA,

DECEMBER 2005

Revija izhaja trimesečno (marec, junij, september, december). Izdaja strokovno društvo za mikroelektroniko, elektronske sestavne dele in materiale - MIDEM. Published quarterly (march, june, september, december) by Society for Microelectronics, Electronic Components and Materials - MIDEM.

Glavni in odgovorni urednik

**Editor in Chief**

Dr. Iztok Šorli, univ. dipl.ina.fiz... MIKROIKS d.o.o., Liubliana

Tehnični urednik **Executive Editor**

Dr. Iztok Šorli, univ. dipl.ing.fiz., MIKROIKS d.o.o., Ljubljana

Uredniški odbor **Editorial Board**

Dr. Barbara Malič, univ. dipl.ing. kem., Institut Jožef Stefan, Ljubljana

Prof. dr. Slavko Amon, univ. dipl.ing. el., Fakulteta za elektrotehniko, Ljubljana Prof. dr. Marko Topič, univ. dipl.ing. el., Fakulteta za elektrotehniko, Ljubljana

Prof. dr. Rudi Babič, univ. dipl.ing. el., Fakulteta za elektrotehniko, računalništvo in informatiko

Maribor

Dr. Marko Hrovat, univ. dipl.ing, kem., Institut Jožef Stefan, Ljubljana Dr. Wolfgang Pribyl, Austria Mikro Systeme Intl. AG, Unterpremstaetten

Časopisni svet International Advisory Board Prof. dr. Janez Trontelj, univ. dipl.ing. el., Fakulteta za elektrotehniko, Ljubljana,

PREDSEDNIK - PRESIDENT Prof. dr. Cor Claeys, IMEC, Leuven

Dr. Jean-Marie Haussonne, EIC-LUSAC, Octeville

Darko Belavič, univ. dipl.ing. el., Institut Jožef Stefan, Ljubljana

Prof. dr. Zvonko Fazarinc, univ. dipl.ing., CIS, Stanford University, Stanford

Prof. dr. Giorgio Pignatel, University of Padova

Prof. dr. Stane Pejovnik, univ. dipl.ing., Fakulteta za kemijo in kemijsko tehnologijo, Ljubljana

Dr. Giovanni Soncini, University of Trento, Trento

Prof. dr. Anton Zalar, univ. dipl.ing.met., Institut Jožef Stefan, Ljubljana Dr. Peter Weissglas, Swedish Institute of Microelectronics, Stockholm

Prof. dr. Leszek J. Golonka, Technical University Wroclaw

Naslov uredništva Headquarters

Uredništvo Informacije MIDEM

MIDEM pri MIKROIKS

Stegne 11, 1521 Ljubljana, Slovenija + 386 (0)1 51 33 768 tel.: + 386 (0)1 51 33 771 e-mail: Iztok.Sorli@guest.arnes.si http://www.midem-drustvo.si/

Letna naročnina znaša 12.000,00 SIT, cena posamezne številke je 3000,00 SIT. Člani in sponzorji MIDEM prejemajo Informacije MIDEM brezplačno. Annual subscription rate is EUR 100, separate issue is EUR 25. MIDEM members and Society sponsors receive Informacije MIDEM for free.

Znanstveni svet za tehnične vede I je podal pozitivno mnenje o reviji kot znanstveno strokovni reviji za mikroelektroniko, elektronske sestavne dele in materiale. Izdajo revije sofinancirajo ARRS in sponzorji društva.

Scientific Council for Technical Sciences of Slovene Research Agency has recognized Informacije MIDEM as scientific Journal for microelectronics, electronic components and materials.

Publishing of the Journal is financed by Slovene Research Agency and by Society sponsors.

Znanstveno strokovne prispevke objavljene v Informacijah MIDEM zajemamo v podatkovne baze COBISS in INSPEC.

Prispevke iz revije zajema ISI® v naslednje svoje produkte: Sci Search®, Research Alert® in Materials Science Citation Index™

Scientific and professional papers published in Informacije MIDEM are assessed into COBISS and INSPEC databases.

The Journal is indexed by ISI® for Sci Search®, Research Alert® and Material Science Citation Index™

Po mnenju Ministrstva za informiranje št.23/300-92 šteje glasilo Informacije MIDEM med proizvode informativnega značaja.

Grafična priprava in tisk

Printed by

BIRO M, Ljubljana

Naklada

1000 izvodov

Circulation

1000 issues

Poštnina plačana pri pošti 1102 Ljubljana

Slovenia Taxe Percue

| UDK621.3:(53+54+621+66),   | ISSN0352-9045  |

|----------------------------|----------------|

| UDNUZ1.3.(33) 34 (021 (00) | 100110002-3070 |

## Informacije MIDEM 35(2005)4, Ljubljana

| ZNANSTVENO STROKOVNI PRISPEVKI                                                                                                                                      |     | PROFESSIONAL SCIENTIFIC PAPERS                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M. Lethiecq, F. Levassort, L. Tran-Huu-Hue:<br>Ultrazvočni pretvorniki za slikanje z visoko ločljivostjo:<br>od piezoelektričnih struktur do medicinske diagnostike | 177 | M. Lethiecq, F. Levassort, L. Tran-Huu-Hue:<br>Ultrasonic Transducers For High Resolution Imaging:<br>From Piezoelectric Structures To Medical<br>Diagnostics |

| R. Ubar:<br>Odločitveni diagrami in digitalno testiranje                                                                                                            | 187 | R. Ubar:<br>Decision Diagrams And Digital Test                                                                                                                |

| V. Eveloy, S. Ganesan, Y. Fukuda, J. Wu,<br>M. G. Pecht:<br>WEEE, RoHS in kaj vse morate storiti, da se<br>pripravite na elektroniko brez svinca                    | 196 | V. Eveloy, S. Ganesan, Y. Fukuda, J. Wu,<br>M. G. Pecht:<br>WEEE, RoHS, And What You Must Do To Get Ready<br>For Lead-free Electronics                        |

| G. Koziol:<br>Laboratorij za raziskavo in študij materialov in<br>procesov brez svinca                                                                              | 213 | G. Koziol:<br>Quality Laboratory For Investigation of Lead-free<br>Materials And Processes                                                                    |

| Z. Drozd, J. Bronowski, J. Drozd, M. Szwech:<br>Pospešeni testi zanesljivosti spajkanih<br>stikov brez svinca                                                       | 221 | Z. Drozd, J. Bronowski, J. Drozd, M. Szwech:<br>Accelerated Reliability Tests of Lead<br>-free Soldered Joints                                                |

| P. Mach, A. Duraj:<br>Lepljenje ali spajkanje brez svinca?                                                                                                          | 228 | P. Mach, A. Duraj:<br>Adhesive Joining Or Lead-Free Soldering?                                                                                                |

| J. Renko:<br>Direktivi WEEE/RoHS: od začetne informacije do<br>Slovenske implementacije                                                                             | 236 | J. Renko: Directives WEEE/RoHS: From Early Information to the Slovenian Implementation                                                                        |

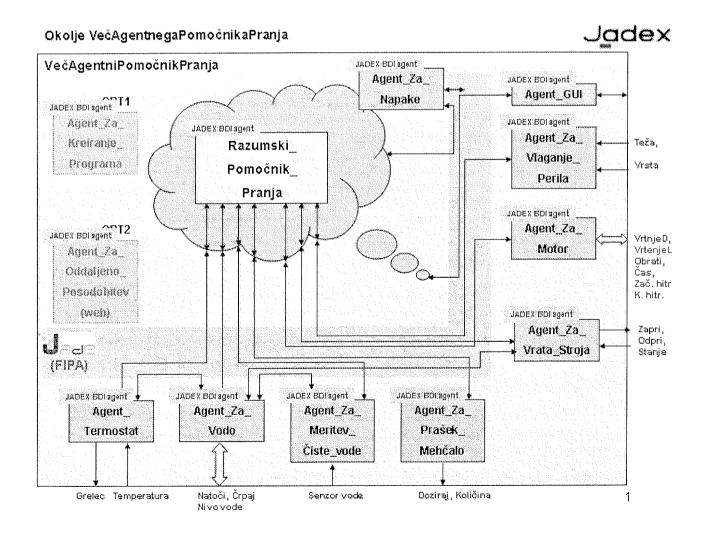

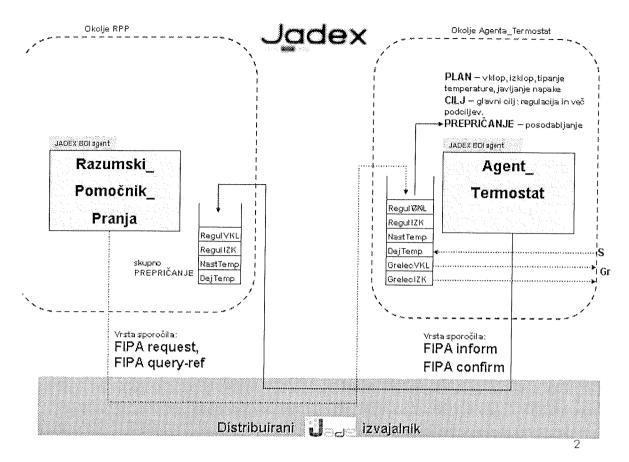

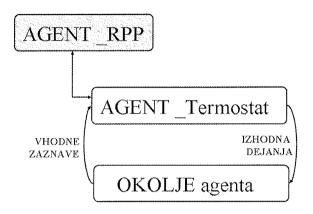

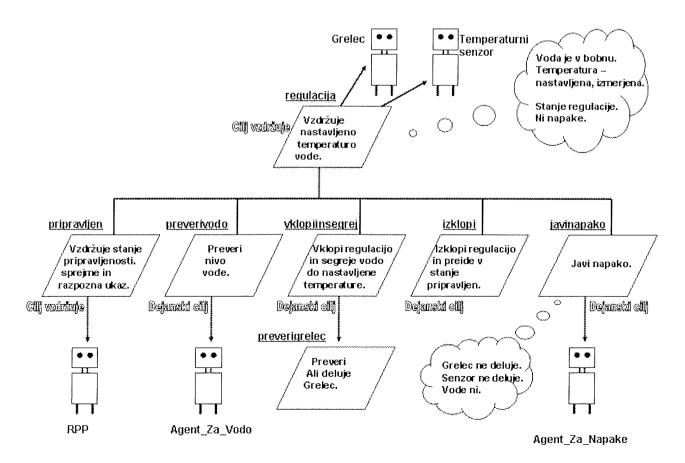

| K. Steblovnik, J. Tasič, D. Zazula:<br>Razumni hišni pomočnik                                                                                                       | 240 | K. Steblovnik, J. Tasič, D. Zazula:<br>Intelligent Home Assistant                                                                                             |

| Konferenca MIDEM 2005 - poročilo                                                                                                                                    | 253 | MIDEM 2005 Conference - report                                                                                                                                |

| NOVICE                                                                                                                                                              | 257 | NEWS                                                                                                                                                          |

| VSEBINA LETNIKA 2005                                                                                                                                                | 260 | VOLUME 2005 CONTENT                                                                                                                                           |

| MIDEM prijavnica                                                                                                                                                    | 263 | MIDEM Registration Form                                                                                                                                       |

| Slika na naslovnici:<br>Konferenca MIDEM 2005 se je odvijala v prijetnem<br>okolju hotela Ribno pri Bledu                                                           |     | Front page:<br>MIDEM 2005 Conference was held in pleasant<br>environment of Hotel Ribno near Bled                                                             |

## Obnovitev članstva v strokovnem društvu MIDEM in iz tega izhajajoče ugodnosti in obveznosti

Spoštovani,

V svojem več desetletij dolgem obstoju in delovanju smo si prizadevali narediti društvo privlačno in koristno vsem članom. Z delovanjem društva ste se srečali tudi vi in se odločili, da se v društvo včlanite. Življenske poti, zaposlitev in strokovno zanimanje pa se z leti spreminjajo, najrazličnejši dogodki, izzivi in odločitve so vas morda usmerili v povsem druga področja in vaš interes za delovanje ali članstvo v društvu se je z leti močno spremenil, morda izginil. Morda pa vas aktivnosti društva kljub temu še vedno zanimajo, če ne drugače, kot spomin na prijetne čase, ki smo jih skupaj preživeli. Spremenili so se tudi naslovi in način komuniciranja.

Ker je seznam članstva postal dolg, očitno pa je, da mnogi nekdanji člani nimajo več interesa za sodelovanje v društvu, se je Izvršilni odbor društva odločil, da stanje članstva uredi in vas zato prosi, da izpolnite in nam pošljete obrazec priložen na koncu revije.

Naj vas ponovno spomnimo na ugodnosti, ki izhajajo iz vašega članstva. Kot član strokovnega društva prejemate revijo »Informacije MIDEM«, povabljeni ste na strokovne konference, kjer lahko predstavite svoje raziskovalne in razvojne dosežke ali srečate stare znance in nove, povabljene predavatelje s področja, ki vas zanima. O svojih dosežkih in problemih lahko poročate v strokovni reviji, ki ima ugleden IMPACT faktor. S svojimi predlogi lahko usmerjate delovanje društva.

Vaša obveza je plačilo članarine 25 EUR na leto. Članarino lahko plačate na transakcijski račun društva pri A-banki : 051008010631192. Pri nakazilu ne pozabite navesti svojega imena!

Upamo, da vas delovanje društva še vedno zanima in da boste članstvo obnovili. Žal pa bomo morali dosedanje člane, ki članstva ne boste obnovili do konca leta 2006, brisati iz seznama članstva.

Prijavnice pošljite na naslov:

MIDEM pri MIKROIKS

Stegne 11

1521 Ljubljana

Ljubljana, december 2005

# ULTRASONIC TRANSDUCERS FOR HIGH RESOLUTION IMAGING: FROM PIEZOELECTRIC STRUCTURES TO MEDICAL DIAGNOSTICS

<sup>1</sup> Marc Lethiecq, <sup>2</sup> Franck Levassort and <sup>2</sup> Louis-Pascal Tran-Huu-Hue <sup>1</sup> LUSSI-EIVL, Blois-cedex, France <sup>2</sup> François Rabelais University, Tours, France

INVITED PAPER

MIDEM 2005 CONFERENCE

14.09.2005 - 16.09.20045, Bled, Slovenia

Key words: diagnostics, imaging, high resolution imaging, transducers, piezoelectric transducers

Abstract: The fields of medical diagnostics, namely for examination of skin, eye and blood vessels, of medical research on small animals, of cosmetics and also of non destructive testing of small parts all require very high resolution imaging techniques. Ultrasonic waves, at frequencies between 20 and 100 MHz, allow the observation of structures of several mm size with resolutions in the micrometers range. For this, specific systems including ultrasonic transducers, transmit/receive electronics and image processing and display need to be developed, since classical ultrasonic systems operate only in the 1-15 MHz range. The electroacoustic performance of transducers is one (if not the) key element of such systems. Parameters such as the centre frequency, the relative bandwidth and the loop sensitivity need to be optimised and adjusted for each application. They define both the axial resolution of the images produced and the depth of penetration, and also influence the contrast. To obtain high lateral resolution, the transducers must be focused, which implies either using a focusing lens or shaping the transducer surface. The paper describes current work on piezoelectric materials and structures, namely thick films, developed specifically for these applications. Material properties measured on different samples including thin plates, thick films on several substrates, machined bulk ceramics are presented and compared. The design of transducers using those materials identified as potentially most efficient is discussed, as well as transducer fabrication and performance.

## Ultrazvočni pretvorniki za slikanje z visoko ločljivostjo : od piezoelektričnih struktur do medicinske diagnostike

Kjučne besede: diagnostika, slikanje, slikanje z visoko ločljivostjo, pretvorniki, piezo električni pretvorniki

Izvleček: Medicinska diagnostika, npr. pregled kože, oči in žil, preiskave malih živalih, raziskave v kozmetiki, kot tudi neporušno testiranje majhnih sestavnih delov, zahteva tehnike slikanja z visoko ločljivostjo. Ultrazvočni valovi s frekvenco med 20 in 100 MHz omogočajo opazovanje struktur velikosti nekaj milimetrov z mikrometrsko ločljivostjo. V ta namen je potrebno razviti posebne podsisteme, kot so ultrazvočni pretvorniki, oddajno/sprejemna elektronika, prikazovalniki in obdelava slik, saj klasični ultrazvočni sistemi delujejo le v območju 1-15MHz. Elektroakustične lastnosti pretvornikov so ključnega pomena za delovanje takih sistemov. Parametri, kot so sredinska frekvenca, relativna širina pasu in občutljivost morajo biti optimizirani in nastavljeni za vsako uporabo posebej. Le-ti definirajo osno ločljivost posnetih slik, globino prodiranja ultrazvoka in vplivajo na kontrast. Za doseganje visoke lateralne ločljivosti, moramo uporabiti bodisi zbiralno lečo ali ustrezno oblikovati površino pretvornika.

V prispevku opisujemo razvoj piezoelektričnih materialov in debeloplastnih struktur za uporabo v ultrazvočni medicinski diagnostiki. Predstavljamo in primerjamo lastnosti materialov in plastnih struktur na različnih podlagah. Komentiramo načrtovanje, izdelavo in delovanje ultrazvočnih pretvornikov, narejenih iz materialov z največjim piezoelektričnim odzivom.

### 1. Introduction

High frequency ultrasound devices have been developing in many fields such as electronic filters and resonators, material characterisation (acoustic microscopes), non-destructive testing and medical diagnostics. This paper will deal with ultrasonic transducers which are designed for imaging applications, and in particular for medical diagnosis in organs such as skin, eye and blood vessels, as well as for non-destructive evaluation and small animal examinations. This field has generated a great deal of research as well as commercial products, attested by many publications in both specialised and general scientific journals

/1-4/. The frequency range starts around 20 MHz, and extends up to 100 MHz. The paper will first present general transducer requirements, then specific piezoelectric materials developed for high frequency will be reviewed and finally transducer fabrication and performance will be discussed (modelling and characterisation).

## 2. Transducer requirements

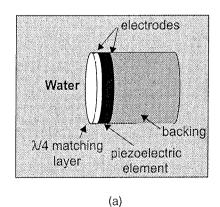

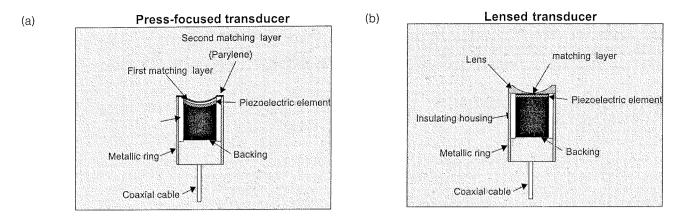

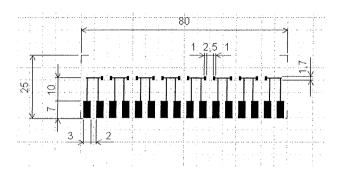

The classical single-element transducer is composed of a piezoelectric plate or disc poled along the thickness direction, whose thickness defines the resonance frequency of the device (Figure 1). The piezoelectric element (typ-

ically a ferroelectric ceramic), has an acoustic impedance (i.e. around 33 MRa) much higher than biological tissues (close to that of water, i.e. 1.5 MRa). This large difference leads to poor acoustic matching and low axial resolution. Consequently, other layers are added to this active layer. First, on its rear face, a thick layer is bonded (backing) /5/. It serves as a mechanical support for the active element, but acoustic energy flows by the rear face. The closer the backing acoustical impedance is to that of the active layer, the more energy is lost. The consequence is a lower sensitivity but a higher axial resolution. The attenuation coefficient and the thickness of the backing layer must be sufficient so that no energy can be radiated back to the active layer. which would produce parasitic echoes. Secondly, on the front (i.e. between the piezoceramic and the propagation medium), a matching layer is used. Its design is optimised in order to increase the transfer of energy from the active layer to the tissues /6/ /7/. The thickness of this matching layer is generally around a quarter-wavelength at the resonance frequency, and its acoustical impedance is intermediate between those of the piezoceramic and tissues. The use of a matching layer thus improves the sensitivity of the transducer. Moreover, since the acoustical energy can better flow towards the tissues, the duration of acoustical resonance in the active layer is decreased. Consequently, the matching layer also improves axial resolution. Influence of these two elements on the impulse and frequency responses transducers is shown in Figure 1 and a trade-off has to be found for each application. The active layer is typically a PZT-based material, while matching layers and backings are polymer-based.

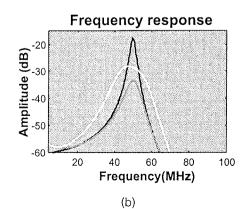

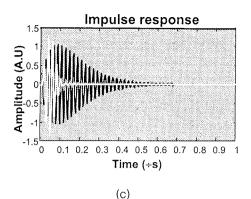

Figure 1: (a) Classical diagram of a single-element transducer.

(b) and (c) Frequency and impulse responses of: black line: piezoelectric element (water on front face and air on rear face), grey line: piezoelectric element+backing, white line: with matching layer.

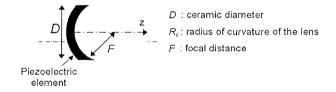

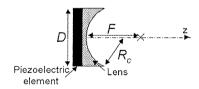

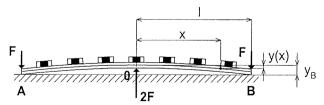

The radiation pattern of a focused single-element transducer is defined by the size of the active element (D) and the focal distance (F) (Figure 2). In the case where a lens is used for focusing, (F) can be deduced from the lens curvature (R<sub>c</sub>) and the sound wave velocities in the lens and propagation media (Figure 3).

Figure 2: Shape-focused transducer.

Figure 3: Lens-focused transducer.

Lateral resolution is linked to the width of the acoustic beam and is optimum at the focal distance. Approximate expressions of this lateral resolution (R<sub>lateral</sub>), depth of field (DOF) and axial resolution (R<sub>axial</sub>) for a spherical shape transducer are defined (eq. 1). The ratio between the focal distance and the diameter of the piezoelectric element, called the f-number (f#), allows to define the trade-off between lateral resolution and depth of field.  $\lambda$  is the wavelength at nominal frequency and BWR-6dB is the relative bandwidth at -6dB.

$$\begin{split} f_{\#} &= \frac{F}{D}, & R_{lateral} \approx & \lambda \times \ f_{\#}, \\ & DOF \approx 7 \lambda \times f_{\#}^2, & R_{axial} \approx \frac{\lambda}{2BWR_{-6dB}} \end{split} \tag{1}$$

The resolutions and depth of field can change of several orders of magnitude according to frequency. High frequencies lead to high resolutions but, due to increase of attenuation in tissues, the depth of penetration in the explored medium is reduced. The acoustical properties of the explored medium as well as of the driving electronics also influence imaging performance /4//8/.

For typical fixed values for medical imaging as the centre frequency at 50 MHz (i.e. a f-number of 2.5, a focal distance at 7.5 mm, a relative bandwidth (-6dB) at 60%), the corresponding diameter D is at 3 mm, the thickness of the piezoelectric element (ceramic) is around 45  $\mu m$ , the axial and lateral resolutions are respectively around 30 and 75  $\mu m$ , and the depth of field around 1.3 mm. These resolutions correspond to those generally required for skin imaging.

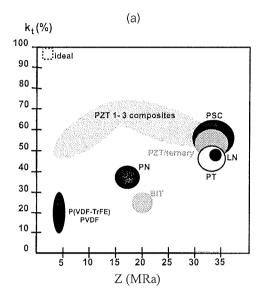

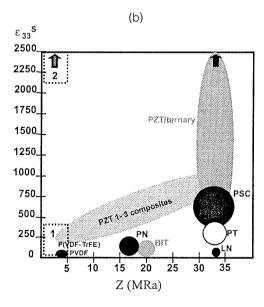

## 3. Piezoelectric materials

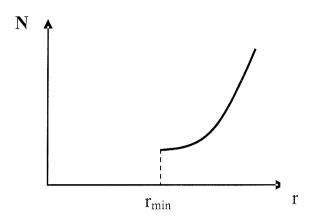

For the piezoelectric material, in particular for medical applications, two of the most important material parameters are the effective electromechanical coupling coefficient keff of the main vibration mode used and the acoustic impedance Zac. The keff factor represents the piezoelectric activity of the material in the considered mode of vibration, in other words the capability of the material to convert electrical energy into acoustical energy (or vice-versa) in a short time; it should of course be as high as possible. This factor depends not only on the material properties but also on the geometry of the active element. In medical imaging applications, all vibration modes are longitudinal, i.e. the displacements are in the poling direction which defines the thickness dimension. For large plates or discs (thickness much lower than lateral dimensions), the thickness coupling factor kt is used. For bars or pillars (thickness higher than lateral dimensions), the factor is k33. For the intermediate case of an array element (one small and one large lateral dimensions with a thickness value between them), k'33 factor is defined /9/. The value of the dielectric constant also has an important role on the electrical matching. Figure 4 represents values of the thickness mode coupling factor (kt) versus the acoustic impedance (Zac) for a wide range of available piezoelectric materials. It can be observed that no material allows to obtain both high coupling and low acoustic impedance (ideal area on Figure 4). The best trade-off must be found among these materials. For almost all medical transducers applications, PZT piezoceramics are used because of their high coupling factor, even if their acoustic impedance is high, since this can be compensated for by using acoustic matching layers in the transducer structure. For a given application, properties such

as dielectric constant and grain size allow to choose a specific material reference. A large range of properties can be found from relatively low (a few hundred) to very high (a few thousand) relative dielectric constants with grain sizes from one to ten micrometers. For large area devices such as single element transducer, a moderate dielectric constant allows good electrical matching to cables and electronics (which are typically at 50 to 80 ohms) (area 1), while array elements require much higher dielectric constants (area 2).

PZT: Lead zirconate titanate, PT: Lead titanate, PN: Lead metaniobate, BIT: Bismuth titanate, PSC: Piezoelectric single crystals, LN: Lithium Niobate, PZT 1-3 composites: PZT and polymer

Figure 4: (a) Electromechanical coupling factor in thickness mode (k<sub>t</sub>) and (b) Dielectric constant at constant strain versus acoustical impedance for a wide range of piezoelectric materials.

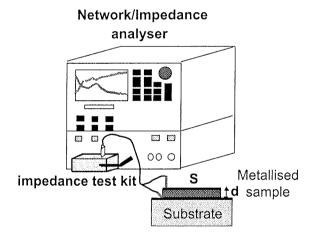

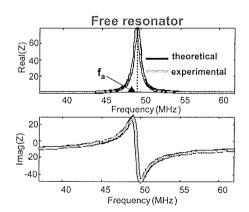

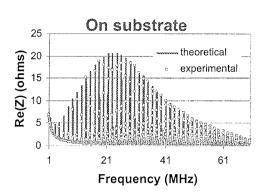

Measurements of the complex electrical impedance as a function of frequency allow the dielectric, mechanical and electromechanical properties to be obtained by a fitting process /9-11/. The set-up is composed of a network analyser with its impedance test kit and a spring clip fixture to make electrical contacts with the electroded piezoelectric material (Figure 5(a)). These contacts have a great importance in particular at high frequency, since to stay in free resonator condition, their sizes must be very small in comparison with the size of the measured sample and the forces applied must not disturb the resonance mode. Figure 5(b) shows the typical resonance of a PZT disk made by tape-casting which has an antiresonant frequency around 50 MHz. At high frequency, the piezoelectric element is often deposited on a substrate during the fabrication process (Figure 5(a)) and the experimental electrical impedance depends on this substrate. With an electrical equivalent circuit, such as KLM which is well adapted to multilayer structures (electrodes, piezoelectric layer and substrate), and knowing all the acoustic properties of electrodes and substrate, the fitting process allows to obtain the properties of the piezoelectric layer (Figure 4 (c))/12//13/.

(a)

(b)

(c)

Figure 5:

(a) experimental set-up for electrical impedance measurements,

(b) experimental and theoretical complex impedance (fit) of high frequency piezoelectric disk in free resonator conditions, (c) experimental and theoretical impedance (real part) (fit) of high frequency piezoelectric thick film on alumina substrate.

Typical parameters characterised are the following:

- Resonant (f<sub>r</sub>) and antiresonant (f<sub>a</sub>) frequencies which correspond respectively to maximum of real admittance and real impedance;

- The thickness coupling factor (vibration corresponding to a thickness mode) can be calculated with

$$k_{t} = \sqrt{\frac{\pi}{2} \frac{f_{r}}{f_{a}} \cot(\frac{\pi}{2} \frac{f_{r}}{f_{a}})}$$

(2)

- The longitudinal wave velocity v = 2df<sub>a</sub> (d: thickness of the piezoelectric sample) (3)

- Dielectric constant ε is obtain from the capacitance

C<sub>0</sub> after resonance and dimensions;

- Mechanical quality factor (or mechanical losses  $\delta_{\text{m}})$

$$Q_{m} = \frac{f_{a}}{\Lambda f} \tag{4}$$

where Df corresponds to the frequency width at half the maximum resistance;

Dielectric losses appear as an offset on resistance curves, the measurement can be made at twice the anti-resonant frequency and they can change with frequency.

Piezopolymers such as PVDF or copolymers /14/ /15/ can be purchased as films with thickness of one to a few tens of microns which can be directly used for high frequency applications. Their coupling factors are relatively low (between 15 and 30%) and relative clamped dielectric constant is low (around 5). These two last properties tend to give a relatively low sensitivity and the electric matching is difficult. But their acoustic impedance is low and close to that of tissues (between 4 and 5 MRa), so acoustic matching is not indispensable (Table 1).

Table 1: Main properties of a P(VDF-TrFE) piezoelectric copolymer film.

| material    | ε <sub>33</sub> <sup>S</sup> /ε <sub>0</sub> | v <sub>i</sub> (m/s) | k <sub>t</sub> (%) | δ <sub>e</sub> (%) | δ <sub>m</sub> (%) | <b>Z</b><br>(MRa) | ref  |

|-------------|----------------------------------------------|----------------------|--------------------|--------------------|--------------------|-------------------|------|

| P(VDF-TrFE) | 4.1                                          | 2380                 | 29                 | 6.9                | 4.0                | 4.6               | [16] |

$\epsilon_{33}^{\rm S}/\epsilon_0$ : clamped dielectric constant;  $v_i$ : longitudinal wave velocity;  $k_t$ : thickness coupling factor;  $\delta_e$ : dielectric losses;  $\delta_m$ : mechanical losses; Z: acoustic impedance;

The second main and determinant advantage is the flexibility of the film which allows a direct focusing and avoids the addition of a lens (Figure 6). Even with a relatively low (k<sub>t</sub>), these materials are widely used for high frequency transducer fabrication in the range of from 20 MHz to over 100 MHz.

Pz21

(a)

(b)

(a)

(b)

c)

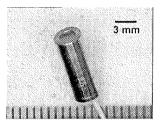

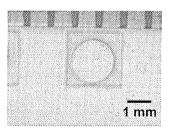

Figure 6: (a) Copolymer sheet and (b) high frequency copolymer based transducer.

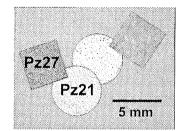

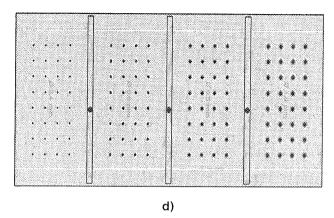

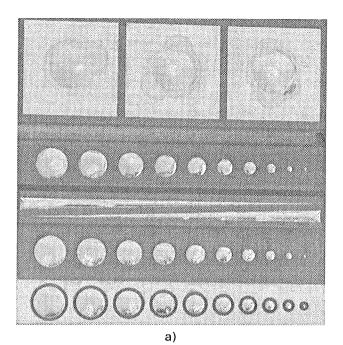

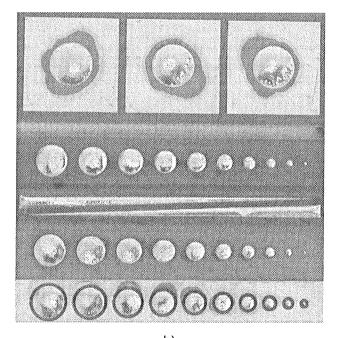

Ceramic thick films are a very promising alternative. Many processes are possible and have been developed /17/ such as screen-printing, tape-casting, spin or dip coating processes and spray techniques /15//18//19//20//21/ to make piezoelectric thick films (few tens of microns). The three first ones are widely used techniques, in particular for imaging applications. In each case, the samples (generally circular shape) are made directly in final shape and avoid machining, namely lapping, which can represent a critical step where micro-cracks or breakdown can appear. The tapes can be used to manufacture thin self-supported disks as shown on Figure 7.

Figure 7: Tape-casted self supported disk photographs. (a) (b) from Ferroperm piezoceramics (Denmark), (c) from Laboratoire de Céramique (EPFL, Switzerland)

Table 2 summarises several representative characteristics of self-supported samples where properties are slightly lower than those of bulk ceramics (in particular k<sub>1</sub>) but their actual performance allow to integrate these elements in transducers which deliver satisfying properties.

Table 2: Properties of self supporting samples made by tape-casting.

| Materials    | ε <sub>33</sub> <sup>8</sup> /ε <sub>0</sub> | k <sub>t</sub> (%) | <b>f</b> <sub>a</sub> (MHz) | ρ (kg/m³) | δ <sub>m</sub> (%) | ref  |

|--------------|----------------------------------------------|--------------------|-----------------------------|-----------|--------------------|------|

| Pz21 (PNNZT) | 1920                                         | 43                 | 33.9                        | 7420      | 4.7                | [22] |

| Pz29 (PZT)   | 1035                                         | 35.5               | 34.1                        | 6900      | 6.0                | [22] |

| PZT          | 675                                          | 43                 | 46                          | -         | 3.6                | [23] |

$\epsilon_{33}$ S/ $\epsilon_{0}$ : clamped dielectric constant;  $k_{t}$ : thickness coupling factor;  $f_{a}$ : antiresonant frequency;  $\rho$ : density;  $\delta_{m}$ : mechanical losses.

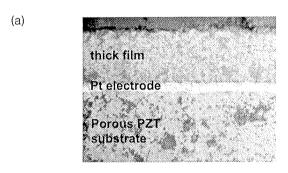

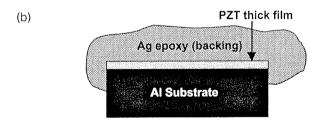

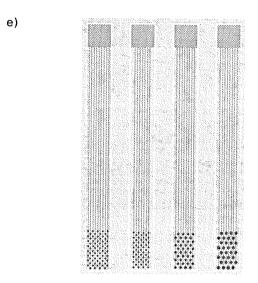

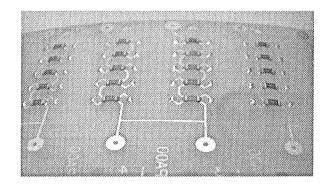

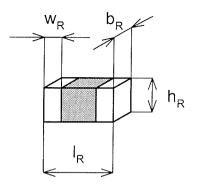

The substrates used for the deposited thick films can be used in two ways. First, the substrate can be chosen to be used directly as a backing for the transducer /24/. Many conditions are necessary for this in terms of sintering temperature (for the thick films) and acoustical properties for the transducer. Porous PZT can be a good choice (Figure 8(a)). This method leads to an integrated device. Secondly, the substrate can be chosen only as an intermediate material. For example, The PZT thick film is deposited on an aluminium substrate (Figure 8(b)) /25/. On the other side, epoxy resin loaded with Ag powder is added as the future backing. Finally, the Al substrate is etched and a new electrode is deposited on the front face of the thick film. This method allows to optimise the choice of these two materials for the future transducer. For these two cases, properties of the piezoelectric thick films are given in Table 3 where the performance obtained can be relatively high, but the reproducibility remains an important problem to be solved. Moreover, the choice of the bottom electrode material and thickness can also greatly influence the final properties.

Figure 8: (a) Cross section of optical microscope photograph of screen-printed PZT thick film on Porous PZT substrate from JSI - Slovenia, (b) screen-printing with intermediate substrate.

Different types of piezocomposites have also been developed for high frequency applications /26-41/, namely 1-3 connectivity including fibres and hollow spheres, as well as curved films.

## 4. Transducer fabrication and performance

#### 4.1. Transducer fabrication

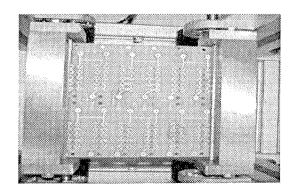

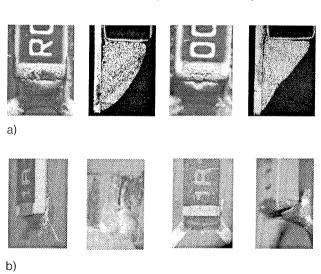

A fabrication technique, described by Lockwood et al. /42/, has allowed to increase significantly the sensitivity of focused transducers, for centre frequencies around 50 MHz, compared to the more classical polymer-based devices. This method has been applied to both ceramic and single crystals. First, bulk ceramic is bonded on a malleable substrate (typically conductive epoxy layer). Ceramic is then lapped to required thickness (generally few tens of microns). The third step is the lapping of the substrate generally to around 100 microns and machining of the structure to final diameter. The two-layer composite is then heated and pressed into a spherically shaped well. The diameter of the well is the focal distance of the transducer. The shell is cooled and removed from the well. Finally, an attenuating backing is added. Two possibilities exist for focusing. The first is the use of a spherically-shaped active element (Figure 9(a)), the second is the addition of lens (Figure 9(b)).

## 4.2. Transducer performance: overview of published results

The two next Tables (Tables 4 and 5) give an overview of published results on high frequency transducers using materials and/or process described in previous sections. Table 4 specifies essentially the characteristics (fabrication process, dimensions or material used) while Table 5 gives the corresponding performance such as bandwidth and sensitivity /44//33//45//25/ (if authors give these values). Concerning the sensitivity, the comparison between values is not always possible since the definition used by different authors is not identical.

| Table 3: Properties c | f screen-printed | ' samples on | ditterent substrates. |

|-----------------------|------------------|--------------|-----------------------|

|-----------------------|------------------|--------------|-----------------------|

| material | process         | substrate | <b>e</b> (μm) | $\epsilon_{33}$ S/ $\epsilon_{0}$ | <b>v</b> <sub>i</sub> (m/s) | k <sub>t</sub> (%) | δ <sub>e</sub><br>(%) | δ <sub>m</sub> (%) | <b>Z</b> (MRa) | ref  |

|----------|-----------------|-----------|---------------|-----------------------------------|-----------------------------|--------------------|-----------------------|--------------------|----------------|------|

| PZT/PGO  | Screen-printing | PZT       | 35.5          | 334                               | 3240                        | 47                 | 4.7                   | 4.8                | -              | [24] |

| PZT/PGO  | Screen-printing | $Al_2O_3$ | 39            | 342                               | 3940                        | 39.7               | 2.0                   | 1.5                | -              | [24] |

| PZT      | Spin coating    | Al        | 20            | 220                               | 3950                        | 24.4               | -                     | -                  | 21.8           | [25] |

$e_{33}^{S}/\epsilon_{0}$ : clamped dielectric constant;  $v_{l}$ : longitudinal wave velocity;  $k_{t}$ : thickness coupling factor;  $\delta_{e}$ : dielectric losses;  $\delta_{m}$ : mechanical losses;  $\mathbf{Z}$ : acoustic impedance.

Figure 9: Cross-sections of schematic representation of press&lens-focused transducers.

Table 4: Overview of published results on high frequency transducers (part 1).

| Material                        | e<br>(μm) | f <sub>c</sub> (MHz) | shaping      | F <sub>#</sub> /F (mm)                         | <b>Z</b> ₅(MRa)-<br>material | <b>Z<sub>m1</sub>(MRa)</b> -<br>material | <b>Z<sub>m2</sub>(MRa)-</b><br>material |

|---------------------------------|-----------|----------------------|--------------|------------------------------------------------|------------------------------|------------------------------------------|-----------------------------------------|

| <b>P(VDF-TrFE)</b> [16]         | 17        | 34                   | prefocused   | 2.7/6                                          | 15 — Ag epoxy                | no                                       | no                                      |

| PVDF[33]                        | 9         | 48.1                 | prefocused   | 2-3/-                                          | 3.15 -pure epoxy no          |                                          | no                                      |

| LiNbO <sub>3</sub> crystal [44] |           | 78                   | prefocused   | prefocused $2/-$ 5.9 – Ag epoxy 7.3 – Ag epoxy |                              | 2.6 - parylene                           |                                         |

| LiNbO <sub>3</sub> crystal [33] | 60        | 44.5                 | Lens (epoxy) | 2-3/-                                          | 5.9 — Ag epoxy               | 7.3 — Ag epoxy                           | no                                      |

| LiNbO <sub>3</sub> crystal [45] | -         | 200                  | prefocused   | 1.15/0.8                                       | 4.3 — Ag epoxy               | no                                       | no                                      |

| PT ceramic [33]                 | 32        | 45.1                 | prefocused   | 2-3/-                                          | 5.9 — Ag epoxy               | 3- parylene                              | no                                      |

| Fiber composite [34]            | 32        | 31                   | prefocused   | -/17.5                                         | Porous polymer               | no                                       | no                                      |

| PT hollow sphere [41]           | 70-90     | 39.8                 | -            | -/1.43                                         | 6 - Ag epoxy                 | parylene                                 | no                                      |

| PZT thick film [25]             | -         | 72                   | prefocused   | -/2.8                                          | Ag epoxy                     | no                                       | no                                      |

e: thickness of the piezoelectric material;  $f_c$ : transducer centre frequency; F: focal distance;  $F_{\#}$ : f-number;  $Z_b$ : acoustic impedance of the backing- corresponding material;  $Z_{m1}$  and  $Z_{m2}$ : acoustic impedances of the first and second matching layers – corresponding material;

In these nine high frequency transducers, a wide range of centre frequencies is observed (between 31 and 200 MHz). The press-focused process is essentially used. A majority of transducers have been designed to have a fnumber between 2 and 3. With PT hollow sphere, this fnumber is lower. For backing material, epoxy loaded with silver particles is mainly used. For matching layers, technology takes a very important place and generally only one matching layer is added. These matching layers are often

in parylene which allows uniform and repeatable deposition of controlled-thickness layers.

In accordance with properties of piezoelectric materials, LiNbO<sub>3</sub> and PT based single-element transducers deliver best performance corresponding to a good trade-off between resolution and sensitivity. Press-focused process delivers better performance than lens-focused process /44/. Attenuation due to various lens thickness decreases

Table 5: Overview of published results of high frequency transducers (part 2).

| Material                        | <b>D</b> (mm) | tuning | <b>BW</b> (%) | AR (μm) | <b>LR</b> (μm) | IL (dB) |

|---------------------------------|---------------|--------|---------------|---------|----------------|---------|

| <b>P(VDF-TrFE)</b> [16]         | 2.2           | no     | 70            | 51      | -              | -       |

| PVDF [33]                       | 3             | no     | 118           | -       | -              | -45.6   |

| LibO <sub>3</sub> crystal [44]  | 3             | yes    | 73            | -       | -              | -13.5   |

| LiNbO <sub>3</sub> crystal [33] | 3             | yes    | 74            | -       | _              | -21.3   |

| LiNbO <sub>3</sub> crystal [45] | 0.7           | -      | 22            | 12      | 14             | -18     |

| PT ceramic [33]                 | 3             | yes    | 47            | _       | -              | -23.7   |

| Fiber composite [34]            | 5             | no     | 118           | -       | -              | -29.3   |

| PT hollow sphere [41]           | 2.            | no     | 33            | -       | -              | -20.1   |

| PZT thick film [25]             | 1             | no     | 52            | 20      | 295            | -46     |

D: Aperture; tuning: addition or not of a self inductor and a transformer; BW: bandwidth at -6dB; AR: axial resolution (-6dB); LR: lateral resolution (-6dB); IL: Insertion loss.

the sensitivity (around -6dB for LiNbO<sub>3</sub> transducers /44/) even if bandwidth is slightly increased. Finally, the transducer (LiNbO<sub>3</sub> based) with two matching layers (Ag epoxy and parylene) gives, as expected, the highest performance.

## 4.3 Comparison of transducer performance.

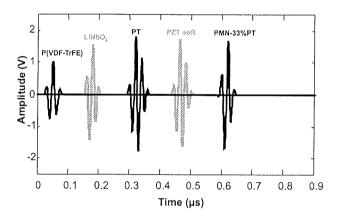

Electroacoustic behaviour of transducers includes electrical input impedance that will govern energy transfer between the imaging system and the transducer, pulse-echo response whose amplitude is linked to sensitivity and duration to axial resolution, and frequency response equal to the Fourier transform of pulse-echo response, which defines centre frequency and bandwidth. All these curves can be predicted with the assumption of single axis vibration, using equivalent electrical circuits such as KLM /10/ /46/ or others /47/. All transducer layers are taken into account as well as electrical elements such as electrical matching and cables. Finite element methods are also available /48/ /49/ in cases where no assumptions can be made on acoustic modes. Acoustic radiation patterns allow to define lateral resolution, which is high when lateral beam dimensions are low, and acoustic noise level (the off-axis power level measured in dB using the on-axis power level as a reference). The appearance of side lobes tends to increase acoustic noise level. Lateral resolution is responsible for image sharpness and low parasitic lobe levels ensure the absence of artefacts in the lateral direction. Radiation pattern calculations can be performed by applying Huygen's principle (i.e. the transducer surface is assumed to be a series of point-sources, and the pressure radiated at any point is the sum of pressures radiated by each of the point-sources /50/). For simple geometry (circular, annular or rectangular transducers), analytical results have been derived (impulse diffraction theories), and allow more efficient calculations /51/ /52/. Five different piezoelectric materials have been retained for comparison: P(VDF-TrFE) copolymer, LiNbO3 single crystal, lead titanate (PbTiO<sub>3</sub>) ceramic, soft PZT ceramic and finally PMN-PT single crystal. For these simulations, three parameters have been fixed: the transducer centre frequency (50 MHz), the active area of the piezoelectric element (diameter of 3 mm) and the length of the 50 ohms coaxial cable (1.5 m). One matching layer is considered. A self inductor and a transformer are also taken into account. Table 6 gives

all the parameters of piezoelectric materials used for the simulations (values from literature).

The optimisation of transducer performance allows to determine the characteristics /43, 53-56/ of the matching layer (acoustical impedance and thickness), backing (acoustical impedance), value of the self inductor and ratio of the transformer. The performance results are specified in Table 7. These simulations do not take into account focusing by a lens. Impulse responses are represented in Figure 10. Due to low  $k_t$ , the P(VDF-TrFE) based transducer delivers a low sensitivity. The results for the PbTiO3, soft PZT and single crystal (PMN-PT) are similar. The electrical matching allows to compensate for the difference in dielectric constants. The LiNbO3 single crystal delivers a similar bandwidth but a lower sensitivity since the dielectric constant is much lower than that of the three previous materials.

Figure 10: Electroacoustic responses of the five simulated transducers.

### 5. Conclusion

PZT-based thick films are very promising for high frequency ultrasonic transducer applications since their electromechanical properties are high and they are compatible with backing materials. Their performance has been demonstrated in non focused configurations, and current work aims at obtaining curved films in order to focus the beam without use of a lens.

Table 6: Piezoelectric material parameters for high frequency transducer simulations.

| Material                        | <b>k</b> <sub>t</sub> (%) | ε <sub>33</sub> <sup>S</sup> /ε <sub>0</sub> | ρ (kg/m³) | <b>v</b> <sub>I</sub> (m/s) | δ <sub>e</sub> (%) | δ <sub>m</sub> (%) | <b>Z</b> (MRa) |

|---------------------------------|---------------------------|----------------------------------------------|-----------|-----------------------------|--------------------|--------------------|----------------|

| <b>P(VDF-TrFE)</b> [16]         | 33                        | 4.1                                          | 1932      | 2380                        | 6.9                | 4.0                | 4.6            |

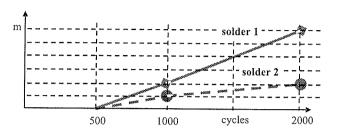

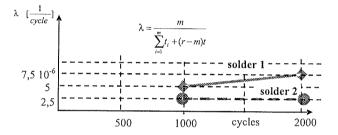

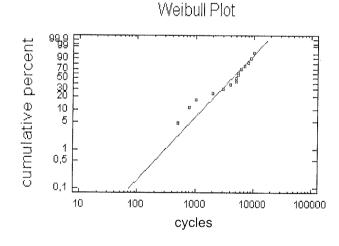

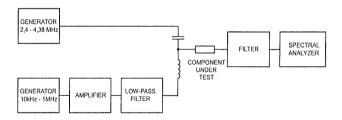

| LiNbO <sub>3</sub> crystal [33] | 49                        | 28                                           | 4640      | 7340                        | 0.1                | 0.01               | 34.1           |

| PT ceramic [33]                 | 49                        | 200                                          | 6900      | 5200                        | 0.9                | 0.83               | 35.9           |

| PZT soft ceramic [57]           | 50                        | 800                                          | 7900      | 4390                        | 2.5                | 2.7                | 34.7           |

| PMN-33%PT [58]                  | 62                        | 712                                          | 8060      | 4645                        | _                  | _                  | 37.4           |

$k_t$ : thickness coupling factor;  $\epsilon_{33}{}^{s}/\epsilon_{0}$ : clamped dielectric constant;  $\rho$ : density;  $v_l$ : longitudinal wave velocity;  $\delta_{e}$ : dielectric losses;  $\delta_{m}$ : mechanical losses; Z: acoustic impedance.

| Material                   | <b>e</b> (μm) | <b>Z</b> ₅(MRa) | Z <sub>m1</sub> (MRa) | $e_{m1}(\times \lambda/4)$ | tuning | <b>BW</b> (%) | IL(dB) |

|----------------------------|---------------|-----------------|-----------------------|----------------------------|--------|---------------|--------|

| P(VDF-TrFE)                | 22.4          | 1.2             | 2                     | 1.5                        | Yes    | 71            | 26     |

| LiNbO <sub>3</sub> crystal | 69.6          | 4.5             | 4                     | 1.2                        | Yes    | 70            | 23.4   |

| PT ceramic                 | 51.0          | 4.3             | 4.3                   | 1.2                        | Yes    | 53            | 19.7   |

| PZT soft ceramic           | 43.1          | 4               | 4.2                   | 1.2                        | Yes    | 54            | 20.6   |

| PMN-33%PT                  | 44.3          | 2.7             | 4                     | 1.0                        | Yes    | 68            | 22     |

Table 7: Design and performance parameters of high frequency single element transducers.

e: thickness of the piezoelectric material;  $Z_b$  and  $Z_{m1}$ : acoustic impedances of the backing and matching layer;  $e_{m1}$ : thickness of the matching layer normalised by a quarter-wavelength; tuning: addition or not of a self inductor and a transformer; BW: bandwidth at -6dB; IL: Insertion loss

### 6. References

- /1./ Sherar, M.D., M. B. Noss, F. S. Foster, Ultrasound backscatter microscopy images the internal structure of living tumour spheroids. Nature, 1987. 330: p. 493-495.

- /2./ Berson, M., J. M. Grégoire, F. Gens, J. Rateau, F. Jamet, L. Vaillant, F. Tranquart, L. Pourcelot, High frequency (20 MHz) ultrasonic devices: advantages and applications. European Journal of ultrasound, 1999. 10: p. 53-63.

- /3./ Ermet, H., M. Vogt. High frequency ultrasonic imaging and its applications in skin. in SPIE Conference on Ultrasonic Transducer Engineering. 1999.

- /4./ Foster, F.S., C. J. Pavlin, K. A. Harasiewicz, D. A. Christopher, D. H. Turnbull, Advances in ultrasound biomicroscopy. Ultrasound in Med. & biol., 2000. 26(1): p. 1-27.

- /5./ Kossof, G., The effects of backing and matching on the performance of piezoelectric ceramic transducers. IEEE Trans. Sonics and Ultrasonics, 1966. 13: p. 20-30.

- /6./ Desilets, C.S., J.D. Fraser, G.S. Kino, The design of efficient broadband piezoelectric transducers. Ultrasonics, 1978. 25: p. 115-125.

- /7./ Inoue, T., M. Ohta, S. Takahashi, Design of ultrasonic transducers with multiple acoustic matching layers for medical application. IEEE Trans. Ultrason. Ferroelect., Freq. Contr, 1987. 34: p. 8-16.

- /8./ Lethiecq, M., F. Levassort, G. Feuillard, L. P. Tran-Huu-Hue, Piezoelectric materials for ultrasonic medical diagnostics. Piezoelectric Materials in Devices, Ed. N. setter, 2002. Chaper 11: p. 211-230.

- /9./ IEEE, Standard on Piezoelectricity ANSI/IEEE Std. 1987.

- /10./ Krimholtz, R., D.A. Leedom, G.L. Matthei, New equivalent circuit for elementary piezoelectric transducers. Electronic letters, 1970. 38: p. 338-339.

- /11./ CENELEC, E.S.P.E.

- /12./ Tran-Huu-Hue, L.P., F. Levassort, F. Vander Meulen, J. Holc, M. Kosec, M. Lethiecq, Preparation and electromechanical properties of PZT/PGO thick films on alumina substrate. Journal of the European Ceramic Society, 2001. 21(10-11): p. 1445-1449.

- /13./ Lukacs, M., T. Olding, M. Sayer, Thickness mode material constants of a supported piezoelectric film. Journal of Applied Physics, 1999. 85(5): p. 2835-2843.

- /14./ Kawaii, H., The piezoelectricity of poly(vinylidene fluoride). Jpn. J. Appl. Phys., 1969. 8: p. 975-976.

- /15./ Foster, F.S., K. A. Harasiewicz, M. D. Sherar, A history of medical and biological imaging with polyvinylidene fluoride (PVDF) transducers. IEEE Trans. Ultrason., Ferroelect., Freq. Contr., 2000. 47(6): p. 1363-1371.

- /16./ Levassort, F., L. P. Tran-Huu-Hue, G. Feuillard, M. Lethiecq, Characterisation of P(VDF-TrFE) material taking into account dielectric relaxation: application to modelling of high frequency transducers. Ultrasonics, 1998. 36(1-5): p. 41-45.

- /17./ Wolny, W.W., Piezoceramic thick films Technology and applications. State of art in Europe. IEEE Int. Symp. Applic. Ferro., 2001: p. 257-262.

- /18./ Gentry, K.L., J.M. Zara, S. Bu, C. Eom, S.W. Smith, *Thick film sol PZT Transducer using dip coating.* IEEE Int. Ultrasonics Symp., 2000. 2: p. 977-980.

- /19./ He, X.-Y., A.-L Ding, X.-S. Zheng, P.-S. Qiu, W.-G. Luo, Preparation of PZT(53/47) thick films deposited by a dip-coating process. Microelectronic Engineering, 2003. 66: p. 865-871.

- /20./ Kobayashi, M., T. R. Olding, L. Zou, M. Sayer, C. K. Jen, A. U. Rehman, Piezoelectric thick film ultrasonic transducers fabricated by spray technique. IEEE Int. Ultrasonics Symp., 2000. 2: p. 985-989.

- /21./ Thiele, E.S., D. Damjanovic, N. Setter, Processing and properties of screen-printed lead zirconate titanate piezoelectric thick films on electroded silicon. J. Am. Ceram. Soc., 2000. 84(12).

- /22./ Levassort, F., L. P. Tran-Huu-Hue, M. Lethiecq, T. Bove, W. W. Wolny, New piezoceramics films for high resolution medical imaging applications. IEEE Int. Ultrasonics Symp., 2000. 2(6): p. 1125-1128.

- /23./ Thiele, E.S., N. Setter, Lead zirconate titanate particle dispersion in thick-film ink formulations. J. Am. Ceram. Soc., 2000. 83(6)

- /24./ Kosec, M., J. Holc, F. Levassort, L. P. Tran-Huu-Hue, M. Lethiecq, Screen-printed Pb(Zr,Ti)O3 thick films for ultrasonic medical imaging applications. Proc. 34th Int. Symp. on Microelectronics, 2001: p. 195-200.

- /25./ Lukacs, M., M. Sayer, F. S. Foster, Single element high frequency (>50 MHz) PZT sol gel composite ultrasound transducers. IEEE Trans. Ultrason., Ferroelect., Freq. Contr., 2000. 47(1): p. 148-159.

- /26./ Newnham, R.E., D. P. Skinner, L. E. Cross, connectivity and piezoelectric-pyroelectric composites, Mat. Res. Bull., 1978. 13: p. 525-536.

- /27./ Savakus, H.P., K. A. Klicker, R. E. Newnham, PZT-Epoxy piezoelectric transducers: a simplifiled fabrication procedure. Mat. Res. Bull., 1981. 16: p. 677-680.

- /28./ Janas, V.F., A. Safari, Overview of fine-scale piezoelectric ceramic/polymer composite processing. 1995. 78(11): p. 2945-2955.

- /29./ Su, B., D. H. Pearce, T. W. Button, Routes to net shape electroceramic devices and thick films. J. Eur. Ceram. Soc., 2001. 21: p. 2005-2009.

- /30./ Meyer Jr, R.J., P. Lopath, S. Yoshikawa, T. R. shrout, High frequency 1-3 composite transducers fabricated from alkoxide-derived PZT fibers. IEEE Int. Ultrasonics Symp., 1997: p. 915-918.

- /31./ Jadidian, B., V. Janas, A. safari, J. French, G. Weitz, J. Luke, R. Cass, Development of fine scale plezoelectric ceramic/polymer composites via incorporation of fine PZT fibers. IEEE Int. Ultrasonics Symp., 1996: p. 31-34.

- /32./ Meyer Jr, R.J., T. R. Shrout, S. Yoshikawa, Development of ultra-fine scale piezoelectric fibers for use in high frequency 1-3 transducers. IEEE Int. Ultrasonics Symp., 1996: p. 547-550.

- /33./ Snook, K.A., J.-Z Zhao, C. H.-F. Alves, J. M. Cannata, W.-H. Chen, R. J. Meyer, T. A. Ritter, K. K. Shung, Design, Fabrication, and evaluation of high frequency, single-element transducers incorporating different materials. IEEE Trans. Ultrason., Ferroelect., Freq. Contr., 2002. 49(2): p. 169-176.

- /34./ Li, K., H. L. W. Chan, C. L. Choy, Samarium and manganese-doped lead titanate ceramic fiber/epoxy 1-3 composite for high-frequency transducer application. IEEE Trans. Ultrason., Ferroelect., Freq. Contr., 2003. 50(10): p. 1371-1376.

- /35./ Chan, H.L.-W., K. Li, C.-L Choy, Piezoelectric ceramic fibre/ epoxy 1-3 composites for high-frequency ultrasonic transducer applications. Materials Science and Engineering B, 2003. 99: p. 29-35.

- /36./ Ritter, T.A., T. R. Shrout, R. Tutwiler, K. K. Shung, A 30-MHz piezo-composite ultrasound array for medical applications. IEEE Trans. Ultrason., Ferroelect., Freq. Contr., 2002. 49(2): p. 217-230.

- /37./ Kwon, S., W. Hachenberger, P. Rehrig, K. Snook, S. Rhee, T. R. Shrout, Ceramic/polymer 2-2 composites for high frequency transducers by Tape-casting. IEEE Int. Ultrasonics Symp., 2003; p. 366-369.

- /38./ Liu, R., D. knapik, K. A. Harasiewicz, F. S. Foster, Fabrication of 2-2 Piezoelectric composites by Interdigital Pair Bonding. IEEE Int. Ultrasonics Symp., 1999; p. 973-976.

- /39./ Levassort, F., M. Lethiecq, D. Certon, F. Patat, A matrix method for modeling electroelastic moduli of 0-3 piezo-composites. IEEE Trans. Ultrason. Ferroelect., Freq. Contr, 1997. 44(2): p. 445-452.

- /40./ Levassort, F., M. Lethiecq, R. Desmare, L. P. Tran-Huu-Hue, Effective electroelastic moduli of 3-3(0-3) piezocomposites. IEEE Trans. Ultrason. Ferroelect., Freq. Contr, 1999. 46(4): p. 1028-1034.

- /41./ Meyer Jr, R.J., R. E. Newnham, S. Alkoy, T. Ritter, J. Cochran Jr, Pre-focused lead titanate >25 MHz single-element transducers from hollow spheres. IEEE Trans. Ultrason., Ferroelect., Freq. Contr., 2001. 48(2): p. 488.

- /42./ Lockwood, G.R., D. H. Turnbull, F. S. Foster, Fabrication of spherically shaped ceramic transducers. IEEE Trans. Ultrason., Ferroelect., Freq. Contr., 1994. 41(2): p. 231-235.

- /43./ Chen, W.H., P. J. Cao, E. Maione, T. Ritter, K. K. shung, Optimization of pulse transmission in a high frequency ultrasound imaging system. 2001. IEEE Int. Ultrasonics Symp.: p. 995-998

- /44./ Cannata, J.M., T. A. Ritter, W.-C. Chen, R. H. Silverman, K. K. Shung, Design of efficient, broadband single-element (20-80 MHz) ultrasonic transducers for medical imaging applications. IEEE Trans. Ultrason., Ferroelect., Freq. Contr., 2003. 50(11): p. 1548-1557.

- /45./ Knapik, D.A., B.Starkoski, C. J. Pavlin, F. S. Foster, A 100-200 MHz ultrasound biomicroscope. IEEE Trans. Ultrason., Ferroelect., Freq. Contr., 2000. 47(6): p. 1540-1549.

- /46./ Van Kervel, S.J.H., J.M. Thijssen, A calculation scheme for the optimum design of ultrasonic transducers. Ultrasonics, 1983. 21: p. 134-140.

- /47./ Lockwood, G.R., F. S. Foster, Modeling and optimization of high-frequency ultrasound transducers. IEEE Trans. Ultrason., Ferroelect., Freq. Contr., 1994. 41(2): p. 225-230.

- /48./ Assaad, J., B. Dubus, B. Hamonic, J.N. Decarpigny, J.C. Debus, Finite element modelling of ultrasonic transducers using the ATILA code. Proceedings of Ultrasonics International, 1991: p. 371-374.

- /49./ Marechal, P., F. Levassort, L. P. Tran-Huu-Hue, M. Lethiecq, Electro-acoustic response at the focal point of a focused transducer as a function of the acoustical properties of the lens. Proc. 5th World Congress on Ultrasonics, 2003: p. 535-538.

- /50./ Kino, G.S., Acoustic waves: devices imaging and analog signal processing. 1987: processing Prentice-Hall Inc Englewood Cliffs New Jersey. Chap. 3.

- /51./ Penttinen, A., M. Luukkala, The impulse response and pressure nearfield of a curved ultrasonics radiators. J. Phys. D, 1976. 9: p. 1547-1557.

- /52./ Selfridge, A.R., G.S. Kino, B.T. Khury-Yakub, A theory for the radiation pattern of a narrow strip acoustic transducer. Appl. Phys. Lett., 1980. 37: p. 35-36.

- /53./ Thijssen, J.M., W. A. Verhoef, M. J. Cloostermans, Optimisation of ultrasonic transducers. Ultrasonics, 1985: p. 41-46.

- /54./ Rhyne, T.L., Computer optimisation of transducer transfer using constraints on bandwidth, ripple and loss. IEEE Trans. Ultrason., Ferroelect., Freq. Contr., 1996. 43(6): p. 1136-1149.

- /55./ Mc Keighen, R.E., Design guidelines for medical ultrasonic arrays, S.P.I.E., 1998. 3341: p. 2-18.

- /56./ Desmare, R., L.P. Tran Huu Hue, F. Levassort, M. Lethiecq, Optimisation method for ultrasonic transducers used in medical imaging. Journal Revista de Acustica, 2003. 33.

- /57./ Felix, N., L. P. Tran-Huu-Hue, L. Walker, C. Millar, M. Lethiecq, The application of high permittivity piezoelectric ceramics to 2D array transducers for medical imaging. Ultrasonics, 2000. 38: p. 127-130.

- /58./ Zhang, R., B. Jiang, W. Cao, Orientation dependence of piezoelectric properties of single domain 0.67Pb(Mn1/3Nb2/ 3)03-0.33PbTiO3 crystals. Appl. Phys. Lett., 2003. 82(21): p. 3737-3739.

Marc Lethiecq, LUSSI-EIVL, BP 3410, F-41034 Blois-cedex lethiecq@univ-tours.fr

Franck Levassort and Louis-Pascal Tran-Huu-Hue. GIP ULTRASONS / LUSSI - CNRS FRE 2448 François Rabelais University - Tours, France

Prispelo (Arrived): 14. 09. 2005; Sprejeto (Accepted): 28. 10. 2005

## **DECISION DIAGRAMS AND DIGITAL TEST**

Raimund Ubar

Tallinn University of Technology, Tallinn, Estonia

INVITED PAPER

MIDEM 2005 CONFERENCE

14.09.2005 - 16.09.20045, Bled, Slovenia

Key words: testing, testing of digital systems, decision diagrams, hierarchical modeling, high level decision diagrams, vector descision diagrams

Abstract: The most important question in testing today's complex digital systems is: how to improve the testing quality at continuously increasing complexities of systems? Two main trends can be observed: defect-orientation to increase the quality of testing, and high-level modelling to reduce the complexity problems of diagnostic analysis. Both trends can be joined in the hierarchical approach. Decision Diagrams (DD) serve as a good tool for hierarchical modelling and diagnostic analysis of digital systems. Traditional Binary Decision Diagrams are well known for working with logic level. New generalizations of BDDs in a form of High-Level DDs and Vector DDs as efficient tools for test generation and fault simulation of complex digital systems are discussed in the paper. Finally, two examples of hierarchical test generation tools based on DDs together with corresponding experimental results are given.

## Odločitveni diagrami in digitalno testiranje

Kjučne besede: testiranje, testiranje digitalnih sistemov, odločitveni diagrami, hierarhično modeliranje, odločitveni diagrami na višjem nivoju, vektorski odločitveni diagrami

Izvleček: Eno najpomembnejših današnjih vprašanj pri testiranju digitalnih sistemov je, kako izboljšati zanesljivost testiranja ob stalnem naraščanju kompleksnosti sistemov? Opažamo dvae glavni smeri: eno, ki je usmerjena k odkrivanju napak in drugo, ki obsega modeliranje na višjem nivoju, kar zmanjša zapletenost diagnostične analize. Obe smeri lahko združimo v hierarhični pristop. Odločitveni diagrami ( DD ) služijo kot dobro orodje za hierarhično modeliranje in diagnostično analizo digitalnih sistemov. Tradicionalni binarni odločitveni diagrami ( BDD ) so dobro poznani pri delu z logičnimi nivoji. V prispevku obravnavamo nove posplošitve BDD v obliki DD na višjem nivoju in vektorske DD kot učinkovita orodja za tvorbo testov in simulacijo napak pri kompleksnih digitalnih sistemih. Na koncu podamo dva primera orodja za tvorbo hierarhičnih testov na osnovi DD skupaj z ustreznimi eksperimentalnimi rezultati

### 1. Introduction

Test generation for digital systems encompasses three activities: selecting a description method, developing a fault model and generating tests to detect the faults covered by the fault model. The efficiency of test generation (quality, speed) is highly depending on the description method and fault models which have been chosen.

As the complexity of digital systems continues to increase, the gate level test generation methods have become obsolete. Other approaches based mainly on higher level functional and behavioral methods are gaining more popularity /1-3/. However, the trend towards higher level modelling moves us even more away from the real life of defects and, hence, from accuracy of testing. To handle adequately defects in deep-submicron technologies, new fault models and defect-oriented test methods should be used. On the other hand, the defect-orientation is increasing even more the complexity. To get out from the deadlock, the two opposite trends - high-level modelling and defect-orientation - should be combined into hierarchical approaches. The advantage of hierarchical approaches compared to high-level functional modelling lies in the possibility of constructing test plans on higher levels, and modelling faults on more detailed lower levels.

The drawback of traditional multi-level and hierarchical approaches to digital test lies in the need of different dedicated languages and models for different levels. Uniform methods for hierarchical diagnostic modelling of digital systems can be developed by using Decision Diagrams (DD) /4-9/. Binary DDs (BDD) have found already very broad applications in design and test on the logic level /4-5/. A special class of BDDs, Structurally Synthesized BDDs (SSBDD) can be used to represent gate-level structural faults directly in the graph model /6,7/. Recent research has shown that generalization of BDDs for higher levels provides a uniform model for both gate and RT level or even behavioral level test generation /8,9/.

The disadvantage of the traditional hierarchical test approaches is the use of gate-level stuck-at fault (SAF) model. It has been shown that high SAF coverage cannot quarantee, high quality of testing /10/. The types of faults that can be observed in a real gate depend not only on the logic function of the gate, but also on its physical design. These facts are well known but usually, they have been ignored in engineering practice. In earlier works on layout-based test techniques /11,12/ a whole circuit having hundreds of gates was analysed as a single block. Such an approach is computationally expensive and highly impractical as a method of generating tests for real VLSI designs.

In this paper, we present, first, in Section 2 a method for mapping faults from lower levels to higher levels. For this purpose the concept of functional fault model is used. Thereafter, for hierarchical diagnostic modelling of digital systems, DDs are presented. In Section 3 SSBDDs are described for logic level test generation, and in Section 4 the use of higher level DDs for test generation is discussed. Some experimental data are presented in Section 5 to illustrate the efficiency of the described hierarchical approach. Section 6 concludes the paper.

## 2. Functional fault model in hierarchical test

Consider a Boolean function  $y = f(x_1, x_2, ..., x_n)$  implemented by an embedded component C in a digital circuit. Introduce a Boolean variable d for representing a given physical defect in the component, which may affect the value y by converting the Boolean function f into another faulty function  $y = f^d(x_1, x_2, ..., x_n)$ . Introduce for the block C a generic parametric function

$$y^* = f^*(x_1, x_2, ..., x_n d) = \overline{d} f \vee df^d$$

(1)

as a function of the defect variable d, which describes the behavior of the component simultaneously for both possible fault-free and faulty cases. The solutions of the Boolean differential equation

$$W^d = \frac{\partial y^*}{\partial d} = 1 \tag{2}$$

describe the conditions which activate the defect d on a line y. The parametric modeling of a given defect d by equations (1) and (2) allows us to use the constraints  $W^d = 1$ , either in defect-oriented fault simulation to check if the condition (2) is fulfilled (i.e. if the defect d is tested by the given pattern), or in defect-oriented test generation to solve the equation (2) for testing the defect d. The conditions  $W^d$  allow to map physical defects to logic level. The constraint  $W^d = 1$  defines how a lower level fault d should be activated at a higher level to a given node y.

Table 1: Activating conditions for different defects

| No | Defect                            | Conditions W                                           |

|----|-----------------------------------|--------------------------------------------------------|

| 1  | SAF $x_k \equiv 0$                | $x_k = 1$                                              |

| 2  | SAF $x_k \equiv 1$                | $x_k = 0$                                              |

| 3  | Short between $x_k$ and $x_l$     | $x_k = 1, x_l = 0$                                     |

| 4  | Exchange of lines $x_k$ and $x_l$ | $x_k = 1, x_l = 0, \text{ or } $<br>$x_k = 0, x_l = 1$ |

| 5  | Delay fault on the line $x_k$     | $x_k = 1, x'_k = 0, \text{ or } x_k = 0, x'_k = 1$     |

Table 2: Library defect table for a complex gate AND2,2/NOR2

| i  | Fault $d_i$ | Erroneous function $f^{di}$   | Input patterns $t_j$ |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |

|----|-------------|-------------------------------|----------------------|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|

|    | Fault $a_i$ | Enoneous function j           | 0                    | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9  | 10 | 11 | 12 | 13 | 14 | 15 |

| 1  | B/C         | not((B*C)*(A+D))              |                      |   |   | 1 |   |   |   |   |   |    |    | 1  | 1  | 1  |    |    |

| 2  | B/D         | not((B*D)*(A+C))              |                      |   |   | 1 |   |   |   |   |   |    |    | 1. | 1  |    | 1  |    |

| 3  | B/N9        | B*(not(A))                    | 1                    | 1 | 1 |   |   |   |   | 1 | 1 | 1. | 1  |    |    |    |    |    |

| 4  | B/Q         | B*(not(C*D))                  | 1                    | 1 | 1 |   |   |   |   |   | 1 | 1  | 1  |    | 1  | 1  | 1  |    |

| 5  | B/VDD       | not(A+(C*D))                  |                      |   |   |   |   |   |   |   | 1 | 1  | 1  |    |    |    |    |    |

| 6  | B/VSS       | not(C*D)                      |                      |   |   |   |   |   |   |   |   |    |    |    | 1  | 1  | 1  |    |

| 7  | A/C         | not((A*C)*(B+D))              |                      |   |   | 1 |   |   |   | 1 |   |    |    |    | 1  | 1  |    |    |

| 8  | A/D         | not((A*D)*(B+C))              |                      |   |   | 1 |   |   |   | 1 |   |    |    |    | 1  |    | 1  |    |

| 9  | A/N9        | A*(not(B))                    | 1                    | 1 | 1 |   | 1 | 1 | 1 |   |   |    |    | 1  |    |    |    |    |

| 10 | A/Q         | A*(not(C*D))                  | 1                    | 1 | 1 |   | 1 | 1 | 1 |   |   |    |    |    | 1  | 1  | 1  |    |

| 11 | A/VDD       | not(B+(C*D))                  |                      |   |   |   | 1 | 1 | 1 |   |   |    |    |    |    |    |    |    |

| 12 | C/N9        | not(A+B+D)+(C*(not((A*B)+D))) |                      | 1 |   |   | 1 | 1 |   |   | 1 | 1  |    |    |    |    |    |    |

| 13 | C/Q         | C*(not(A*B))                  | 1                    | 1 |   | 1 | 1 | 1 |   | 1 | 1 | 1  |    | 1  |    |    |    |    |

| 14 | C/VSS       | not(A*B)                      |                      |   |   | 1 |   |   |   | 1 |   |    |    | 1  |    |    |    |    |

| 15 | D/N9        | not(A+B+C)+(D*(not((A*B)+C))) |                      |   | 1 |   | 1 |   | 1 |   | 1 |    | 1  |    |    |    |    |    |

| 16 |             | D*(not(A*B))                  | 1                    |   | 1 | 1 | 1 |   | 1 | 1 | 1 |    | 1  | 1  |    |    |    |    |

| 17 | N9/Q        | not((A*B)+(B*C*D)+(A*C*D))    |                      |   |   | 1 |   |   |   |   |   |    |    |    |    |    |    |    |

| 18 | N9/VDD      | not((C*D)+(A*B*D)+(A*B*C))    |                      |   |   |   |   |   |   |   |   |    |    |    | 1  |    |    |    |

| 19 | Q/VDD       | SA1 at Q                      |                      |   |   | 1 |   |   |   | 1 |   |    |    | 1  | 1  | 1  | 1  | 1  |

| 20 | Q/VSS       | SA0 at Q                      | 1                    | 1 | 1 |   | 1 | 1 | 1 |   | 1 | 1  | 1  |    |    |    |    |    |

Some examples of the conditions  $W^d$  for different type of defects (where SAF is a particular extreme case) are given in Table 1 (here  $x_k$  is the observable variable, and  $x'_k$  is the variable observed at the previous time moment).

The event of erroneous value of y can be described as dy = 1, where dy means Boolean differential. A functional fault representing a defect d can be described as a couple (dy,  $W^d$ ): at the presence of the physical level defect d, we will have an higher level erroneous signal dy = 1 if the condition  $W^d = 1$  is fulfilled.

The functional fault model  $(dy, W^d)$  allows to use for test generation for any physical defect d traditional stuck-at fault test generators. To generate a test for a defect d, a test pattern should be generated for the stuck-at fault  $y \equiv (1 \oplus y(W^d))$  at the additional condition  $W^d = 1$ . Here  $y(W^d)$  is the expected value of y determined by the condition  $W^d = 1$ .

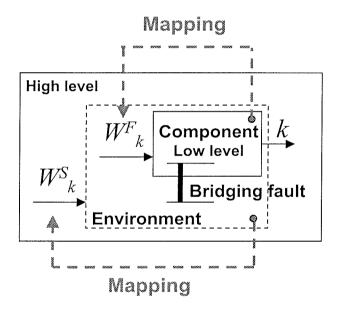

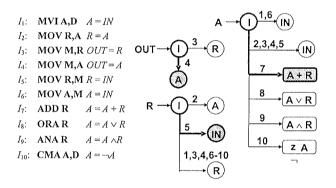

Figure 1: Mapping faults from lower level to higher level

In the described approach we have to characterize all possible defects in all library cells, and represent the results as defect tables or as optimized sets of defect activating

conditions  $W^F = \{W^{d,i}\}$ . The defect characterization may be computationally expensive, but it is performed only once for every library cell. An example of the fault table for the complex gate AND2,2/NOR2 with a function  $y = \neg (AB \ Ú \ CD)$  is presented in Table 2 / 13/.

The defect lists  $W_k^F$  of library components  $C_k$  embedded in the circuit can be extended by additional physical defect lists  $W_k^S$  in the close network environment of the component  $C_k$  to take into account also the wrong behaviour of  $C_k$  influenced by the outside environment (bridging faults, crosstalkings etc.). For these defects additional characterization should be carried out by a similar way as for the library cells.

## 3. Diagnostic modelling of digital systems by BDDs

Decision Diagrams (DD) can serve as a basis for a uniform approach to test generation for mixed-level representations of systems, similarly as we use the Boolean algebra for the plain logic level. In the following it is shown how the traditional logic level test methods can be implemented on Binary Decision Diagrams (BDD) /6,7,14/ as a special class of DDs, and then we generalize the procedures developed for BDDs for a general class of DDs /6,16,17/ to handle the test generation problems at higher levels of systems.

Structurally synthesized BDDs. In 1959 C.Y.Lee introduced a method for representing digital circuits by Binary Decision Programs /18/. In 1976 /14/ and in 1977 /15/ independently the BDDs were introduced for test generation purposes. Today the theory of BDDs is developing quickly /4,5,19/.

In /7,14/ structurally synthesized BDDs (SSBDD) as a special class of BDDs was introduced to represent the topology of gate-level circuits in terms of signal paths. Unlike "traditional" BDDs /4,18/, SSBDDs directly support test generation for gate-level structural faults without explicitly representing the faults. The advantage of SSBDDs is that the library of D-cubes for components is not needed for structural path activization. That's why SSBDD based test generation procedures do not depend on whether the circuit

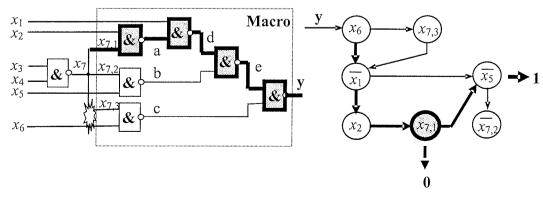

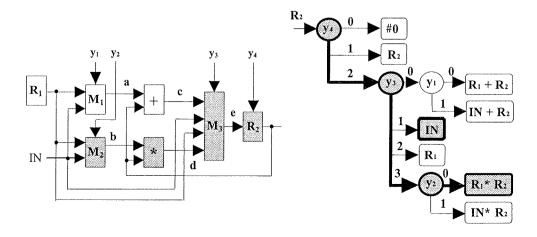

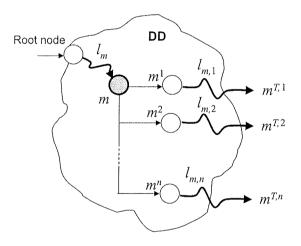

Figure 2: Combinational macro and his SSBDD

is represented on the gate level or on the higher macrolevel whereas the macro means an arbitrary single-output subcircuit of the whole circuit. Moreover, the test generation procedures developed for SSBDDs can be easily generalized for higher level DDs to handle digital systems represented at higher levels /6,16,17/.

The BDD that represents a Boolean function is a directed noncyclic graph with a single root node, where all nonterminal nodes are labelled by Boolean variables (arguments of the function) and have always exactly two successornodes whereas the terminal nodes are labelled by constants 0 or 1. For all nonterminal nodes, a one-to-one correspondence exists between the values of the label variable of the node and the successors of the node. The correspondence is determined by the Boolean function to be represented by the graph.

Denote the variable which labels a node m in a BDD by x(m). We say that a value of the node variable activates the node output edge. According to the value of x(m), one of two output edges of m will be activated. If x(m) = 1 we say 1-edge is activated, or if x(m) = 0 we say 0-edge is activated. A path is activated if all the edges that form this path are activated. The BDD is activated to 0 (or 1) if there exists an activated path which includes both the root node and the terminal node labelled by the constant 0 (or 1).

<u>Definition 3.1.</u> A BDD  $G_y$  with nodes labelled by variables  $x_1, x_2, ..., x_n$ , represents a Boolean function  $y = f(X) = f(x_1, x_2, ..., x_n)$ , if for each pattern of X, the BDD will be activated to the value which is equal to y for the same pattern.

Important property of SSBDDs. SSBDDs differently from traditional BDDs have the following property: each node m in a  $G_y$  which describes a tree-like subnetwork  $N_y$  of the gate-level circuit  $N_y$ , represents a signal path I(m) in  $N_y$ . There is an one-to-one correspondence between the nodes m in a  $G_y$  and the paths I(m) in the corresponding circuit  $N_y$ .

An example of a combinational circuit with a tree-like macro and SSBDD for the macro is presented in Figure 2. For simplicity, the values of variables on edges of the SSBDD are omitted (by convention, the 1-edge is always directed to the right, and the 0-edge is always directed downwards). Also, terminal nodes with constants 0 and 1 are omitted (leaving the SSBDD to the right corresponds always to y =1, and down - to y = 0). Each node is marked by an input variable of the macro. A node with the label  $x_m$  in the SSB-DD represents the signal path through the macro which begins with the input variable  $x_m$ . The node variable is inverted when the path consists of odd number of inverters, and not inverted when the number of inverters is even. For example, the node  $x_{7,1}$  of SSBDD represents the signal path with even number of inverters starting with the line  $x_{7,1}$  through the nodes a,d,e to the output y in the macro (the bold lines in the circuit). The node will in the SSBDD has inverted variable since the corresponding path  $x_1, d, e, y$ consists of odd number of inverters. The fan-out node x7

in the circuit has three branches, and each branch  $x_{7,i}$  (i = 1,2,3) is the beginning of a path which is represented by the node  $x_{7,i}$  in the SSBDD.

From the above described property of the SSBDD, automatic fault collapsing results. Assume a node m with label variable x(m) represents a signal path l(m) in a circuit. Suppose the path l(m) goes through n gates. Then, instead of 2n faults of the path l(m) in the circuit, only 2 faults related to the node variable x(m) should be tested when using the SSBDD model.

Test generation with SSBDDs. Consider a combinational circuit as a network of gates, which is partitioned into interconnected tree-like subcircuits (macros). This is a new higher level (macro-level) representation of the same circuit. Each macro is represented by a SSBDD where each node corresponds to an input of the macro. In the tree-like subcircuits only the stuck-at faults at inputs should be tested. This corresponds to testing all the nodes in each SSBDD. Test generation for a node m in SSBDD, which represents a function y = f(X) of a macro, is carried out by the following procedure  $\frac{19,23}{}$ .

#### Algorithm 1.

- A path I<sub>m</sub> from the root node of SSBDD to the node m is activated.

- 2) Two paths  $I_{m,e}$  consistent with  $I_m$ , where  $e \in \{0,1\}$ , from the neighbors  $e^n$  of  $e^n$  to the corresponding terminal nodes  $e^{T,e}$  are activated.

- 3) For generating a test for a particular stuck-at-e fault  $x(m) \equiv e$ ,  $e \in \{0,1\}$ , the opposite assignment for x(m) is needed:  $x(m) = \overline{e}$ .

- 4) All the values assigned to node variables build the local test pattern T(X,y) (input pattern of the macro) for testing the node m in  $G_y$ .

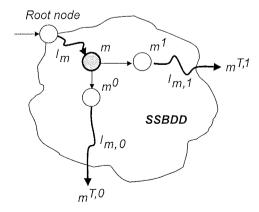

The paths in the SSBDD activated by *Algorithm 1* are illustrated in Figure 3.

Figure 3: Test generation for the node m with SSBDD

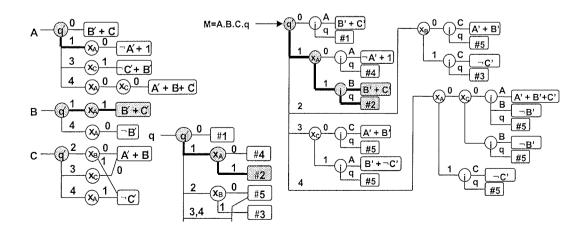

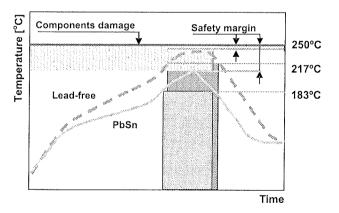

To create the final test pattern in terms of primary inputs of the circuit (network of macros) for the given fault in an node to the terminal node  $m^{T,e}$ .