# GALs - GENERIC ARRAY LOGIC (Part III) (A member of PLDs family)

## Zlatko Bele

KEY WORDS: Programmable logic circuits (PLDs), integrated circuits, Aplication specific integrated circuits (ASIC), EECMOS, Output Logic Macro Cell (OLMC), GAL

ABSTRACT: In previous parts of the article an overview and detailed architecture of GALs has been presented. Part III deals with programming software and hardware for GAL devices as well as programming example. A way of emulating conventional PAL devices with GAL devices is also presented.

# GALi - Generične logične mreže (III.del)

KLJUČNE BESEDE: programabilna logična vezja (PLDs), integrirana vezja, vezja po naročilu (ASIC), EECMOS, izhodne logične makrocelice (OLMC), GAL

POVZETEK: V prvih dveh delih članka je bil podan pregled in podrobna zgradba GAL programabilnih logičnih vezij, tretji del pa opisuje programska in strojna orodja za programiranje GAL vezij skupaj s konkretnim primerom programiranja. Podan je tudi način emulacije konvencionalnih PAL vezij z GAL vezji.

#### 1. INTRODUCTION

Apperance of first PLD devices (bipolar PAL's) falls into early 70's. At that time this devices had a quite difficult time being accepted by system's and board designers due to the lack of good programming software. It was necessary to load each individual fuse location into the devices after extensive analysis of the design requirements. This was a slow and cumbersome process requiring the designer to learn the architecture of many different devices in addition to the fact that logic errors could not be automatically identified.

Development and availability of user-friendly and functional software tools had the main contribution to the tremendous upsurge in the usage of the PLD devices in late 80's.

#### 2. SOFTWARE TOOLS

The most popular early assembler based programming software for PAL devices was PALASM from Monolithic Memories. This assembler allows inputs only as Boolean equations, has a difficult command structure, allows equations only in SOP (sum-of-products) format, works on PAL devices only and has no intelligence i.e. unable to do logic minimization or identify specific device types which will or will not work with a given set of Boolean equations. The most severe restrictions of this type of approach was the inflexbility of the software to work on other vendors devices thus forcing designers to learn many different assemblers in order to have more than one device supplier to choose from.

The development of compiler based software in the early 80's was the response to the need for more flexibility and utility in development tools. The original packages were developed by third-party manufacturers, not device vendors, with the goal of supporting all device types and all manufacturers. This original packages as "CUPL" from Personal CAD systems and "ABEL" from DATA I/O Corp. had the capability of logic equation minimization, macros, truth table and state machine syntax and self-documentation.

The latest advance in the PLD development software has occured in the mid-80's. These programs allow schematic capture using pre-programmed macros in the software which allow a designer to simply create a logic shematic as the input to a translator. The translator converts the graphic representation to a network list that is then compiled to the fuse maps by the software tool. All the other functions of the software such as logic minimization are then available to streamline the design before it is downloaded into a device. The most widely used of these tools are "CAE-1" from Personal CAD systems and "DASH" from DATA I/O.

#### 3. HARDWARE TOOLS

The hardware used to program GAL devices can be divided roughly into two types:

- a) Universal programmers

- b) GAL-only programmers

## a) Universal programmers

In this case "universal" means with respect to PLD devices only, this terminology should not be confused with the broader sense of "universal" programmers, meaning those that program EPROM memories or EPROM arrays in microprocessors as well as PLD's.

In these category of universal type programmers are those from DATA I/O and STAG MICROSYSTEMS as well as many others. These programmers support many different PLD devices, including ECL, CMOS EPROM, standard bipolar PALs and GAL EECMOS device types. These universal programmers also support many advanced functions such as test vectors, register preload, and even automatic chip handler control in a production environment.

#### b) GAL-only programmers

Main advantage of GAL-only programmers is, of course, their low price. Well known vendors of such programmers are QWERTY and PROGRAMMABLE LOGIC TECHNOLOGIES. The QWERTY also supports test vectors and registers preload for full functional testing of GAL devices.

The type of tool choosen should reflect the environment it will be used in. This means that GAL-only programmer could be considered in an operation where GAL only development and small volume production is occuring in a situation where a low-cost evaluation and programming of GALs is necessary. However in a large development lab where many types of PLDs are being evaluated or a high volume production environment where automated handling of devices is necessary, a universal type programmer with chip handler may be more appropriate. A prime consideration should also be the necessary functions of the programer as well. For example altough a 100% programming yield of GAL devices is guaranteed by vendor, test vector and register preload capability is recommended for the designer to verify that the device is doing exactly what was planned.

#### 4. PROGRAMMING PROCESS

Programming GAL device is the process of providing it with so called "JEDEC" file. This file has got its name by the standards organization JEDEC with the representatives from major semiconductor companies on its committees, which has approved a standard for the interchange of PLD data. So JEDEC file is used as the medium of transfer from the development computer environment to that of the hardware device programmer. Included in the file are control bits that determine the status of programming cells, status of security cell, test vectors and data-transsmision checksum. Test vectors, if included, indicate the stimulus and response for a PLD and serve primarily to validate the functionallity of a design source file.

JEDEC file is written into the device by applying a series of specific voltage pulses."Responsibility" of the programmer manufacturer refers to his ability to provide the

correct voltages and timing pulses and make the correct measurements on the outputs, if applicable, for the device

JEDEC file is produced from a design source file which is written in a specific syntax and compiled with a compiler based programming software. As mentioned before one of the most known such a software is that of CUPL from Personal CAD systems.

First what we have to do developing a design source file using CUPL or in general some other development software is to tell the software which type of GAL device will be used. Then entry of some optional informations such as company name, design description, designer name is provided.

The device pinout and pin labels need to be specified next. Convenient names should be used since the software doesn't care what the pin is called as long as we are consistent. Pin definition example is as follows:

```

/ * inputs * /

pin (1,2) = ( A, !B);

/ * outputs * /

pin (18,19) = (Y,!Z);

```

It is also a good idea to specify pin names in a format that is consistent with the actual pin state. In the above definitions, signals A and Y are active high, while B and Z are active low. An eclamation point prefixing label is used to indicate active-low data signals. The use of active-high variation of these signals in subsequent design statements will automatically be resolved by the software compiler.

Entry of logic functions is next. Traditionally, this entry is in the form of Boolean equations. Current revisions of CUPL software allow truthtable, state-macine and shematic-entry formats, as well. In example below a traditional equation-entry format is used to create an AND function on Y (pin 18) and an XOR function on Z (pin 19). Since Z has been defined as an active-low signal, however, function on pin 19 is actually XNOR:

```

/ * logic equations * )

Y = A & B;

Z = !A & B # A & !B;

```

The opeartors used in the CUPL language are "!" for invert, "&" for the AND function and "#" for the OR function. The equations are written exactly as needed. All of the inversions for active-low inputs and outputs will be automatically resolved, a routine procedure for the compiler software. Altough these are simple equations, if they had been complex ones that needed automatic reduction to a specific number of product terms for a given PLD, the software would have performed that reduction, as well.

Next, the CUPL compiler needs to be invoked to process the "source" file. Through compiling process a JEDEC file is produced together with so called "documentation file". The purpose of this file is to provide a

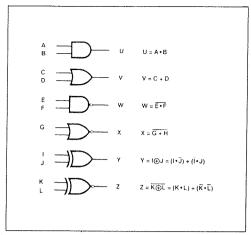

Fig. 1 Basic Logic Gates

hard-copy documentation of the final (reduced) equations, the cell map and chip diagram, if desired.

As an actual example an implementation of the basic logic gates AND, OR, NAND, NOR, and XNOR (see Figure 1) in a GAL16V8 device is presented next.

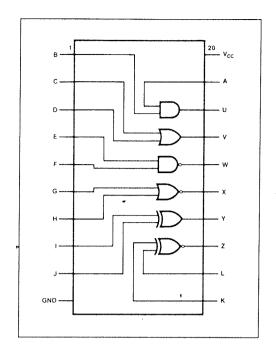

Since 12 inputs and 6 outputs are needed (Figure 2), 2 Output Logic Macrocells (OLMCs) must be configured as dedicated inputs and 6 as dedicated combinational outputs. Programming software automatically handles this task. Active-high or low outputs are no problem either, becouse of the programmable polarity feature of the GAL16V8.

Figure 3 shows a CUPL design input source file as it has to be prepared to program GAL16V8 with basic logic gates from Figure 1.

Once this file is compiled with CUPL compiler a JEDEC file as shown on Figure 4 is produced. Zeros in the cell's field represent active cells.

Detailed and complete cell map or so called 'fuse plot' for mentioned example is presented on Figure 4. As can be seen all inactive cells have to be programmed.

As mentioned, for testing the functionality of the device and design verification a "test vectors" has to provided by means of CUPL simulation file. In this case JEDEC file includes also test vectors. Both files are shown on Figure 5 and Figure 6 respectively.

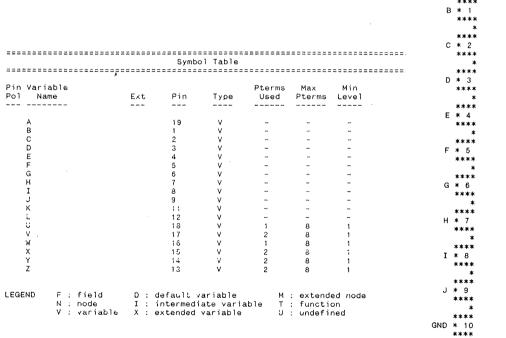

At the end of programming process a 'documentation' file is generated which consists of:

- Expanded product terms (Figure 7)

- Symbol table (Figure 8)

- Chip diagram (Figure 9)

- Fuse plot (allready shown on Figure 4)

The patterning of the GAL device array is done using a parallel programming scheme. This allows the device to be programmed very fast and in fact is less than a second on most programming hardware. This is up to an order of magnitude faster than device using the UV-CMOS approach. During this programming cycle, the logic array, the architecture matrix programming and

Fig. 2 GAL16V8 Basic Gates Pinout

```

Name

Partno

Date

Revision

Designer

Company

Assembly

GATES;

00001;

29/06/87;

01;

ALBERTO;

SGS-THOMSON Microelectronics

PC AT;

PLZN1;

,

/*********************************

/* INPUTS AND

/* INPUTS OR

/* INPUTS NAND

/* INPUTS NOR

/* INPUTS YOP

Pin

Pin

Pin

Pin

[A,B]

[C,D]

[E,F]

[G,H]

[11,12]

/**

Outputs

/* OUTPUT AND

/* OUTPUT OR

/* OUTPUT NAND

/* OUTPUT NOR

/* OUTPUT XOR

/* OUTPUT XNOR

/** Declarations and Intermediate Variable Definitions **/

Logic Equations

= A & B

= C # O

= !(E & F)

= !(G # H)

= I $ J

= !(K $ L)

A N D

O R

N A N D

N O R

X O R

X N O R

```

Fig. 3 CUPL Design Input File

the verify cycle are executed. The verify cycle check programming and margins conservatively such that a minimun data reteintion of 20 years is ensured.

```

Syn

2192 ~ Ac0 2193 x

Pin #15 2052 Pol x 2124 Ac1 x

Pin #19 2048 Pol x 2120 Ac1 -

0000 *******************

0032 *******************

0064 xxxxxxxxxxxxxxxxxxxxxxxxxxxx

0096 XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX

0128 xxxxxxxxxxxxxxxxxxxxxxxxxxxx

1152 xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx

0160 xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx

0192 xxxxxxxxxxxxxxxxxxxxxxxxxxx

0224 xxxxxxxxxxxxxxxxxxxxxxxxxxxx

1248 XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX

Pin #14 2053 Pol - 2125 Ac1 x 1280 -----x----

Pin #18 2049 Pol - 2121 Ac1 x 0256 --x--x-----

0288 xxxxxxxxxxxxxxxxxxxxxxxxxxxxx

1312

0320 XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX

0352 xxxxxxxxxxxxxxxxxxxxxx

1408 xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx

0384 XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX

0416 xxxxxxxxxxxxxxxxxxxxxxxxxxxxx

0448 xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx

0480 xxxxxxxxxxxxxxxxxxxxxxxxxxx

1568 -----

0576 xxxxxxxxxxxxxxxxxxxxxxxxxx

1600 xxxxxxxxxxxxxxxxxxxxxxxxxxx

0608 xxxxxxxxxxxxxxxxxxxxxxxxxxxx

1632

0640 xxxxxxxxxxxxxxxxxxxxxxxxxxxxx

0672 xxxxxxxxxxxxxxxxxxxxxxxxxxxx

1760 xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx

0736 xxxxxxxxxxxxxxxxxxxxxxxxxxxx

Pin #16 2051 Pol x 2123 Ac1 x 0768 -----x---x----

0800 xxxxxxxxxxxxxxxxxx 0080

1824 XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX

0832 xxxxxxxxxxxxxxxxxxxxxxxxxxx

0864 xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx

1920 xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx

0928 xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx

0960 XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX

0992 xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx

LEGEND

X : fuse not blown - : fuse blown

Fia. 4

CUPL Fuse Plot

CSIM Version 2.11b Serial# 5-00001-154

Copyright (C) 1983,1986 Personal CAD Systems, Inc.

CREATED Fri Sep 18 17:15:04 1987

LISTING FOR SIMULATION FILE: GATES.si

1: Name

GATES:

2: Partno

00001;

01;

29/06/87;

3: Revision

4: Date

5: Designer

ALBERTO;

SGS-THOMSON Microelectronics

6: Company

7: Location

PLZN1;

PC AT;

8: Assembly

9: Format

JEDEC:

11: /*

*/

*/

12: /*

BASIC GATES : SIMULATION FILE

13: /*

14. /***********************************

15: /*

Target Devices: G16V8

* /

17:

18:

19: Order: A,B,%2,U,%3,C,D,%2,V,%3,E,F,%2,W,%3,G,H,%2,X,

%3,I,J,%2,Y,%3,K,L,%2,Z;

20:

21:

______

Simulation Results

Ν

Х

Ν

Ν

Α

Α

Ν

0

0

0

0

CD

EF

Э

GH

R

ΙJ

R

KL

R

AB

D

R

Н

00

Н

00

00

Н

0001: 00

00

00

0002: 10

L

10

Н

10

Н

10

L

10

Н

10

01

Н

01

0003: 01

01

Н

01

Н

01

L

0004:

11

```

Fig. 5 CUPL Simulation File

```

2.11b Serial# 5-00001-154

g16v8s Library DLIB-f-23-8

Fri Sep 18 17:07:25 1987

CUPL

Device

Created

Name

Partno

Revision

GATES

00001

01

29/06/87

ALBERTO

Date

Designer

Company

Assembly

Location

*QP20

SGS-THOMSON Microelectronics

*QF2194

*QV4

*G0

*F0

*L0256 1101110111111111111111111111111111

*L2176 11:1111111111111111

*L2176 11:111111111111110

*C2F02

*P 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 :6 17 18 19 20

*V0001 00000000000HHHLLON

*V0002 010101010N10HLHHLIN

*V0003 101010101N01HHHHLON

*V0004 1111111111111HLLLHH1N

```

```

2.11b Serial# 5-00001-154

g16v8s Library DLIB-f-23-8

Fri Sep 18 17:07:24 1987

GATES

CUPL

Device

Created

Name

Partno

Revision

Date

00001

01 29/06/87

ALBERTO

SGS-THOMSON Microelectronics

PC AT

PLZN1

Designer

Company

Assembly

Location

Expanded Product Terms

U =>

A & B

V =>

E & F

X =>

G

# H

Y =>

# !I & J

```

Fig. 6 CUPL JEDEC File with Test Vectors

Fig. 7 CUPL Expanded Product Terms

Fig. 8 CUPL Symbol Table

Fig. 9 CUPL Chip Diagram

#### References:

SGS-THOMSON: Programmable logic manula-GAL products

DATA I/O: Programmable logic

Zlatko Bele,dipl.ing. MIKROIKS d.o.o. Titova 36A 61000 Ljubljana

Prispelo: 05.05.1990 Sprejeto: 20.11.1990