Strokovno društvo za mikroelektroniko elektronske sestavne dele in materiale

# 3.2002

Strokovna revija za mikroelektroniko, elektronske sestavne dele in materiale Journal of Microelectronics, Electronic Components and Materials

INFORMACIJE MIDEM, LETNIK 32, ŠT. 3(103), LJUBLJANA, september 2002

#### **INFORMACIJE**

### **MIDEM**

**3** ° 2002

INFORMACIJE MIDEM

LETNIK 32, ŠT. 3(103), LJUBLJANA,

SEPTEMBER 2002

INFORMACIJE MIDEM

VOLUME 32, NO. 3(103), LJUBLJANA,

SEPTEMBER 2002

Revija izhaja trimesečno (marec, junij, september, december). Izdaja strokovno društvo za mikroelektroniko, elektronske sestavne dele in materiale - MIDEM. Published quarterly (march, june, september, december) by Society for Microelectronics, Electronic Components and Materials - MIDEM.

Glavni in odgovorni urednik

**Editor in Chief**

Dr. Iztok Šorli, univ. dipl.ing., MIKROIKS d.o.o., Ljubljana

Tehnični urednik Executive Editor Dr. Iztok Šorli, univ. dipl.ing., MIKROIKS d.o.o., Ljubljana

Uredniški odbor

Doc. dr. Rudi Babič, univ. dipl.ing., Fakulteta za elektrotehniko, računalništvo in informatiko Maribor

**Editorial Board**

Dr.Rudi Ročak, univ. dipl.ing., MIKROIKS d.o.o., Ljubljana mag.Milan Slokan, univ. dipl.ing., MIDEM, Ljubljana Zlatko Bele, univ. dipl.ing., MIKROIKS d.o.o., Ljubljana

Dr. Wolfgang Pribyl, Austria Mikro Systeme International AG, Unterpremstaetten

mag. Meta Limpel, univ. dipl.ing., MIDEM, Ljubljana

Miloš Kogovšek, univ. dipl.ing., Ljubljana

Prof. Dr. Marija Kosec, univ. dipl. ing., Inštitut Jožef Stefan, Ljubljana

Časopisni svet International Advisory Board Prof. dr. Slavko Amon, univ. dipl.ing., Fakulteta za elektrotehniko, Ljubljana,

PREDSEDNIK - PRESIDENT

Prof. dr. Cor Claeys, IMEC, Leuven

Dr. Jean-Marie Haussonne, EIC-LUSAC, Octeville

Dr. Marko Hrovat, univ. dipl.ing., Inštitut Jožef Stefan, Ljubljana

Prof. dr. Zvonko Fazarinc, univ. dipl.ing., CIS, Stanford University, Stanford † Prof. dr. Drago Kolar, univ. dipl.ing., Inštitut Jožef Stefan, Ljubljana

Dr. Giorgio Randone, ITALTEL S.I.T. spa, Milano

Prof. dr. Stane Pejovnik, univ. dipl.ing., Fakulteta za kemijo in kemijsko tehnologijo, Ljubljana

Dr. Giovanni Soncini, University of Trento, Trento

Prof.dr. Janez Trontelj, univ. dipl.ing., Fakulteta za elektrotehniko, Ljubljana

Dr. Anton Zalar, univ. dipl.ing., ITPO, Ljubljana

Dr. Peter Weissglas, Swedish Institute of Microelectronics, Stockholm

Naslov uredništva Headquarters Uredništvo Informacije MIDEM Elektrotehniška zveza Slovenije Dunajska 10, 1000 Ljubljana, Slovenija

tel.: + 386 (0)1 50 03 489 fax: + 386 (0)1 51 12 217 e-mail: Iztok,Sorli@guest.arnes.si http://paris.fe.uni-lj.si/midem/

Letna naročnina znaša 12.000,00 SIT, cena posamezne številke je 3000,00 SIT. Člani in sponzorji MIDEM prejemajo Informacije MIDEM brezplačno. Annual subscription rate is EUR 100, separate issue is EUR 25. MIDEM members and Society sponsors receive Informacije MIDEM for free.

Znanstveni svet za tehnične vede I je podal pozitivno mnenje o reviji kot znanstveno strokovni reviji za mikroelektroniko, elektronske sestavne dele in materiale. Izdajo revije sofinanci rajo Ministrstvo za znanost in tehnologijo in sponzorji društva.

Scientific Council for Technical Sciences of Slovene Ministry of Science and Technology has recognized Informacije MIDEM as scientific Journal for microelectronics, electronic components and materials.

Publishing of the Journal is financed by Slovene Ministry of Science and Technology and by Society sponsors.

Znanstveno strokovne prispevke objavljene v Informacijah MIDEM zajemamo v podatkovne baze COBISS in INSPEC.

Prispevke iz revije zajema ISI® v naslednje svoje produkte: Sci Search®, Research Alert® in Materials Science Citation Index™

Scientific and professional papers published in Informacije MIDEM are assessed into COBISS and INSPEC databases.

The Journal is indexed by ISI® for Sci Search®, Research Alert® and Material Science Citation Index™

Po mnenju Ministrstva za informiranje št.23/300-92 šteje glasilo Informacije MIDEM med proizvode informativnega značaja.

Grafična priprava in tisk

Printed by

BIRO M, Ljubljana

Naklada Circulation

1000 izvodov 1000 issues

Poštnina plačana pri pošti 1102 Ljubljana

Slovenia Taxe Percue

| UDK621.3:(53+54+621+66), ISSN0352-9045                                                                                                            |     | Informacije MIDEM 32(2002)3, Ljubljana                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------|

| ZNANSTVENO STROKOVNI PRISPEVKI                                                                                                                    |     | PROFESSIONAL SCIENTIFIC PAPERS                                                                                           |

| A.Bürmen, D.Strle, F.Bratkovič,<br>J.Puhan, I.Fajfar, T.Tuma:<br>Robustno načrtovanje analognih integriranih vezij z<br>uporabo kazenskih funkcij | 149 | A.Bürmen, D.Strle, F.Bratkovič,<br>J.Puhan, I.Fajfar, T.Tuma:<br>Penalty Function Approach to Robust Analog IC<br>Design |

| D.Osebik, R.Babič:<br>Možnosti izvedbe adaptivnega FIR sita s<br>programirnimi (FPGA) vezji                                                       | 157 | D.Osebik, R.Babič:<br>The Practicability of Adaptive FIR Digital Filter<br>Implementation with FPGA Circuits             |

| A.Štern, J.Trontelj:<br>Sprejemnik za RFID integrirani bralnik                                                                                    | 167 | A.Štern, J.Trontelj:<br>An On-chip RFID Receiver Stage                                                                   |

| A.Časar, Z.Brezočnik, T.Kapus:<br>Uporaba simboličnega preverjanja modelov pri<br>zaznavanju zatičnih napak v digitalnih vezjih                   | 171 | A.Časar, Z.Brezočnik, T.Kapus:<br>Exploiting Symbolic Model Checking for Sensing<br>Stuck-at Faults in Digital Circuits  |

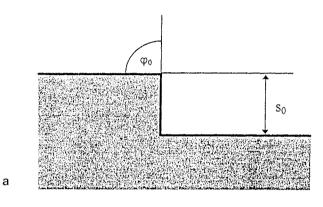

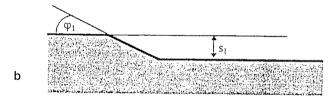

| R.Osredkar, B.Gspan:<br>Pregled planarizacijskih metod v mikroelektronskih<br>tehnologijah                                                        | 181 | R.Osredkar, B.Gspan:<br>Planarization Methods in IC Fabrication<br>Technologies                                          |

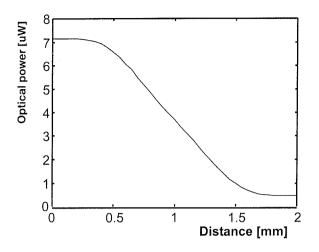

| A.Suhadolnik, J.Petrišič:<br>Merjenje pomika z uporabo odbojnostnih senzorjev<br>z optičnimi vlakni                                               | 186 | A.Suhadolnik, J.Petrišič:<br>Displacement Measurement Using Optical Fiber<br>Reflection Sensors                          |

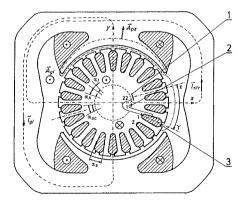

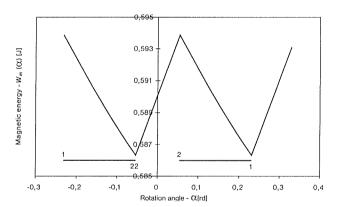

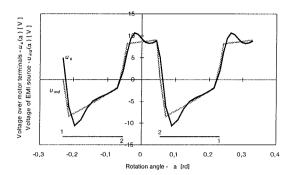

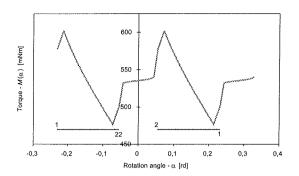

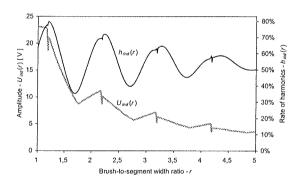

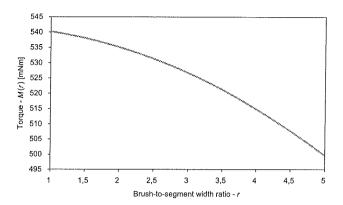

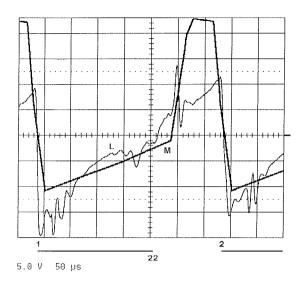

| F.Pavlovčič, J.Nastran:<br>Zmanjšanje EMI kolektorskih motorjev z<br>optimiranjem prekrivanja lamel komutatorja                                   | 189 | F.Pavlovčič, J.Nastran:<br>Reducing EMI of Commutator Motors by Optimizing<br>Brush-to-segment Width Ratio               |

| J.Tušek, M.Uran, M.Vovk:<br>Vpliv velikosti okna med elektrodami na proces<br>elektrouporovnega točkovnega varjenja                               | 194 | J.Tušek, M.Uran, M.Vovk:<br>Influence of Throat Area on the Resistance Spot<br>Welding Process                           |

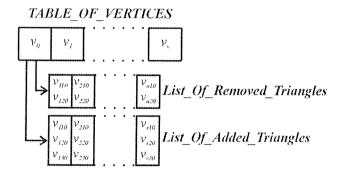

| M.Rojc, Z.Kačič, I.Kramberger:<br>Strojna implementacija jezikovnih virov za uporabo v<br>vdelanih sistemih                                       | 199 | M.Rojc, Z.Kačič, I.Kramberger:<br>Hardware Implementation of Language Resources<br>for Embedded Systems                  |

| I.Ozimek:<br>Optimalna preslikava algoritmov za hitro izvajanje v<br>sistoličnem polju                                                            | 204 | I.Ozimek:<br>Optimal Algorithm Mapping for Fast Systolic Array<br>Implementations                                        |

| J.Stergar, B.Horvat:<br>Napovedovanje simboličnih prozodičnih mej z<br>nevronskimi mrežami                                                        | 213 | J.Stergar, B.Horvat:<br>Prediction of Symbolic Prosody Breaks with Neural<br>Nets                                        |

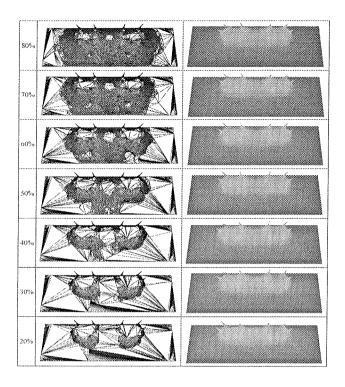

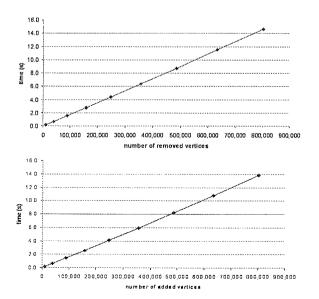

| S.Krivograd, B.Žalik, F.Novak:<br>Modeliranje inženirskih podatkov s poenostavljanjem<br>in rekonstrukcijo trikotniških mrež                      | 219 | S.Krivograd, B.Žalik, F.Novak:<br>Triangular Mesh Decimation and Undecimation for<br>Engineering Data Modelling          |

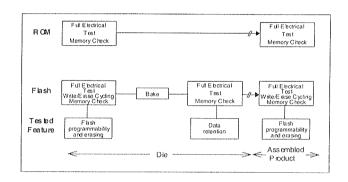

| APLIKACIJSKI ČLANEK                                                                                                                               | 224 | APPLICATION ARTICLE                                                                                                      |

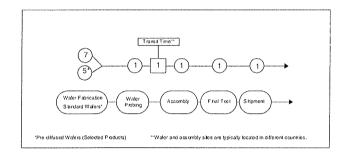

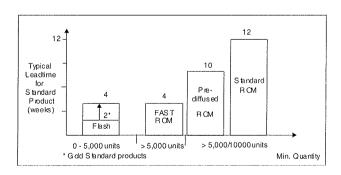

| Izbira med ROM, FASTROM in FLASH<br>spominom za mikrokrmilnik                                                                                     |     | Selecting Between ROM, FASTROM and FLASH for a Microcontroller                                                           |

| A.Paulin:<br>Misli ob štiridesetletnici prvih magistrov                                                                                           | 227 | A.Paulin:<br>Forty Years of Master Science Title - Reflections                                                           |

| MIDEM prijavnica                                                                                                                                  | 228 | MIDEM Registration Form                                                                                                  |

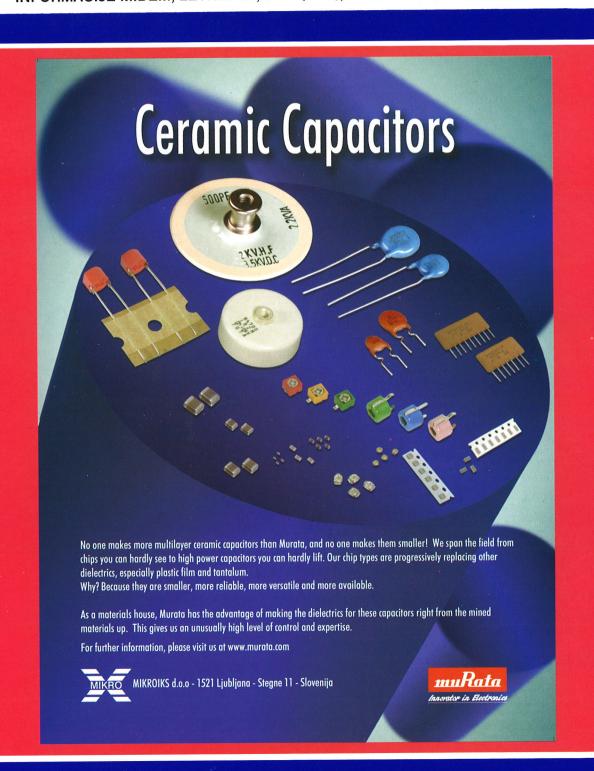

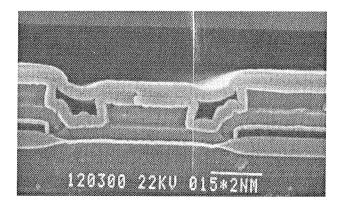

Slika na naslovnici:

Keramične tehnologije iz firme muRata

Front page:

Total Ceramic Technology by muRata

# 38<sup>th</sup> INTERNATIONAL CONFERENCE ON MICROELECTRONICS, DEVICES AND MATERIALS

# and the WORKSHOP on PACKAGING AND INTERCONNECTIONS IN ELECTRONICS

Lipica, October 09. – 11. 2002

REPUBLIC OF SLOVENIA Ministry of Education, Science and Sport

HIPOT-HYB Production of Hybrid Circuits d.o.o. Šentjernej, Slovenia

Slovenia Chapter

Slovenia Section

# PENALTY FUNCTION APPROACH TO ROBUST ANALOG IC DESIGN

Arpad Bűrmen, Drago Strle, Franc Bratkovič, Janez Puhan, Iztok Fajfar, Tadej Tuma University of Ljubljana, Faculty of Electrical Engineering, Ljubljana, Slovenia

Key words: circuit sizing, analog IC, optimization, penalty function, CAD.

Abstract: Automating the robust IC design process is becoming more and more important due to its complexity and decreasing time to market. In order for the circuit to be robust it must satisfy all design requirements across a range of operating conditions and manufacturing process variations. Part of the design process, which is performed by experienced analog IC designers, is automated. A transformation of the robust design problem into a constrained optimization problem by means of penalty functions is presented. The method is illustrated on a robust differential amplifier design problem. The results show that it is capable of sizing a circuit and reaching comparable or to some extent even superior performance to a humanly designed circuit. The method has great potential in parallel processing although it is efficient enough to be executed on a single computer.

# Robustno načrtovanje analognih integriranih vezij z uporabo kazenskih funkcij

Ključne besede: dimenzioniranje vezij, analogna integrirana vezja, optimizacija, kazenske funkcije, računalniško podprto načrtovanje.

Izvleček: Avtomatizacija postopka robustnega načrtovanja IV postaja vse bolj pomembna zaradi zahtevnosti samega postopka in čedalje krajšega časa od začetka načrtovanja do pojave vezja na tržišču. Da je vezje robustno, mora zadostiti vsem načrtovalskim zahtevam za dano območje pogojev delovanja in možnih variacij parametrov postopka izdelave. Predstavljen je avtomatiziran postopek načrtovanja, po zgledu postopka, ki ga izvajajo načrtovalci IV. Podana je preslikava iz problema robustnega načrtovanja v omejen optimizacijski problem. Pri tem se poslužujemo kazenskih funkcij za definicijo kriterijske funckcije. Uporaba metode je prikazana na robustnem načrtovanju diferencialnega ojačevalnika. Rezultati kažejo, da je metoda sposobna poiskati nabor parametrov vezja, ki da primerljivo ali pa do neke mere celo boljše vezje kot ga načrtuje človek. Pristop ima velik potencial v vzporednem računanju, a je kljub temu dovolj učinkovit, da lahko pridemo do sprejemljivih rezultatov z uporabo enega samega računalnika.

#### 1 Introduction

A major issue in analog IC design is robustness. A robust design satisfies the design requirements in all foreseen operating conditions. Furthermore, a robust design must fulfil all design requirements regardless of the expected process variations that may occur during the fabrication of the designed IC. As the time-to-market becomes shorter automating the design process is becoming an important task /1/.

By design requirements we mean circuit characteristics which are of importance to the user of the designed circuit and can be expressed by real values, such as gain, phase margin, gain-bandwidth product, common mode rejection ratio, distortion, output rise time, input impedance, current consumption, etc. A circuit fulfils the design requirements if all circuit characteristics, which are of importance to its user, lie inside some predefined intervals.

An IC must fulfil the design requirements in various operating conditions, which also include various environmental effects. Some common operating conditions whose variations can cause improper circuit operation are power supply voltage, bias currents and load characteristics. The most common environmental condition that affects the operation of a circuit is the temperature. In order to obtain a

robust design the circuit must fulfil the design requirements for a given range of operating conditions.

Process variations are another reason speaking in favour of robust design. IC manufacturers describe process variations by so called corner models. Corner models describe several extreme conditions, which can occur during IC fabrication and result in some extreme circuit behaviour. For a CMOS process usually 4 different corner models are provided to the designer: worst one (WO), worst zero (WZ), worst power (WP) and worst speed (WS). Beside corner models, IC manufacturers also supply a typical mean (TM) model.

If robustness is not foreseen at the design stage and already incorporated in the design, one can expect that only a small number of fabricated ICs will fulfil the design requirements at nominal operating conditions due to process variations. Furthermore only a fraction of these ICs will fulfil the design requirements in all foreseen operating conditions.

In the past a lot of effort was invested in finding efficient means of automated nominal design (/2/, /3/, /6/, /5/, /6/). Nominal design however does not produce robust circuits. The resulting circuits satisfy the design requirements only in nominal operating conditions and for the typ-

ical process. In order to obtain a robust circuit and additional step of design centering is required. Design centering techniques are either statistical (/7/, /8/) or deterministic (/9/, /10/, /11/).

The whole idea of robust design (as sometimes practised by IC designers) relies on the assumption, that the circuit characteristics reach their extreme values at points where the operating conditions and process variations take their so-called corner values. In order to establish, whether the design is robust, designers examine the performance of the circuit for all combinations of corner values. Every such combination represents a corner point of the design.

The number of corner points can be large. Beside 4 corner points for MOS transistors (result of the process variations), every operating condition brings along at least two extreme values - the minimal and the maximal value. For the operating temperature IC designers usually examine more than the two extreme values. The same can also be the case for other operating conditions and process variations.

The reason why one examines the circuit for more than only the extreme operating conditions is the fact that the circuit characteristics are not necessarily monotonic functions of operating conditions and process variations. When these functions are not monotonic, the probability of making a wrong conclusion increases with the distance between individual corner points. By examining the circuit at a larger number of "corner" points this distance is decreased.

In order to obtain a robust design an IC designer varies the dimensions of individual transistors and other elements of the design until the design fulfils the requirements in all relevant corner points. Whether or not a particular design is robust can be examined by simulating it at those corner points. If one examines the circuit for all combinations of 5 MOS corners, 3 temperature corners and 2 power supply voltage corners, a total of 30 corners must be examined.

IC designers practise robust design by iterating corner point simulation and circuit parameter adjustments for selected structure (topology). Obviously the only part of this process where the computer plays a role is the simulation. The parameter adjustment is still performed by the designer manually and is based on knowledge and past experience. One way of automating the process of parameter adjustment is the transformation of the robust design problem, as perceived by the IC designer, into a (constrained) optimization problem. There exist many algorithms for solving (constrained) optimization problems that can be applied to solve the IC designer's robust design problem.

The remainder of this paper is organised as follows: first the robust design method is mathematically formulated. A short introduction to optimization is given upon which the relationship between robust design and cost function used in the process of optimization is established. The cost function is divided in two parts: penalties for circuits that cause the simulator to fail at evaluating the circuit and penalties arising from design requirements. The use of the method is illustrated on a robust amplifier design problem. Finally the conclusions and ideas for future work are given.

#### 2 Design Methodology

#### 2.1 Circuit design and corner points

The robust design process as perceived and practised by an IC designer is based on the notion of corner points. A corner point is a combination of some process variation and M operating conditions. Suppose that we have a set of possible process variations

$$P_0 = \left\{ p_0^1, \dots, p_0^{n_0} \right\} \tag{1}$$

and for every operating condition a set of values that are of particular interest to the designer

$$P_i = \left\{ p_i^1, ..., p_i^{n_i} \right\} \qquad i = 1, ..., M \tag{2}$$

$p_0^1$  stands for the characteristics of the nominal IC fabrication process and  $p_1^1, p_2^1, ..., p_M^1$  for the nominal operating conditions. The cross product of M+1 sets from (1) and (2) is the set of corner points C. In general a subset of these points is examined during the process of robust design

$$C = P_0 \times P_1 \times ... \times P_M \tag{3}$$

The number of corners is

$$K = \prod_{i=0}^{M} n_i \tag{4}$$

The performance of the circuit, (which is the result of some combination of process variations during its fabrication and operating conditions during its use), is described by a vector of N real values  $y = [y_1, ..., y_N] \in R^N$ .

We represent the circuit as a function that for any combination of n circuit parameters denoted by vector  $\underline{x}$  and some combination of process variations and operating conditions denoted by q produces a vector of circuit characteristics  $\mathcal{Y}$ .

$$D: (\underline{x}, q) \mapsto \underline{y} \qquad \underline{x} \in \mathbb{R}^{n}, q \in \mathbb{C}, \underline{y} \in \mathbb{R}^{N}$$

$$y(\underline{x}, q) = [y_{1}(\underline{x}, q), y_{2}(\underline{x}, q), ..., y_{N}(\underline{x}, q)] =$$

$$[D_{1}(\underline{x}, q), D_{2}(\underline{x}, q), ..., D_{N}(\underline{x}, q)] \qquad (5)$$

In the subsequent sections we also use the following notation for (5):

$$D_i: (\underline{x}, q) \mapsto y_i \qquad \underline{x} \in R^n, q \in C, y_i \in R$$

Two vectors express the design requirements: a vector of lower bounds  $\underline{b} = [b_1,...,b_N] \in \mathbb{R}^N$  and a vector of upper bounds  $\underline{B} = [B_1,...,B_N] \in \mathbb{R}^N$ . For the sake of simplicity we allow for any lower bound to take the value  $-\infty$ , meaning that there is no lower bound on the respective circuit characteristic. Similarly any upper bound can take the value  $+\infty$ , meaning that no upper bound exists on the respective circuit characteristic. A circuit with circuit parameters  $\underline{x}$  satisfies the design requirements for a particular corner point  $q \in C$  if the following set of relations holds:

$$b_i \le y_i \le B_i \qquad i = 1, ..., N \tag{6}$$

Let g(x) denote some continuous monotonically increasing function defined for  $x \ge 0$ . Define a new function:

$$f(x) = \begin{cases} 0 & x < 0 \\ g(x) - g(0) & x \ge 0 \end{cases} \tag{7}$$

(7) is used to establish the relation between the robust design problem and the constrained optimization problem.

A circuit design is satisfactory if it satisfies the design requirements for all corner points from set  $\,C.\,$

#### 2.2 Constrained optimization

Problems of the form

$$\underline{x}_o = \min_{\underline{x} \in S} r(\underline{x}) \qquad S \subseteq R^n$$

are n-dimensional unconstrained global optimization problems,  $\underline{x}_o$  is the global optimum and  $r(\underline{x})$  is a cost function. Most unconstrained optimization methods search merely for a local optimum, where the following relation holds:

$$\nabla r(\underline{x}) = 0$$

If the search space is constrained, i.e.  $S \subset R^n$ , the problem becomes a constrained optimization problem. The notion of global optimum remains unchanged, but the definition of local optimum changes.

The search space in constrained optimization is defined by means of constraints. In general two kinds of constraints exist. Explicit constraints have the form  $b \le x_i \le B$  where  $x_i$  can be any component of  $\underline{x}$ . More complex relations define implicit constraints like  $h(\underline{x}) \ge 0$  or  $h(\underline{x}) = 0$ . The former one is an inequality constraint and the latter one is an equality constraint. Note, that  $h(\underline{x})$  can be any function. Handling implicit constraints is more complicated than handling explicit constraints.

When optimizing integrated circuits, the vector of optimized parameters  $\underline{x}$  includes mostly circuit parameters like element widths and lengths, although in some cases also cur-

rent, frequency, resistance and other values can be among optimized parameters. Explicit constraints are mostly used for setting the limits imposed by the technology like minimum dimensions. Another possible use of explicit constraints is to force a parameter to remain in a particular interval, e.g. one could restrict the transistor width of a differential pair to stay above some given value. Explicit equality constraints can be used to impose a fixed dependence of a parameter on some subset of circuit parameters. Such constraints are easily enforced during optimization. More complex explicit constraints (i.e. explicit constraints on circuit characteristics, explicit inequality constraints) are also possible. Nevertheless one should keep in mind that a large number of more complex explicit constraints could in practice reduce the performance of an optimization algorithm.

Another important thing to note regarding optimization algorithms is that in practical cases they do produce a decrease in the cost function value when compared to the initial value. But in general, a large amount of computing time and resources has to be invested in order to find the global optimum of an optimization problem. Generally one is satisfied if:

- an optimization algorithm provides an improvement over the best economically justified human design,

- (at least partially) solves some problem without human intervention or

- helps the designer to speed up the design process.

In the past many efficient optimization algorithms that relied on the cost function value along with the values of its derivatives were developed. Since the sensitivity information is generally not available from circuit simulators (at least not to the extent required to calculate the partial derivatives of the cost function), one must rely to a different class of methods. Direct search methods /12/ rely only on cost function value and require no derivative information from the simulator. They are the methods of choice in this work.

# 2.3 Penalty function for enforcing constraints on circuit performance

In order to exploit optimization for robust circuit design a cost function has to be defined. The cost function is supposed to rank the set of possible designs thus making it ordered. Throughout the optimization all designs have the same structure (topology). Only the nominal circuit parameter values ( $\underline{x}$ ) are varied. Consider the following penalty function:

$$F(\underline{y}) = \sum_{i=1}^{N} \left( f\left(\frac{y_i - B_i}{A_i}\right) + f\left(\frac{b_i - y_i}{A_i}\right) \right) \tag{8}$$

Function (8) penalises any design with one or more characteristics lying outside the intervals defined by the respective lower and upper bounds on circuit performance. The

penalty is proportionate to the distance from the boundary of the interval. For a design which characteristics lie inside the intervals defined by  $\underline{b}$  and  $\underline{B}$ , the function returns 0. Note that the penalty function applies to the circuit characteristics for a particular corner point.

Since "bad" designs are associated with higher values of the penalty function and "good" designs are associated with 0, the definition of a cost function (which will in turn be minimised by the optimization algorithm) is right at hands:

$$r_{E}(\underline{x}) = \sum_{i=1}^{K} F(D(\underline{x}, q_{i}))$$

(9)

One can stop the optimization algorithm as soon as (9) reaches 0, since the algorithm found a point in the search space  $\underline{x}_0$  for which the corresponding design satisfies all performance constraints (6) in all corners. Furthermore, if the algorithm has a way of detecting the existence of a neighbourhood of  $\underline{x}_0$  where corresponding designs are all satisfactory, one can tell that the design requirements are too "loose". Ideally the design requirements should be so tight that every satisfactory point in the search space has no neighbourhood where all designs fulfil the design requirements. In such case one could be assured that the capabilities of the technology are fully exploited for the particular circuit structure.

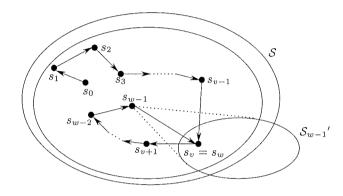

#### 2.4 Heuristic corner search

In previous section robust design was achieved by checking the circuit performance in all relevant corner points of the design (3). Since the total number of corner points grows exponentially with the increasing number of operating conditions (4), the analysis of circuit performance becomes intractable. Approaches for reducing the number of analysed corner points become of interest where one replaces the search through the complete set of corners C by its subset  $C_S = \{s(i): i=1,...,K_H\} \subset C$ . Consequently the number of checked corners is reduced to  $K_H = |C_S| < K$  and the corresponding term in the cost function becomes:

$$r_H(\underline{x}) = \sum_{i=1}^{K_H} F(D(\underline{x}, s(i)))$$

(10)

Several different heuristics can be defined for choosing the set  $C_s$ . The method of choice in this paper first examines the individual influences of operating conditions. The collected information is used for predicting the corners where circuit characteristics are expected to reach their extreme values, upon which those corners are examined. In the first part the following set of corners is examined:

$$q_{nom} = s_0^1 = s_1^1 = \dots = s_M^1 = (p_0^1, p_1^1, \dots, p_M^1)$$

$s_0^i = (p_0^i, p_1^1, \dots, p_M^1)$   $i = 2, \dots, n_0$

$$s_1^i = (p_0^1, p_1^i, ..., p_M^1)$$

$i = 2, ..., n_1$  (11)

Based on the results obtained for these corners, further 2N corners are generated (two for every circuit characteristic; one where the lowest value and one where the highest value is expected to take place) and examined:

$$q_{L}^{i} = \left(p_{0}^{l_{i}^{0}}, p_{1}^{l_{1}^{1}}, ..., p_{M}^{l_{M}^{M}}\right) \qquad q_{H}^{i} = \left(p_{0}^{h_{i}^{0}}, p_{1}^{h_{1}^{1}}, ..., p_{M}^{h_{M}^{M}}\right)$$

$$i = 1, ..., N$$

$$l_i^j = \underset{k=1,\dots,n_j}{\arg\min} \ y_i(\underline{x}, s_j^k) \qquad h_i^j = \underset{k=1,\dots,n_j}{\arg\max} \ y_i(\underline{x}, s_j^k)$$

$$i = 1,\dots, N \qquad j = 0,\dots, M$$

(12)

By searching through corners defined by (11) and (12) we need to check only  $K_H = \sum_{i=0}^M n_i - M + 2N + 1$  corners. The

price to pay is the risk of obtaining a narrower range for the circuit characteristic  $y_i$  in case the function  $D_i(\underline{x},q)$  is not monotonic with regard to the intervals enclosing operating conditions and intervals enclosing model parameters of process variations.

#### 2.5 Cumulative cost function

The cumulative cost function r(x) equals (9) (or (10) if heuristic corner search is used). This causes the optimizer to search for a circuit satisfying all design requirements. The optimization can be stopped as soon as some point where r(x)=0 is found. One also has to consider the case that the simulation itself fails to converge thus rendering the optimization incapable of determining the cost function value for a particular combination of circuit parameters. Besides that the simulator may succeed to simulate certain circuits, but the performance of these circuits is far from the desired performance (e.g. some of the transistors that are supposed to be in saturation, are not). To resolve the problem an additional penalty term  $r_c(x)$  is introduced into the cumulative cost function. The value of  $r_{c}(x)$  for such circuits should be significantly larger than the contribution of the penalty functions  $r_E(\underline{x})$  (or  $r_H(\underline{x})$ ). The additional penalty should be proportionate to the severity of the convergence problem (circuit performance problem).

Applying optimization to the cumulative cost function can solve the robust design problem. Any box-constrained optimization method can be used. The reason due to which box constraints are sufficient is the fact that we only need to constrain circuit parameters such as transistor widths and lengths to intervals of possible values. The implicit constraints arising from the design requirements are handled by the penalty functions.

#### 3 Results

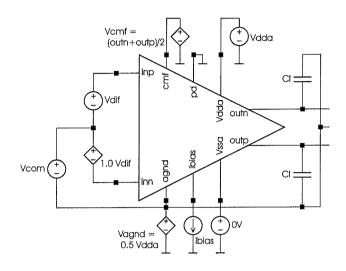

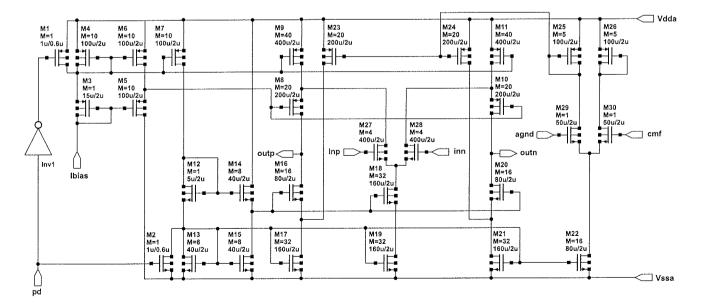

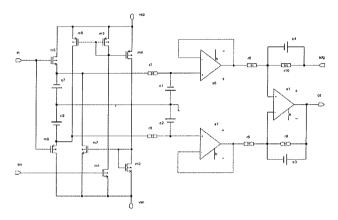

To illustrate the method, robust design has been applied to the circuit structure in Figure 1 /18/. The circuit is an amplifier with differential input, differential output and common mode feedback. The *M* and *W/L* values of transistors in Figure 1 (reference circuit) were designed by an IC designer.

Since the **pd** signal is kept low throughout normal operation so inverter Inv1 and transistors M1 and M2 are irrelevant to the design. An external current source pulls 16µA from the **bias** input in order to set the operating point of the circuit. During normal operation **Vdda** is set to 5V and **Vssa** to 0V. The **agnd** input voltage is in the middle between **vdda** and **vssa** since it is the analog reference level. The differential input is at v(inp, inn), whereas v(outp, outn) constitutes the differential output. Ideally the cmf input is kept at (v(outp)+v(outn))/2.

In the circuit there are several groups of transistors whose dimensions are mutually dependent. Their ratios were kept constant throughout the search. A similar approach can be found in /13/. The lengths of transistors M4-M11 are identical. The ratios of widths for these transistors M4-M11 are also kept constant since they constitute the current mirrors that set the operating point of the circuit. The same goes for M13-M22. The widths of M3 and M12 are adjusted according to designer's experience with regard to the W/L ratios of M4 and M13. Transistors M23, M24 must have the same widths. The same goes for M25 and M26. Transistors in both differential pairs must also be of the same width (M27-M28 and M29-M30). In the automated design process the same values for M were used as in figure 1.

#### 3.1 Design requirements

Note that  $V_{ds}$  and  $V_{dsat}$  denote the drain-source voltage and the drain-source saturation voltage. For p-MOS they represent the absolute values of respective quantities. Refer to Figure 2 for the test circuit.

Figure 2: Test setup for the circuit in figure 1.

First of all we require that for the operating point of all transistors except M1, M2 and the transistors in Inv1  $V_{ds} > V_{dsat} + 0.005$  holds in all examined corners. Let  $M_{rel}$  denote the set of all relevant MOS transistors. The saturation measure is defined as

$$P_{sat} = \sum_{M \in M_{rel}} ramp \left( V_{dsat} \left( M \right) + 0.005 - V_{ds} \left( M \right) \right).$$

Next the offset voltage (i.e. the common mode output voltage at  $V_{\rm dif}=0$  ,  $V_{\rm com}=0$ ) is measured.

Figure 1: The differential amplifier circuit taken from a real world application.

W/L and M values were designed by an IC designer.

The linear range is defined as the percentage of the maximal output voltage range [ $V_{ssa}$  -  $V_{dda}$ ,  $V_{dda}$  -  $V_{ssa}$ ]) where the differential amplification is above 1/2 of its maximum value. The common mode range is measured by keeping

the input differential voltage **Vdif** at 0, sweeping the input common mode voltage **Vcom** and observing the  $V_{ds}$  -  $V_{dsat}$  difference for all transistors in  $M_{rel}$ . The lowest and the highest value of the input common mode voltage  $(V_{imp} + V_{inn})/2$  are measured where  $V_{ds} > V_{dsat}$  holds for all transistors in  $M_{rel}$ .

In the AC analysis (transfer function from (inp, inn) to (outp, outn)) the gain at OHz, phase margin (difference to  $180^{\circ}$  at OdB gain) and the frequency where gain falls to OdB are measured. Noise analysis is performed with output at (outp, outn) and input at Vdif. Input noise spectrum density is measured at two frequencies: 10Hz ( $n_1$ ) and 1kHz ( $n_2$ ).

The measure of the amplifier area is defined as the sum of WL products for all transistors in  $M_{rel}$ .

#### 3.2 The set of corner points

A total of 5 CMOS corners arising from random process variations were examined along with the corners for temperature,  $V_{dda_1}$   $I_{bias}$ , and  $C_1$ . See Table 1 for the complete list of examined values. A total of 405 corners for the exhaustive corner search and 13+20=33 corners for the heuristic corner search must be examined.

|                  | Nominal | Extreme values |

|------------------|---------|----------------|

| MOS corners      | TM      | WO, WZ, WP, WS |

| Temperature      | 25°C    | -40°C, 125°C   |

| Power supply     | 5V      | 4.5V, 5.5V     |

| Bias current     | 16uA    | 13.6uA, 18.4uA |

| Load capacitance | 6pF     | 4.2pF, 7.8pF   |

Table 1: Corners of the design.

Table 2 lists the design requirements (lower and upper bounds on individual circuit characteristics).

#### 3.3 Results of optimization experiment

The optimizer tried to find a solution starting from a design that didn't work (all widths were  $20\mu m$ , lengths  $2\mu m$  and M3/M4 (M12/M13) width ratios were 0.2). 12 parame-

ters were optimized. The range for transistor dimensions was  $0.6\mu m$  to  $1000\mu m$  for widths (5 parameters),  $0.6\mu m$  to  $3\mu m$  for lengths (5 parameters), and 0.01 to 1.0 for M3/M4 (M12/M13) width ratios (2 parameters).

Additional penalty terms  $(r_C(\underline{x}))$  were introduced in the following cases:

- In case a failure in initial OP analysis occurred penalty of 10<sup>6</sup> was added. The offset was set to 10V and the remaining analyses (DC analyses, AC analysis and NOISE analysis) were skipped for the particular corner. All problems encountered in this analysis would reoccur in all other analyses since OP analysis precedes or is included in any other type of analysis.

- 2. In case a failure in the differential mode DC sweep analysis occurred the linear range was set to 0%.

- 3. In case of a failure in the common mode DC sweep analysis the lower (upper) bound for the common mode range was set to +5V (-5V).

- 4. In case the AC analysis failed, OHz gain, phase margin and OdB frequency were set to 0.

- 5. In case the NOISE analysis failed  $n_1$  ( $n_2$ ) was set to  $10^{-4} V / \sqrt{Hz}$  ( $10^{-5} V / \sqrt{Hz}$ ).

- 6. If any of the failures from cases 1-5 occurred in the first part of the heuristic search, the second part of the search was skipped with additional penalty of 10<sup>9</sup>.

- 7. In case of a failure in OP analysis (case 1) when the remaining analyses were skipped for a particular corner, circuit characteristics that were supposed to result from the skipped analyses were set to the values mentioned in cases 2-5.

SPICE was used as the circuit simulator /14/. The optimization method (/15/, /16/) was a modified constrained simplex method based on /17/. The results are summarized in Tables 3-5. The optimization was stopped as soon as some circuit with cost function value less or equal 0 was found.

|                 |                             | Requirements                       |                         |  |  |  |  |  |

|-----------------|-----------------------------|------------------------------------|-------------------------|--|--|--|--|--|

|                 | b (min)                     | B (max)                            | A (1 penalty point per) |  |  |  |  |  |

| Sat. measure    | -∞                          | 0                                  | 0.001m                  |  |  |  |  |  |

| Offset voltage  | 0 (or — ∞)                  | 50mV                               | 1mV                     |  |  |  |  |  |

| Linear range    | 73%                         | 100% (or +∞)                       | 0.1%                    |  |  |  |  |  |

| CM range (low)  | -∞                          | -1.2V                              | 1mV                     |  |  |  |  |  |

| CM range (high) | 1.2V                        | + ∞                                | 1mV                     |  |  |  |  |  |

| 0Hz gain        | 60dB                        | +∞                                 | 1dB                     |  |  |  |  |  |

| Phase margin    | 50°                         | $180^{\circ} (\text{or} + \infty)$ | 1°                      |  |  |  |  |  |

| OdB frequency   | 7.0 MHz                     | + ∞                                | 0.1MHz                  |  |  |  |  |  |

| Noise at 10Hz   | - ∞                         | 620 nV /√Hz                        | 100 nV /√Hz             |  |  |  |  |  |

| Noise at 1kHz   | ∞                           | 62 nV /√Hz                         | 10 nV /√Hz              |  |  |  |  |  |

| Area            | $0  \mu m^2  (or - \infty)$ | 8300 μm²                           | 100 µ m²                |  |  |  |  |  |

Table 2: Design requirements.

|                           | Lowest     | Nominal     | Highest                 |  |

|---------------------------|------------|-------------|-------------------------|--|

| Offset voltage            | 0.195mV    | 5.5mV       | 32.7mV                  |  |

| Linear range              | 74.0%      | 79.4%       | 81.6%                   |  |

| CM range (lo.)            | -1.65V     | -1.40V      | -1.15V                  |  |

| CM range (hi.)            | 3.45V      | 3.95V       | 4.45V                   |  |

| 0Hz gain                  | 61.6dB     | 74.0dB      | 77.3dB                  |  |

| Phase margin              | 56.2°      | 62.8⁰       | 74.5°                   |  |

| 0dB freq.                 | 8.23MHz    | 13.1MHz     | 16.8MHz                 |  |

| Noise at 10Hz             | 332nV /√Hz | 386nV /√Hz  | 599nV /√Hz              |  |

| Noise at 1kHz 33.7nV /√Hz |            | 39.3nV /√Hz | 60.8 <sub>nV</sub> /√Hz |  |

| Area 8240 μm <sup>2</sup> |            | 8240µm²     | 8240µm²                 |  |

Table 3: Performance of the reference circuit over the set of corners examined by the heuristic search.

The results in Tables 3 and 4 represent the reference circuit's performance and the computer-designed circuit's performance. In the nominal operating conditions the circuit resulting from the optimization run has worse offset voltage. The upper boundary of common mode range, gain and noise are slightly worse. Linear range, lower boundary of common mode range, phase margin, frequency range and circuit area were better than for the reference circuit.

In the respective worst corners (as seen from the standpoint of the heuristic search) the computer-designed circuit has a slightly worse offset voltage and upper boundary of the common mode range. Linear range, lower boundary of common mode range, gain, phase margin, frequency range and noise are better than for the reference circuit.

|                | Lowest                  | Nominal     | Highest                  |  |

|----------------|-------------------------|-------------|--------------------------|--|

| Offset voltage | 24.8mV                  | 34.4mV      | 38.9mV                   |  |

| Linear range   | 78.3%                   | 83.1%       | 85.1%                    |  |

| CM range (lo.) | -1.65V                  | -1.45V      | -1.20V                   |  |

| CM range (hi.) | 3.35V                   | 3.85V       | 4.35V                    |  |

| 0Hz gain       | 72.0dB                  | 73.2dB      | 74.4dB                   |  |

| Phase margin   | 62.0°                   | 68.5°       | 75.0°                    |  |

| 0dB freq.      | 10.2MHz                 | 17.0MHz     | 23.2MHz                  |  |

| Noise at 10Hz  | 379nV /√Hz              | 443nV /√Hz  | 571 nV /√Hz              |  |

| Noise at 1kHz  | 38.3 <sub>nV</sub> /√Hz | 44.8nV /√Hz | 57.8 <sub>n</sub> ∨ /√Hz |  |

| Area           | 7810µm²                 | 7810µm²     | 7810µm²                  |  |

Table 4: Results of the automated design process over the set of corners examined by the heuristic search.

Since the main goal of robust design is to obtain a circuit whose worst-case characteristics are as good as possible, the comparison of worst case performance is of higher relevance than the comparison of nominal performance. The key result of the experiment is not merely the proof of computer's ability to outperform a human designer, but also the fact that the computer can size a circuit with little prior knowledge of it. Only the circuit's structure, performance constraints, some penalties for circuits that don't simulate and the bias current ratios (*M* parameter values) were pre-

defined in the experiment. To supply such knowledge an experience of a senior designer is still required. Table 5 summarises the resulting transistor dimensions with respect to the reference design.

We expect that by replacing the device models (i.e. replacing 0.6-micron process models with 0.35-micron process models) and executing an optimization run, automated technology migration can be achieved /19/. The applicability of our method to technology migration is to be examined in our future work.

#### 4 Conclusions

The robust IC design methodology applied by IC designers in their everyday work has been mathematically formulated. A general cost function approach utilising penalty functions for describing the robust IC design problem has been proposed. Penalty functions for circuits that can't be simulated were used to guide the search away from regions of search space that can't be analysed. In order to reduce the number of examined corners a heuristic search method for determining the minimal and maximal values of circuit characteristics has been used. Robust design is achieved by minimising the cumulative cost function. In order to achieve this some box constrained optimization method can be used. In our experiment the modified constrained simplex method was used due to its performance in past studies.

The automated design method was tested on an amplifier design problem. The computer attempted to design the circuit without a working initial point and with wide intervals for transistor lengths and widths.

The optimization run resulted in an overall better circuit when results were compared to the nominal circuit's performance. A bigger difference was observed when comparing the worst characteristic values of computer-designed circuits to the reference circuit. The computer-designed circuit generally outperformed the reference circuit, except in the offset voltage. The offset voltage however was more uniform for the computer-designed circuit (from 24.8mV to 38.9mV) than for the reference circuit (0.2mV to 32.7mV). This means that the dependence of the offset voltage on environmental effects is lower for the computer-designed circuit.

The experiment was run on a 450MHz Intel Pentium III computer with 128MB of RAM. Since the computer was running other tasks beside the optimization itself, the timing results may be somewhat higher than they could be. The optimization took 18 hours. 410 circuits were evaluat-

|           | W <sub>29</sub> | L <sub>29</sub> | W <sub>27</sub> | L <sub>27</sub> | $W_{14}$ | L <sub>14</sub> | <b>W</b> <sub>8</sub> | L <sub>8</sub> | $W_5$ | L <sub>5</sub> | <b>r</b> wl(3,4) | <b>r</b> <sub>wl(12,14)</sub> |

|-----------|-----------------|-----------------|-----------------|-----------------|----------|-----------------|-----------------------|----------------|-------|----------------|------------------|-------------------------------|

| Reference | 50u             | 2.0u            | 400u            | 2.0u            | 40u      | 2.0u            | 200u                  | 2.0u           | 100u  | 2.0u           | 0.150            | 0.125                         |

| Computer  | 165u            | 1.3u            | 343u            | 1.6u            | 43u      | 1.7u            | 558u                  | 2.0u           | 71u   | 1.0u           | 0.100            | 0.138                         |

Table 5: Results of the automated design process -transistor dimensions and ratios.

ed. An average circuit evaluation took 158s (4.8s per corner). If we take into account the fact that the state-of-theart PC desktop computer nowadays is about 5 times faster, the optimization run would complete in 3.6 hours. Further acceleration is expected to be achieved by doing the corner analyses for several corners in parallel. The acceleration could reach

$$S = \min\left(\sum_{i=0}^{M} n_i - M + 1,2N\right)$$

when the aforementioned heuristic search would be used. In the two examined cases we could expect speedups of up to 13. The achievable speedup would of course be smaller due to the synchronisation penalty. Speedups of 2-3 could be easily achieved by using a cluster of 4-5 workstations. This would bring the optimization time down to 1-2 hours for the sample circuit.

There remain several possible applications of the method to be examined in the course of future research:

- Incorporating design optimization into the method,

- Technology migration of existing designs to newer technologies (e.g. 0.6-micron to 0.35-micron migration),

- Tuning existing designs as they are reused in newer ICs in order to improve their (worst case) performance (and reduce the occupied silicon area or power consumption),

A great benefit is expected from parallel processing. Multiple corner points can be analysed in parallel. Furthermore, different types of analysis for the same corner point can also be executed in parallel. Finally a parallel optimization method (/20/, /21/) can be applied to minimise the cumulative cost function. Such multilevel parallelism could exploit the power of large clusters of workstations without utilising parallelism at the simulation level and thus take advantage of the same (thoroughly tested) simulation algorithms as those currently used in IC design.

#### 5 References

- /1/ Gielen, G. G. E., Rutenbar, R. A., Computer-Aided Design of Analog and Mixed-Signal Integrated Circuits. Proceedings of the IEEE, vol. 88, no. 12, pp. 1825-1854, 2000.

- /2/ del Mar Hershenson, M., Boyd, S. P., Lee, T. H., Optimal Design of a CMOS Op-Amp via Geometric Programming, IEEE Transactions on Computer Aided Design of Integrated Circuits and Systems, vol. 20, no. 1, pp. 1-21, 2001.

- /3/ Phelps, R., Krasnicki, M., Rutenbar, R. A., Carley, L. R., Hellums, J. R., Anaconda: Robust Synthesis of Analog Circuits via Stochastic Pattern Search. Proceedings of the IEEE 1999 Custom Integrated Circuits Conference, pp. 567-570, 1999.

- /4/ Krasnicki, M., Phelps, R., Rutenbar, R. A., Carley, L. R., Maelstrom: Efficient Simulation-Based Synthesis for Custom Analog Cells. Proceedings 1999 Design Automation Conference, pp. 945-950, 1999.

- /5/ Phelps, R., Krasnicki, M., Rutenbar, R. A., Carley, L. R., Hellums, J. R., Anaconda: Simulation-Based Synthesis of Analog Circuits via Stochastic Pattern Search, IEEE Transactions on Computer Aided Design of Integrated Circuits and Systems, vol. 19, no. 6, pp. 703-717, 2000.

- /6/ Schwencker, R., Schenkel, F., Gräb, H., Antreich, K., The Generalized Boundary Curve A Common Method for Automatic Nominal Design and Centering of Analog Circuits. Design, Automation and Test in Europe Conference and Exhibition 2000. Proceedings, pp. 42-47, 2000.

- /7/ Aftab, S. A., Styblinski, M. A., IC Variability Minimization Using a New Cp and Cpk Based Variability/Performance Measure. 1994 IEEE International Symposium on Circuits and Systems, vol. 1, pp. 149-152, 1994.

- /8/ Keramat, M., Kielbasa, R., OPTOMEGA: an Environment for Analog Circuit Optimization. Proceedings of the 1998 IEEE International Symposium on Circuits and Systems, vol. 6, pp. 122-125, 1998.

- /9/ Abdel-Malek, H, Hassan, A., The Ellipsoidal Technique for Design Centering and Region Approximation. IEEE Transactions on Computer Aided Design of Integrated Circuits and Systems, vol. 10, no. 8, pp. 1006-1014, 1991.

- /10/ Dharchoudhury, A., Kang, S. M., Worst-Case Analysis and Optimization of VLSI Circuit Performances. IEEE Transactions on Computer Aided Design of Integrated Circuits and Systems, vol. 14, no. 4, pp. 481-492, 1995.

- /11/ Krishna, K., Director, S. W., *The Linearized Performance Penalty* (*LPP*) *Method for Optimization of Parametric Yield and Its Reliability*. IEEE Transactions on Computer Aided Design of Integrated Circuits and Systems, vol. 14, no. 12, pp. 1557-1568, 1995.

- /12/ R. M. Lewis, V. Torczon, M. W. Trosset, *Direct search methods: then and now. Journal of Computational and Applied Mathematics*, vol.124, no.1-2, pp.191-207, 2000.

- /13/ Gräb, H., Zizala, S., Eckmüller, J., Antreich, K., The Sizing Rules Method for Analog Integrated Circuit Design. IEEE/ACM International Conference on Computer-Aided Design, pp. 343-349, 2001.

- /14/ T. Quarles, A. R. Newton, D. O. Pederson, A. Sangiovanni-Vincentelli, SPICE3 Version 3f4 User's Manual, Berkeley, University of California, 1989.

- /15/ J. Puhan, T. Tuma, Optimization of analog circuits with SPICE 3f4. Proceedings of the ECCTD'97, vol. 1, pp. 177 180, 1997.

- /16/ J. Puhan, T.Tuma, I. Fajfar, Optimisation Methods in SPICE, a Comparison. Proceedings of the ECCTD'99, vol. 1, pp. 1279-1282, 1999.

- /17/ M. J. Box, A New Method of Constrained Optimization and a Comparison with Other Methods. Computer Journal, vol. 7, pp. 42-52, 1965.

- /18/ Gray, P. R., Hurst, P. J., Lewis, S. H., Meyer, R. G., Analysis and Design of Analog Integrated Circuits, Chapter 12. John Wiley & Sons, New York, 2001.

- /19/ Shah, A. H., Technology Migration of a High Performance CMOS Amplifier Using an Automated Front-to-Back Analog Design Flow. Design, Automation and Test in Europe Conference and Exhibition, 2002. Proceedings of Designers' Forum, pp. 224-229, 2002.

- /20/ J. E. Dennis, Jr., V. Torczon, Parallel Implementations of the Nelder-Mead Simplex Algorithm for Unconstrained Optimization. Proceedings of the SPIE, Vol. 880, pp. 187-191, 1988.

- /21/ L. Coetzee, E. C. Botha, The Parallel Downhill Simplex Algorithm for Unconstrained Optimisation. Concurrency: Practice and Experience, vol. 10, no. 2, pp. 121-137, 1998.

Arpad Bűrmen, Drago Strle, Franc Bratkovič, Janez Puhan, Iztok Fajfar, Tadej Tuma University of Ljubljana Faculty of Electrical Engineering Tržaška 25, SI-1000 Ljubljana E-mail: arpadb@fides.fe.uni-lj.si

Prispelo (Arrived): 24.04.2002 Sprejeto (Accepted): 28.06.2002

### MOŽNOSTI IZVEDBE ADAPTIVNEGA FIR SITA S PROGRAMIRNIMI (FPGA) VEZJI

#### Davorin Osebik, Rudolf Babič

#### Fakulteta za elektrotehniko, računalništvo in informatiko, Univerza v Mariboru

Ključne besede: digitalna obdelava signalov, adaptivno izločanje motilnega signala, adaptivna digitalna sita, nerekurzivna digitalna sita, porazdeljena aritmetika. zaporedna aritmetična struktura

Izvleček: V članku je prikazan matematični opis adaptivnega FIR sita s 16 koeficienti, prikaz izvedbe s programirnimi logičnimi vezji firme Xilinx in simulacija izvedbene strukture. Sito je izvedeno v porazdeljeni aritmetiki s sprotnim izračunom vektorja delnih vsot koeficientov v(k). Načrtano je v dveh delih, iz običajne enote nerekurzivnega digitalnega sita, ki mu lahko spreminjamo koeficiente, in enote za adaptivno izračunavanje koeficientov. Aritmetična enota za izračun koeficientov FIR sita izračunava koeficiente po LMS algoritmu. Izvedena je z zaporedno logiko za izvajanje aritmetično logičnih operacij. S takšnim pristopom smo dosegli linearno naraščanje aparaturne kompleksnosti enote za izračun koeficientov v odvisnosti od stopnje sita, kar omogoča pomembni prihranek logičnih elementov. Za izvedbo smo uporabili dve FPGA vezji XC4013E in XC4020E. Vezje XC4013E za adaptivno enoto FIR digitalnega sita in vezje XC4020E za enoto izračuna koeficientov FIR sita. V prispevku so podani podrobni opisi notranjih spremenljivk enote za izračun koeficientov in enote FIR sita s spremenljivimi koeficienti na bitnem nivoju.

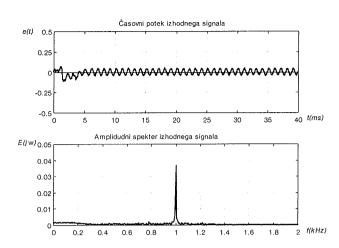

Vhodne spremenljivke adaptivnega digitalnega FIR sita smo predstavili z dolžino 16-bitov, medtem ko je dolžina registrov notranje aritmetične strukture med 16 in 24-biti. Rezultate smo zaenkrat dobili s simulacijo izvedbene strukture adaptivnega FIR sita s programskim paketom OrCAD 9.0 ob podpori razvojnega orodja firme Xilinx XACT 5.2. Rezultati so podani za primer izločanja motilnih signalov z lastnostjo hrupa prometne ulice. Pri tem je bilo doseženo izboljšanje razmerja S/N med 20 in 22 dB pri vhodnem razmerju S/N je -20. Izboljšanje razmerja S/N je odvisno od vhodnega razmerja S/N.

### The Practicability of Adaptive FIR Digital Filter Implementation with FPGA Circuits

Key words: digital signal processing, adaptive digital filters, FIR filters, adaptive noise cancelling, distributed arithmetic technique, serial arithmetic structure

Abstract: The FPGA circuits have become a good alternative for digital signal processing appplications. In this article the mathematical description and computer simulation of the hardware implementation of the adaptive FIR digital filter structure in FPGA circuits is presented. The hardware implementation of digital filter structure is based on the use of distributed arithmetic filter arhitecture which uses no multipliers in its realisation of the filtering functions.

Adaptive digital filters are successfully used in different fields, such as communication, radar, sonar, seismic, and biomedical engineering. Almost all of these adaptive filters have one common characteristic that a reference input signal vector  $\mathbf{u}(k)$  and primary signal  $\mathbf{d}(k)$  are applied to compute an estimation error signal  $\mathbf{e}(k)$ , which is used to control the values of adjustable digital filter coefficients  $\mathbf{h}(k)$ . The presented adaptive digital FIR filter which is carried out with programmable gate array could be used for noise cancelling from the corrupted input signal.

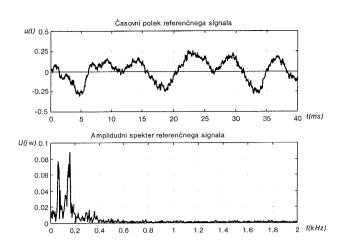

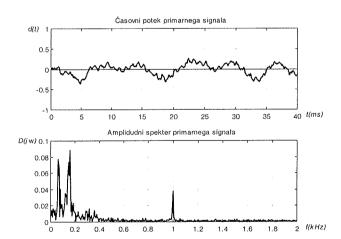

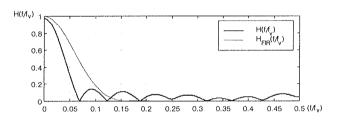

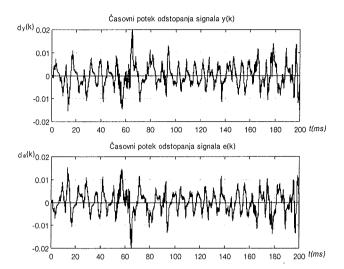

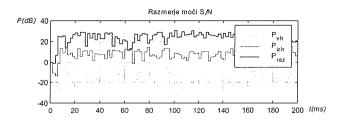

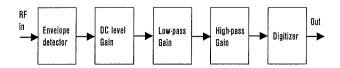

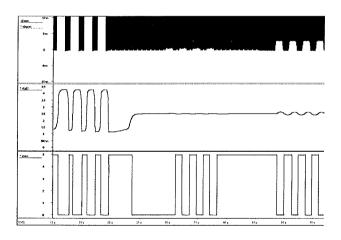

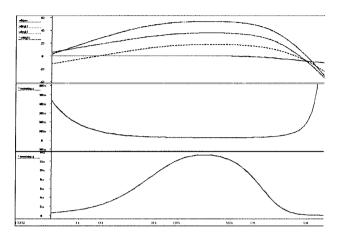

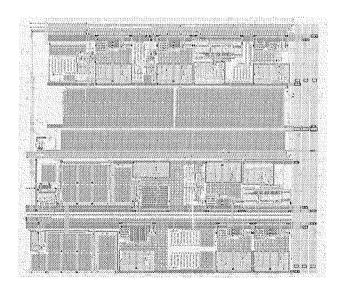

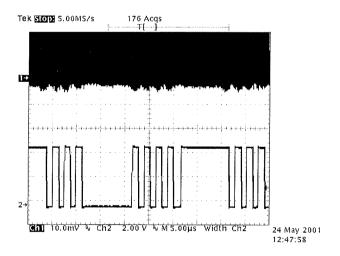

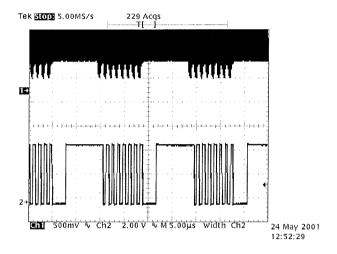

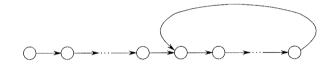

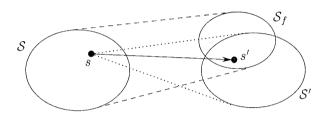

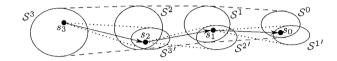

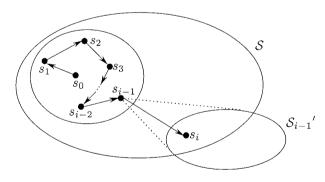

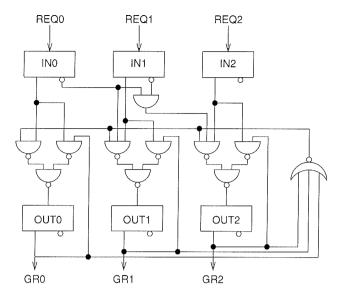

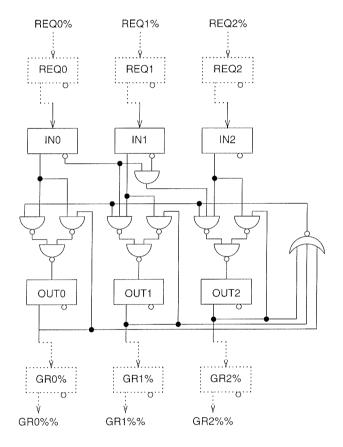

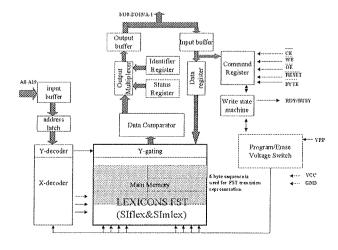

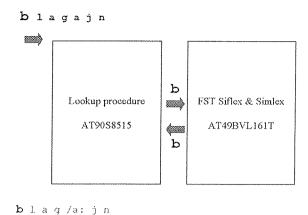

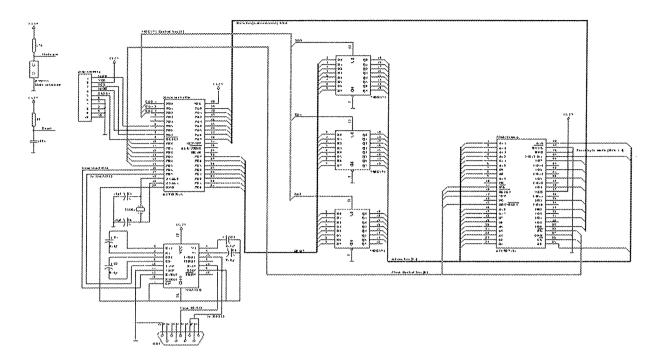

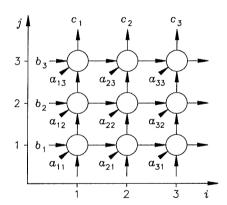

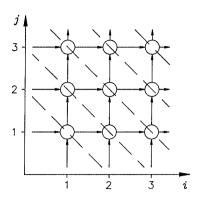

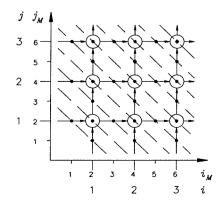

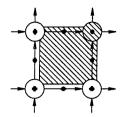

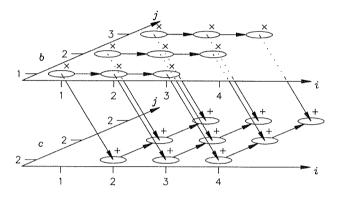

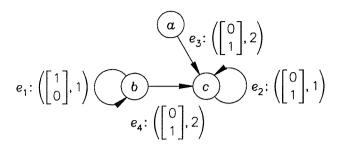

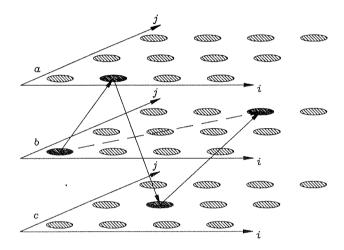

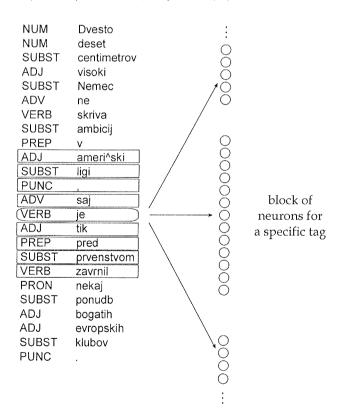

The basic application of adaptive structure is shown in block diagram in figure 2. The first unit is the FIR filter structure, which determines the output values y(k) with distributed arithmetic principle by equations 6. The partial sums of filter coefficients signed as vi and defined with equations 6, are calculated from vector of filter coefficients h(k) and the vector of inputs u(k), by using of equation 12. Because of current calculations of their adapted values, they cannot be stored in the ROM memory as in the ROM-accumulator structure of classical distributed arithmetic realisation /5/. The 16 taps FIR digital filter structure, made within FPGA circuit XC4013 is shown in figure 3. The hardware complexity is accomplished with 16 bits input and output word length and with 16 to 24 bits word length of arithmetic-logic unit. The second unit in the figure 2 is the structure for adaptive filter coefficients calculation, where the least-mean-square (LMS) adaptation algorithm is used. The coefficients of nonrecursive filter vector h(k) was initially obtained from equations (2) and (3) and from (16), (17) and (19) respectively. In these equations  $\mu$  is the step of adaptation, e(k) is the estimation error signal, and u(k) is the reference signal as the input signal in the FIR filter. The product of the e(k)u(k) from (15) is also implemented with distributed arithmetic technique, where the serial logic of arithmetic operation is used. The hardware complexity of the structure for adaptive filter coefficients calculation rises linear with number of taps. In figure 4 the block diagram of unit for adaptive filter coefficients calculation is shown. For complexity of 16 taps and 19 bits of arithmetic and logic unit the structure is made within one FPGA circuit XC4020E and a adapted set of the taps is obtained every 10  $\mu$ s.

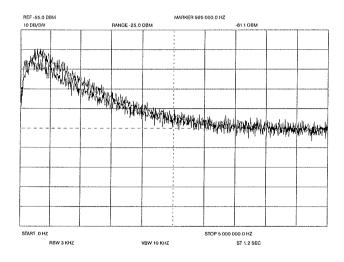

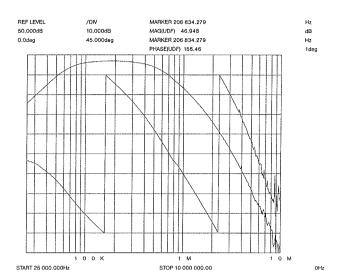

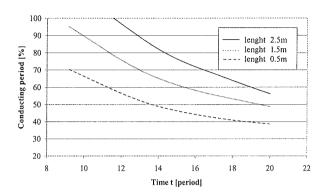

The whole hardware structure was simulated with OrCAD Express and Xilinx XACT 5.2. With 20MHz clock frequency the input signals  $\mathbf{u}(k)$  and  $\mathbf{d}(k)$  sampling frequency of 100 kHz was obtained. The results of presented adaptive digital filter application are shown as noise cancelling from corrupted input signal. In this application the street noise signal is taken into account. The results depends on the signal to noise (S/N) ratio of the input signal of about -20dB the noise component is successfully eliminated, and improvement of S/N ratio of 22dB is obtained. The results are shown as comparision of input reference, primary signal and output signal in the time and frequency domain in the figures 6,7 and 8 and as power S/N ratios of the input signal ( $P_{\text{tzh}}$ ) output signal ( $P_{\text{tzh}}$ ) and improved output signal ( $P_{\text{raz}}$ ) in the figure 11 respectively.

#### 1. Uvod

Adaptivna digitalna sita se uspešno uporabljajo na raznolikih področjih: v komunikacijski tehniki, radarski in sonarni tehniki, seizmologiji in biomedicinski tehniki. Čeprav gre za različna področja, imajo vsa eno skupno lastnost: želeni odziv se izračunava na osnovi ocenitvenega pogreška. Adaptivno sito je sestavljeno iz digitalnega sita in adaptivnega algoritma za izračun koeficientov. Izmed številnih aplikacij uporabe adaptivnih sit bomo predstavili aplikacijo digitalnega sita namenjeno nevtralizaciji interferenčnih signalov iz koristnega signala /1/.

Pri izvedbi sistemov za digitalno procesiranje signalov (DPS) obstajata dve možnosti: izvedba aplikacije s signalnim procesorjem ali izvedba s programirnimi vezji /2/. Pri izvedbi sistemov za DSP s signalnim procesorjem proces procesiranja temelji na ustrezno zapisanem algoritmu /3/, medtem ko pri izvedbi sistemov za DPS s programirnimi vezji procesiranje temelji na aparaturni strukturi, ki omogoča implementacijo v programirna vezja. Pri tem se uporabljajo takšne strukture, ki dopuščajo enostavno povečanje aplikacije z dodajanjem paralelnih struktur. Zmanjšanje aparaturne kompleksnosti je možno doseči z različnimi strukturami FIR sit. Pri FIR sitih s konstantnimi koeficienti zelo poenostavi aparaturno kompleksnost uporaba pomnilnika za zapis delnih vsot koeficientov /4, 5/. Zmanjšanje pomnilnika je možno doseči tudi z izvedbo FIR sit v kaskadni obliki /6/, kjer digitalna sita z manj koeficienti povežemo v kaskadno obliko. Vse naštete strukture za zmanjšanje pomnilnika pri FIR sitih temeljijo na predhodnih izračunih delnih vsot koeficientov, ki jih vpišemo v ROM pomnilnik.

Pri uporabi FIR sit v adaptivnih sistemih se koeficienti spreminjajo za vsak otipek posebej. Uporaba struktur FIR sit s predhodno izračunanimi delnimi vsotami koeficientov v adaptivnih aplikacijah ni možna, saj operacija izračuna in vpisa delnih vsot v pomnilnik vzameta preveč časa. Za FIR sita s spremenljivimi koeficienti so zanimive strukture, ki temeljijo na množenju in akumuliranju izračunane vrednosti (Multiply and Accomulate, MAC algoritmi), in strukture, ki temeljijo na vzporedni porazdeljeni aritmetiki /7/.

Pri izvedbi algoritmov za DPS se je pokazala primerna uporaba zaporedne logike za izvajanje aritmetično logičnih operacij /8/. Z uporabo zaporedne logike izvajanja aritmetično logičnih operacij je zmanjšanje aparaturne kompleksnosti približno za faktor širine aritmetike, pri tem se potreben čas izračuna bistveno ne spremeni. Izračun koeficientov po LMS algoritmu pri FIR situ poteka v celoti z uporabo zaporedne logike.

V članku bomo prikazali možnost izvedbe adaptivnega nerekurzivnega digitalnega sita s programirnim poljem logičnih vezij. Posebej bomo podali matematični opis enote FIR sita v porazdeljeni aritmetiki razdeljene na N podstruktur s sprotnim izračunom delnih vsot koeficientov. Predstavili bomo izvedbo enote FIR sita s programirnim vezjem XC4013E. Pri enoti za izračun koeficientov bomo podali matematični opis koeficientov po LMS algoritmu in izvedbo v programirnem vezju XC4025E. Opisali bomo načina povezave obeh enot, ki skupaj tvorita adaptivno sito. Predstavili bomo dobljene rezultate, ki smo jih zaenkrat dobili še s simulacijo s programskim paketom Orcad 9.0 ob podpori razvojnega orodja XCAT 5.2 za načrtovanje programirnih vezij. V rezultatih podajamo uspešnost izločitve motilnega signala iz koristnega signala, podana pa je tudi primerjava med matematičnim modelom in dejansko izvedbo adaptivnega sita.

#### 2. Uporaba adaptivnih sit za nevtralizacijo interferenčnih signalov

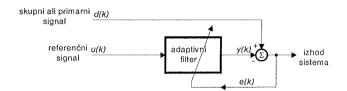

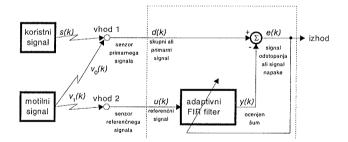

S programirnimi vezji smo realizirali adaptivno FIR sito, katerega smo uporabili za odstranjevanje prisotnih interferenc iz koristnega signala. Postopek odstranjevanja interferenc temelji na uporabi dveh senzorjev: senzorja primarnega signala d(k) in senzorja referenčnega signala u(k). Blokovno shemo prikazuje slika 1.

Slika 1: Adaptivni sitem v aplikaciji odstranjevanja interferenčmih signalov

V splošnem je lahko uporabljen poljubni adaptivni algoritem in poljubna struktura digitalnega sita. Za aparaturno izvedbo je potrebno izbrati algoritem, ki bo računsko dovolj preprost, saj je potrebno izračun opraviti v času enega otipka vhodnih signalov u(k) in d(k). Preprost matematični algoritem je tudi lažie izvesti v aparaturni opremi. Kriterii, ki uporablja najmanjše srednje kvadratično odstopanje - LMS kriterij, da dovolj dobre rezultate pri odstranjevanju interferenc motilnega signala iz koristnega signala. Kriterij najmanjšega srednjega kvadratičnega odstopanja temelji na minimizaciji izhodne moči prisotnega šuma v koristnem signalu. Koeficiente FIR sita za LMS kriterij je možno izračunati na optimalnem linearnem diskretnem situ, ki je poznano kot Wienerjevo sito /1/. Za aparaturno izvedbo je primernejša metoda algoritma strmega spusta, pri kateri so optimalnim koeficientom Wienerjevega sita približamo v nekaj korakih /9, 10/. S tem algoritmom dobimo dovolj natančen in robusten izračun koeficientov adaptivnega FIR sita.

Za digitalno sito smo izbrali FIR sito, pri katerem ni težav s stabilnostjo. Pri tem smo za FIR sito uporabili strukturo porazdeljene aritmetike. Koeficienti FIR sita se izračunavajo na osnovi LMS kriterija.

Izračun veličin pri adaptivnem FIR situ po LMS kriteriju z uporabo metode strmega spusta poteka po treh temeljnih enačbah:

1. izračun izhodne vrednosti FIR digitalnega sita

$$y(k) = \mathbf{h}^{T}(k)\mathbf{u}(k), \tag{1}$$

2. izračun ocene odstopanja

$$e(k) = d(k) - y(k). \tag{2}$$

3. izračun koeficientov sita

$$\mathbf{h}(k) = \mathbf{h}(k-1) + \mu \mathbf{u}(k) e(k). \tag{3}$$

V enačbah (1), (2) in (3) imata vektor koeficientov FIR sita  $\mathbf{h}(\mathbf{k})$  in vektor koeficientov vhodnega signala  $\mathbf{u}(\mathbf{k})$  naslednje komponente:

$$\mathbf{h}(k) = \begin{bmatrix} h_0(k) \\ h_1(k) \\ \vdots \\ h_{N-1}(k) \end{bmatrix} \text{ in } \mathbf{u}(k) = \begin{bmatrix} u(k-1) \\ u(k-2) \\ \vdots \\ u(k-N) \end{bmatrix}.$$

(4)

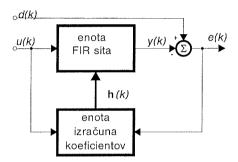

Na osnovi enačb adaptivnega FIR sita smo za izračun veličin adaptivnega digitalnega sita izdelali blokovno shemo, razdeljeno na enoto FIR sita in enoto za izračun koeficientov. Blokovno shemo obeh struktur prikazuje slika 2.

Slika 2: Blokovna shema adaptivnega digitalnega sita

Adaptivno digitalno sito sestavlja enota FIR sita, ki opravlja izračun izhodne vrednosti y(k) po enačbi (1) na osnovi ktega otipka referenčnega signala u(k) in dobljenega k-tega vektorja koeficientov h(k) FIR sita. Izračun k-tega vektorja koeficientov FIR sita poteka v dveh korakih. V prvem koraku je potrebno določiti oceno odstopanja e(k). Ocena odstopanja je določena kot razlika med k-tim otipkom primarnega signala d(k) in k-tim otipkom izhodnega signala y(k). Izračun opisuje enačba (2). Na osnovi določene ocene odstopanja e(k) po LMS kriteriju z metodo strmega spusta je vektor koeficientov določen z enačbo (3).

Predstavili smo izračun veličin adaptivnega digitalnega sita s poljem programirnih logičnih vezij. Na osnovi podrobnega matematičnega zapisa enačb notranjih spremenljivk adaptivnega FIR sita bomo podali njihovo aparaturno kompleksnost in rešitve, ki smo jih uporabili pri izvedbi adaptivnega sita s programirnimi vezji.

#### 2.1 Enota FIR sita

Pri FIR sitih izračun izhodne besede y(k) opisuje enačba (1). V enačbi (1) sta matriki koeficientov h(k) in u(k) za FIR sito z N koeficienti enodimenzionalni matriki dimenzije N. Elemente obeh matrik podaja zapis (4). Namesto opisa izračuna izhodne besede y(k) po enačbi (1) lahko izračun opišemo s konvolucijsko enačbo

$$y(k) = \sum_{i=0}^{N-1} h_i(k) u(k - (i+1)).$$

(5)

V enačbi (5) so h<sub>i</sub>(k) komponenta vektorja koeficientov **h**(k) digitalnega FIR sita in u(k-(i+1)) so komponenta vektorja koeficientov vhoda u(k). Pri izbiri izvedbe FIR sita s spremenljivim vektorjem koeficientov h(k) imamo možnost med izbiro izvedbe FIR sita v koncentrirani aritmetiki, kjer izračun izhodne besede y(k) poteka neposredno po konvolucijski enačbi (5). Pri tej metodi, ki je poznana kot izvedba FIR sita v koncentrirani aritmetiki, potrebujemo za izračun izhodne besede pri situ z N koeficienti N množilnikov. Druga možnost je izvedba FIR sita v porazdeljeni aritmetiki /5/, kjer izračun izhodne besede y(k) poteka brez uporabe množilnikov. Izvedba FIR sita v strukturi porazdeljene aritmetike temelji na uporabi pomnilnika za zapis delnih vsot koeficientov z algoritmom množenja in pomnjenja vrednosti (MAC algoritem) /7/. Izračun izhodne vrednosti izhodne besede y(k) poteka po enačbi

$$y(k) = \sum_{i=1}^{Bu-1} v_i 2^{-i} - v_{Bu}.$$

(6)

V enačbi (6) so  $v_i$  delne vsote koeficientov, ki so odvisni od vhodnega signala u(k) in vektorja koeficientov FIR sita h(k),  $v_i$ =f(u(k),f(k)).

Dosedanji razvoj digitalnih FIR sit s konstantnim vektorjem koeficientov h(k) je temeljil na izvedbi sit v različnih strukturah porazdeljene aritmetike, kjer smo z določenimi postopki zmanjševali potrebno velikost pomnilnika za zapis delnih vsot koeficientov. V primeru, da je vektor koeficientov FIR sita konstanten, je možno vse kombinacije delnih vsot izračunati vnaprej in jih vpisati v pomnilnik. Za sito z N koeficienti je vseh kombinacij delnih vsot koeficientov 2<sup>N</sup>. Pri spremenljivem vektorju koeficientov h(k) je potrebno poiskati strukture FIR sit v porazdeljeni aritmetiki, kjer bo potrebno izračunati le tiste delne vsote koeficientov, ki jih potrebujemo pri danem otipku vhodnega signala u(k). Teh delnih vsot je N. S tem se zmanjša potrebna velikost pomnilnika za zapis delnih vsot koeficientov z 2<sup>N</sup> na N pomnilniških lokacij /7/. Struktura, ki ustreza navedenim pogojem, je struktura s sprotnim izračunom delnih vsot koeficientov /7, 5/. Aparaturna izvedba FIR sita v porazdeljeni aritmetiki s sprotnim izračunom vektorja delnih vsot koeficientov je kompleksnejša od klasične ROM strukture sita FIR sita v porazdeljeni aritmetiki, je taka edina primerna za izvedbo sprotnega izračunavanja in delnih vsot koeficientov. Aparaturna kompleksnost strukture FIR sita s sprotnim izračunom delnih vsot koeficientov je ocenjena z N2.

# 2.1.1 Opis izračuna vrednosti izhodnega signala y(k) pri FIR situ s sprotnim izračunom delnih vsot koeficientov

Pri izračunu izhodne vrednosti y(k) digitalnega sita v porazdeljeni aritmetiki s sprotnim izračunom delnih vsot koeficientov izhajamo iz enačbe (1), kjer poteka množenje vektorja koeficientov h(k) in vektorja koeficientov vhoda u(k) po postopku porazdeljene aritmetike. Pri tem postopku vrednost vhodnega otipka u(k) zapišemo v bitni obliki z dvojiškim komplimentom. Zapis opisuje enačba

$$u(k) = -b_{u,0}(k) + \sum_{i=1}^{Bu-1} b_{u,i}(k) 2^{-i}.$$

(7)

V enačbi (7) najbolj utežni bit  $b_{u,0}(k)$  predstavlja predznak k-tega otipka vhodne besede u(k). Vektor koeficientov vhoda  $\mathbf{u}(k)$  na bitnem nivoju zapišemo z upoštevanjem dvojiškega komplimenta z

$$\mathbf{u}(k) = \begin{bmatrix} b_{u,0}(k-1) + \sum_{i=1}^{Bu-1} b_{u,i}(k-1)2^{i} \\ b_{u,0}(k-2) + \sum_{i=1}^{Bu-1} b_{u,i}(k-2)2^{i} \\ \vdots \\ b_{u,0}(k-N) + \sum_{i=1}^{Bu-1} b_{u,i}(k-N)2^{i} \end{bmatrix}.$$

(8)

Pri adaptivnih sitih se vektor koeficientov h(k) spremeni pri vsakem otipku vhodnega signala u(k), zato ni potrebno opraviti izračuna celotnega nabora delnih vsot koeficientov  $v_i$ . Z uporabo sprotnega izračuna delnih vsot koeficientov, neposredno izračunavamo vektor delnih vsot koeficientov v(k) iz otipka vhodne besede u(k) in vektorja koeficientov h(k) po enačbi

$$\mathbf{v}(k) = \mathbf{b}_{u}^{T}(k)\mathbf{h}(k) \tag{9}$$

V enačbi (9) je vektor  $\mathbf{b}_u(k)$  bitni zapis trenutnega vhodnega otipka signala  $\mathbf{u}(k)$  in ostalih petnajstih predhodnih vrednosti signala  $\mathbf{u}(k)$ . Pri tem k-ti otipek vrednosti vektorja  $\mathbf{b}_u(k)$  zapišemo z

$$\mathbf{b}_{u}(k) = \begin{bmatrix} b_{u,0}(k-1) & b_{u,1}(k-1) & \cdots & b_{u,B-1}(k-1) \\ b_{u,0}(k-2) & b_{u,1}(k-2) & \cdots & b_{u,B-1}(k-2) \\ \vdots & \vdots & \vdots & \vdots \\ b_{u,0}(k-N) & b_{u,1}(k-N) & \cdots & b_{u,B-1}(k-N) \end{bmatrix} . (10)$$

V enačbi (9) je vektor delnih vsot koeficientov  $\mathbf{v}(k)$ , funkcija vektorja  $\mathbf{b}_{u}(k)$  in vektorja koeficientov sita  $\mathbf{h}(k)$ . Z množenjem obeh matrik  $\mathbf{h}(k)$  in  $\mathbf{u}(k)$  dobimo matriko delnih vsot koeficientov  $\mathbf{v}(k)$ , ki se neposredno izračunava v FIR situ ob vsakem novem otipku vhodne besede  $\mathbf{u}(k)$  po enačbi (9). Dobljeni vektor delnih vsot koeficientov  $\mathbf{v}(k)$  za k-ti otipek vhodne besede  $\mathbf{u}(k)$  zapišemo z

$$\mathbf{v}(k) = \begin{bmatrix} h_0(k)b_{u,0}(k-1) + \dots + h_{N-1}(k)b_{u,0}(k-N) \\ h_0(k)b_{u,1}(k-1) + \dots + h_{N-1}(k)b_{u,1}(k-N) \\ \vdots \\ h_0(k)b_{u,Bu-1}(k-1) + \dots + h_{N-1}(k)b_{u,Bu-1}(k-N) \end{bmatrix} . (11)$$

Matrika vektorja delnih vsot koeficientov  $\mathbf{v}(k)$  ima dimenzijo  $B_U \times N$ .  $B_U$  je število bitov za zapis vhodne besede  $\mathbf{u}(k)$ . Za izračun matrike vektorja je potrebno  $B_U$  iteracij. Aparaturna kompleksnost enote FIR sita se zaradi povečanja iteracij ne spremeni, poveča se le potreben čas izračuna izhodne besede  $\mathbf{y}(k)$ . Enačbo vektorja delnih vsot koeficientov FIR sita  $\mathbf{v}(k)$  zaradi preglednosti zapišimo v krajši obliki

$$\mathbf{v}(k) = \begin{bmatrix} \sum_{i=0}^{Bu-1} h_i(k)b_0(k-(N+1)) \\ \sum_{i=0}^{Bu-1} h_i(k)b_1(k-(N+1)) \\ \vdots \\ \sum_{i=0}^{Bu-1} h_i(k)b_{Bu-1}(k-(N+1)) \end{bmatrix}.$$

(12)

V enačbi (12) so  $v_i(k)$  komponente vektorja delnih vsot koeficientov. Za sito z N koeficienti dobimo za vsak nov otipek vhodnega signala u(k) N novih komponent delnih vsot koeficientov  $v_i(k)$ . Pri izvedbi adaptivnega FIR sita smo se odločili za strukturo sprotnega izračuna vektorja delnih vsot koeficientov  $\mathbf{v}(k)$ . Tako dobljeni vektor koeficientov  $\mathbf{v}(k)$  ima dimenzijo N in vsebuje naslednje komponente,

$$\mathbf{v}(k) = \begin{bmatrix} v_1(k) \\ v_2(k) \\ v_{Bu}(k) \end{bmatrix}$$

(13)

Izračun izhodne besede FIR sita y(k) poteka neposredno iz komponent vektorja delnih vsot koeficientov po enačbi (6). Za izračun izhodne y(k) je potrebno izvesti B<sub>U</sub> iteracij.

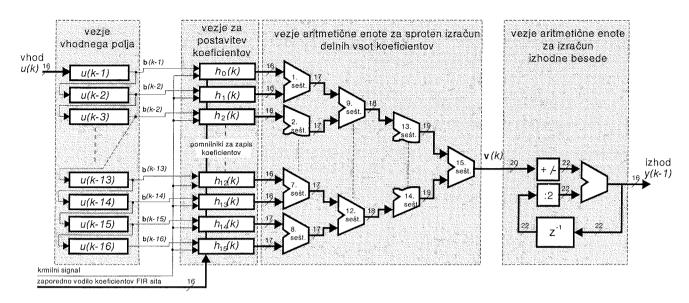

### 2.1.2 Aparaturna izvedba enote FIR digitalnega sita s spremenljivimi koeficienti

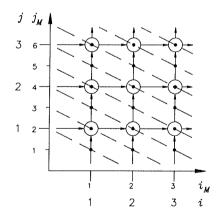

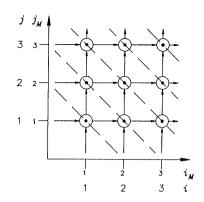

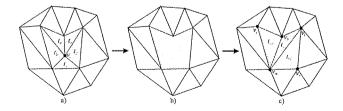

Z FPGA vezjem XC4013E firme Xilinx smo realizirali enoto FIR sita z N=16 koeficienti, z B<sub>u</sub>=16-bitno dolžino vhodne besede in 16-bitno dolžino izhodne besede in dolžino notranje strukture med 16 in 22 biti. Dosegli smo frekvenco vzorčenja vhodne besede f<sub>v</sub>=100kHz pri frekvenci osnovnega signala ure 20MHz.. Izvedbo enote FIR sita v porazdeljeni aritmetiki razdeljeno na N=16 podstruktur prikazuje slika 3.

Realizacijsko enoto FIR digitalnega sita smo razdelili na štiri različna vezja. V enoti FIR digitalnega sita sta vezje vhodnega polja in vezje aritmetične enote enaki kot pri klasični izvedbi adptivnega FIR sita v porazdeljeni aritmetiki /5/. Vezje za postavitev koeficientov in vezje aritmetične enote za sprotni izračun delnih vsot koeficientov smo načrtali posebej za aplikacijo FIR sita s spremenljivimi koeficienti.

Slika 3: Blokovna shema enote digitalnega FIR sita v porazdeljeni aritmetiki razdeljenega na N=16 podstruktur

Vezje vhodnega polja opravlja izračun vektorja  $b_u(k)$  po enačbi (10), pri tem ima vektor dimenzijo  $B_u$ =16 stolpcev in N=16 vrstic.

Vezje za postavitev koeficientov skrbi samo za prenos vektorja koeficientov h(k) iz vezja za izračun vektorja koeficientov h(k) v enoto FIR sita in njegovo pretvorbo iz zaporedne oblike zapisa v vzporedno obliko zapisa. Vezje je sestavljeno iz šestnajstih 16-bitnih zaporedno vzporednih pretvornikov.

Vezje aritmetične enote za sproten izračun delnih vsot koeficientov izračunava vektor delnih vsot koeficientov v(k) po enačbi (9), pri tem ima vektor v(k) N=16 vrstic. Izračun vektorja v(k) se opravi po B<sub>u</sub>=16 iteracijah. Vezje sestavlja 15 seštevalnikov, ki so dolžine od 16. do 19. bitov.

Vektor delnih vsot koeficientov se izračuna po B<sub>u</sub>=16 iteracijah. Vezje aritmetične logične enote izračunava vrednost izhodne besede y(k) po enačbi (11) oz (12). Za izračun je potrebno B<sub>u</sub>=16 iteracij.

**Vezje aritmetične enote** za izračun izhodne besede y(k) po enačbi (6) potrebuje B<sub>U</sub>=16 iteracij.

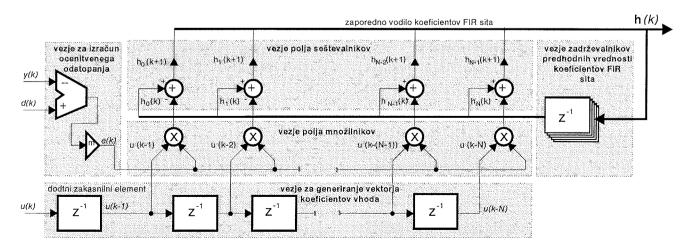

#### 2.2 Enota za izračun koeficientov

Izračun vektorja koeficientov h(k) adaptivnega FIR digitalnega sita poteka po algoritmu, ki skrbi za optimalno nastavljanje parametrov sita. Izračun temelji na kriteriju najmanjšega srednjega kvadratičnega odstopanja, kjer se optimalni koeficienti izračunajo z metodo strmega spusta /1/. Ta način je izbran zaradi matematične enostavnosti in robustnosti algoritme izračuna. Izbrani LMS kriterij zadostuje pogoju glede aparaturne kompleksnosti enote za izračun koeficientov, časa adaptacije in izračuna koeficientov sita v realnem času. Glede na izračun koeficientov FIR sita po LMS kriteriju z algoritmom strmega spusta ločimo: izračun koeficientov s predznačeno funkcije, izračun koeficientov

z nespremenljivo adaptivno konstanto in izračun koeficientov s spremenljivo adaptivno konstanto.

#### 2.2.1 Opis izračuna koeficientov FIR sita

Izračun novih koeficientov sita poteka v dveh korakih. V prvem koraku je potrebno izvesti izračun ocenitvenega odstopanja med primarnim signalom d(k) in izhodnim signalom y(k) po enačbi (2). V drugem koraku je potrebno izvesti izračun novega vektorja koeficientov FIR sita h(k) po enačbi (3). Enačbo (3) razdelimo na dva dela. Del s predhodnimi vrednostmi vektorja koeficientov FIR sita h(k-1) in del z vektorjem trenutnega odstopanja koeficientov FIR sita h'(k),

$$\mathbf{h}(k) = \mathbf{h}(k-1) + \mathbf{h}'(k). \tag{14}$$

V enačbi (14) je izračun vektorja trenutnega odstopanja koeficientov h'(k) za aparaturno izvedbo najkompleksnejši del. Izračun tega vektorja poteka po enačbi

$$\mathbf{h'}(k) = \mu e(k)\mathbf{u}(k). \tag{15}$$

V enačbi (15) je najprej izvedeno množenje ocene odstopanja e(k) z adaptivno konstanto  $\mu$ . Pri tem je dobljen zmnožek med e(k) in  $\mu$  skalar, s katerim v naslednjem koraku izračuna pomnožimo vektor koeficientov vhoda  $\mathbf{u}(k)$  z enačbo

$$\mathbf{h'}(k) = \mu e(k)\mathbf{u}(k) = \begin{bmatrix} \mu e(k)u(k-1) \\ \mu e(k)u(k-2) \\ \vdots \\ \mu e(k)u(k-N) \end{bmatrix}$$

(16)

Ta izračun smo realizirali s postopkom porazdeljene aritmetike. Vektor vhodnih koeficientov  $\mathbf{u}(k)$  vhodnega refe-