### **NFORMACIJE**

Strokovno društvo za mikroelektroniko elektronske sestavne dele in materiale

3.2007

Strokovna revija za mikroelektroniko, elektronske sestavne dele in materiale Journal of Microelectronics, Electronic Components and materials

INFORMACIJE MIDEM, LETNIK 37, ŠT. 3(123), LJUBLJANA, september 2007

#### **INFORMACIJE**

### **MIDEM**

**3** ° 2007

INFORMACIJE MIDEM

LETNIK 37, ŠT. 3(123), LJUBLJANA,

SEPTEMBER 2007

INFORMACIJE MIDEM

VOLUME 37, NO. 3(123), LJUBLJANA,

SEPTEMBER 2007

Revija izhaja trimesečno (marec, junij, september, december). Izdaja strokovno društvo za mikroelektroniko, elektronske sestavne dele in materiale - MIDEM. Published quarterly (march, june, september, december) by Society for Microelectronics, Electronic Components and Materials - MIDEM.

Glavni in odgovorni urednik

Editor in Chief

Dr. Iztok Šorli, univ. dipl.inž.fiz., MIKROIKS, d.o.o., Ljubljana

Tehnični urednik Executive Editor Dr. Iztok Šorli, univ. dipl.inž.fiz., MIKROIKS, d.o.o., Ljubljana

Uredniški odbor Editorial Board Dr. Barbara Malič, univ. dipl.inž. kem., Institut "Jožef Stefan", Ljubljana Prof. dr. Slavko Amon, univ. dipl.inž. el., Fakulteta za elektrotehniko, Ljubljana Prof. dr. Marko Topič, univ. dipl.inž. el., Fakulteta za elektrotehniko, Ljubljana

Prof. dr. Rudi Babič, univ. dipl.inž. el., Fakulteta za elektrotehniko, računalništvo in informatiko

Maribor

Dr. Marko Hrovat, univ. dipl.inž. kem., Institut "Jožef Stefan", Ljubljana Dr. Wolfgang Pribyl, Austria Mikro Systeme Intl. AG, Unterpremstaetten

Časopisni svet International Advisory Board Prof. dr. Janez Trontelj, univ. dipl.inž. el., Fakulteta za elektrotehniko, Ljubljana,

PREDSEDNIK - PRESIDENT

Prof. dr. Cor Claeys, IMEC, Leuven

Dr. Jean-Marie Haussonne, EIC-LUSAC, Octeville Darko Belavič, univ. dipl.inž. el., Institut "Jožef Stefan", Ljubljana

Prof. dr. Zvonko Fazarino, univ. dipl.inž., CIS, Stanford University, Stanford

Prof. dr. Giorgio Pignatel, University of Padova

Prof. dr. Stane Pejovnik, univ. dipl.inž., Fakulteta za kemijo in kemijsko tehnologijo, Ljubljana

Dr. Giovanni Soncini, University of Trento, Trento

Prof. dr. Anton Zalar, univ. dipl.inž.met., Institut Jožef Stefan, Ljubljana Dr. Peter Weissglas, Swedish Institute of Microelectronics, Stockholm

Prof. dr. Leszek J. Golonka, Technical University Wrocław

Naslov uredništva Headquarters Uredništvo Informacije MIDEM

MIDEM pri MIKROIKS

Stegne 11, 1521 Ljubljana, Slovenija tel.: + 386 (0)1 51 33 768 faks: + 386 (0)1 51 33 771 e-pošta: Iztok.Sorli@guest.arnes.si http://www.midem-drustvo.si/

Letna naročnina je 100 EUR, cena posamezne številke pa 25 EUR. Člani in sponzorji MIDEM prejemajo Informacije MIDEM brezplačno. Annual subscription rate is EUR 100, separate issue is EUR 25. MIDEM members and Society sponsors receive Informacije MIDEM for free.

Znanstveni svet za tehnične vede je podal pozitivno mnenje o reviji kot znanstveno-strokovni reviji za mikroelektroniko, elektronske sestavne dele in materiale. Izdajo revije sofinancirajo ARRS in sponzorji društva.

Scientific Council for Technical Sciences of Slovene Research Agency has recognized Informacije MIDEM as scientific Journal for microelectronics, electronic components and materials.

Publishing of the Journal is financed by Slovene Research Agency and by Society sponsors.

Znanstveno-strokovne prispevke objavljene v Informacijah MIDEM zajemamo v podatkovne baze COBISS in INSPEC.

Prispevke iz revije zajema ISI® v naslednje svoje produkte: Sci Search®, Research Alert® in Materials Science Citation Index™

Scientific and professional papers published in Informacije MIDEM are assessed into COBISS and INSPEC databases.

The Journal is indexed by ISI® for Sci Search®, Research Alert® and Material Science Citation Index™

Po mnenju Ministrstva za informiranje št.23/300-92 šteje glasilo Informacije MIDEM med proizvode informativnega značaja.

Grafična priprava in tisk

BIRO M, Ljubljana

Printed by

1000 izvodov

Naklada Circulation

1000 issues

Poštnina plačana pri pošti 1102 Ljubljana

Slovenia Taxe Percue

| ZNANSTVENO STROKOVNI PRISPEVKI                                                                                                                                                                                      |     | PROFESSIONAL SCIENTIFIC PAPERS                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T. Belmonte, R.P. Cardoso, C. Noël,<br>G. Henrion, F. Kosior:<br>Značilnosti argonske in helijeve plazme ustvarjene z<br>mikrovalovno razelektritvijo pri atmosferskem tlaku                                        | 117 | T. Belmonte, R.P. Cardoso, C. Noël,<br>G. Henrion, F. Kosior:<br>Characteristics of argon and helium plasmas created<br>by microwave discharge at atmospheric pressure                                    |

| P. Eiselt:<br>Interakcija visoko disociirane kisikove plazme s<br>polimeri in njihovimi kompoziti                                                                                                                   | 123 | P. Eiselt: Interaction of highly dissociated oxygen plasma with polymers and their composites                                                                                                             |

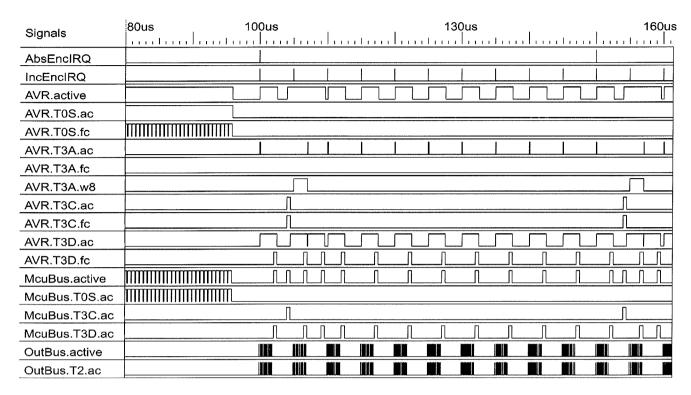

| K.Perko, A.Trost:<br>Grafično okolje za raziskovanje načrtovalskega<br>prostora na nivoju sistemov                                                                                                                  | 132 | K.Perko, A.Trost:<br>Graphical framework for system level design space<br>exploration                                                                                                                     |

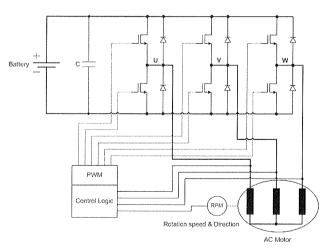

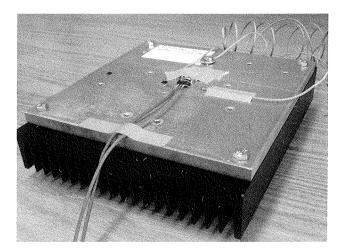

| J.Podržaj, J.Trontelj:<br>Načrtovalski vidiki za močnostne krmilnike<br>elektromotorjev                                                                                                                             | 142 | J.Podržaj, J.Trontelj:<br>Design consideration for power modules of<br>electro-motor drives                                                                                                               |

| A.Biasizzo:<br>Analiza možnih scenarijev vdora v sisteme z vgrajeno<br>varnostno razširitvijo standarda IEEE 1149.1                                                                                                 | 146 | A.Biasizzo:<br>Analysis of potential attack scenarios for systems<br>with IEEE Std 1149.1 security extension                                                                                              |

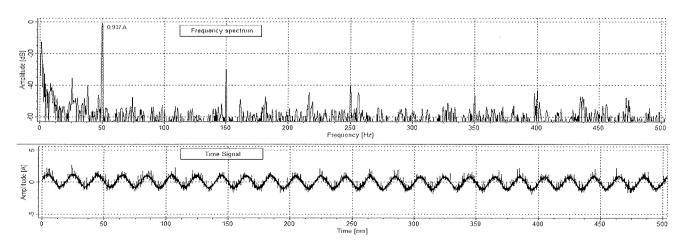

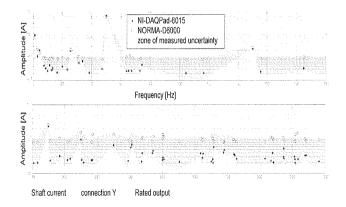

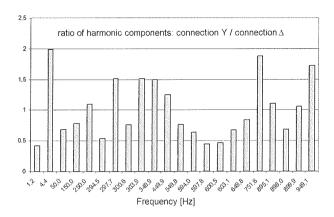

| S.Štefanko, Ž.Hederić,<br>M.Hadžiselimović, I.Zagradišnik<br>Analiza meritev tokov gredi nizkonapetostnega<br>asinhronskega motorja za pogon viličarja z<br>elektronsko opremo                                      | 152 | S.Štefanko, Ž.Hederić,<br>M.Hadžiselimović, I.Zagradišnik<br>Analyses of shaft currents in low-voltage induction<br>motor for forklift drive with electronic equipment                                    |

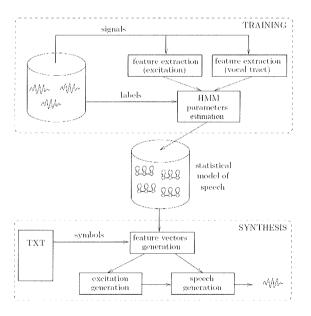

| J.Žganec Gros, M. Žganec:<br>Postopek za izbiro govornih segmentov pri vgrajeni<br>polifonski združevalni sintezi govora                                                                                            | 158 | J.Žganec Gros, M. Žganec:<br>An efficient unit-selection method for embedded<br>concatenative speech synthesis                                                                                            |

| M. B. I. Reaz, M. I. Ibrahimy,<br>F. Mohd-Yasin, C. S. Wei, M. Kamada:<br>Elektronski modul za izvedbo šifriranja v TECB načinu                                                                                     | 165 | M. B. I. Reaz, M. I. Ibrahimy,<br>F. Mohd-Yasin, C. S. Wei, M. Kamada:<br>Single core hardware module to implement<br>encryption in TECB mode                                                             |

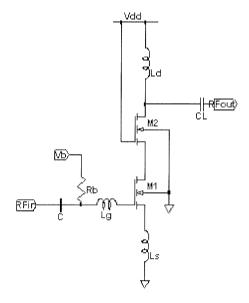

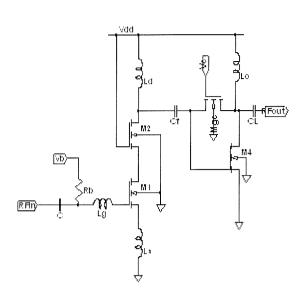

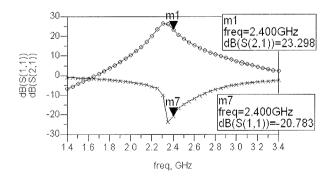

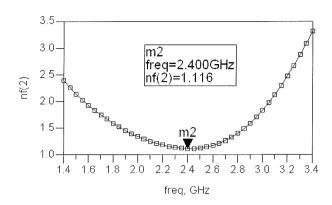

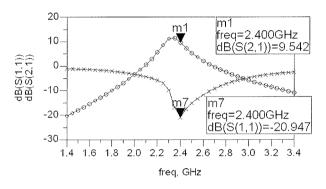

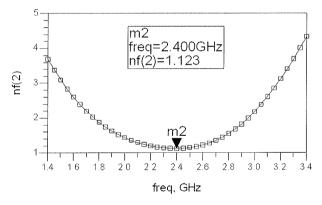

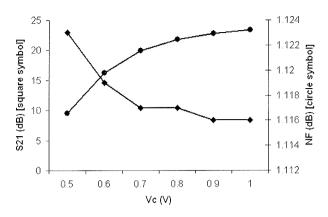

| L.Lee, R.Mohd Sidek, S.Shekhar Jamuar, S.Khatun:<br>Kontrolna zanka ojačanja za 2.4GHz nizkošumni<br>ojačevalnik s spremenljivim ojačanjem (VGLNA)                                                                  | 172 | L.Lee, R.Mohd Sidek, S.Shekhar Jamuar, S.Khatun:<br>Gain control loop for a 2.4 GHz variable gain low<br>noise amplifier (VGLNA)                                                                          |

| F.Mihelič, B.Vesnicer, J.Žibert, E.Nöth:<br>Ocenjevenje prozodije za vgrajene sisteme za sintezo<br>slovenskega govora                                                                                              | 176 | F.Mihelič, B.Vesnicer, J.Žibert, E.Nöth:<br>Prosody evaluation for embedded slovene speech-<br>synthesis systems                                                                                          |

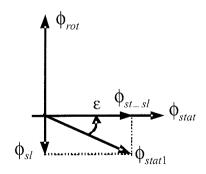

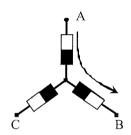

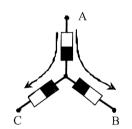

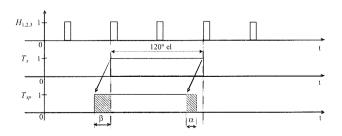

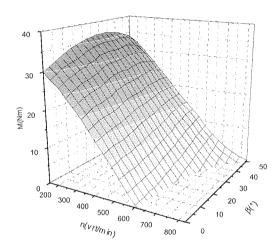

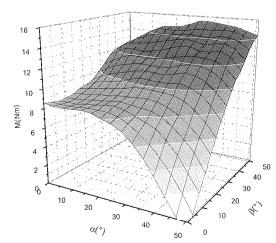

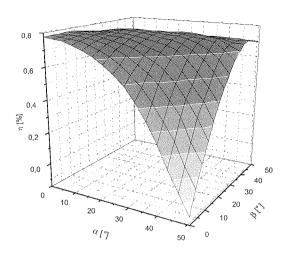

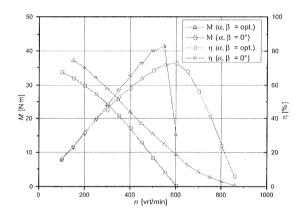

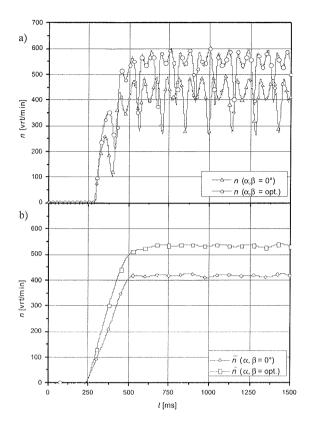

| B.Pevec, P.Bajec, J.Nastran, D.Vončina:<br>Optimizacija navorne karakteristike elektronsko<br>komutiranega motorja v hibridnem pogonu                                                                               | 182 | B.Pevec, P.Bajec, J.Nastran, D.Vončina:<br>Torque characteristic optimization of brushless DC<br>motor in the hybrid vehicle                                                                              |

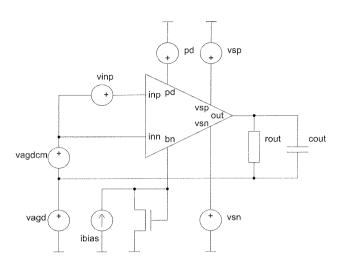

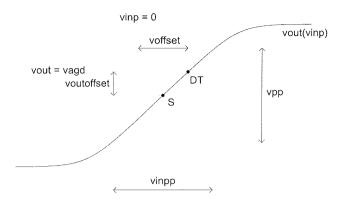

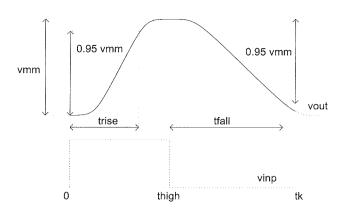

| J.Puhan, Á.Burmen, S.Tomažic, T.Tuma:<br>Definicija kriterijske funkcije za rubustno optimizacijo<br>lastnosti operacijskega ojacevalnika                                                                           | 189 | J.Puhan, Á.Burmen, S.Tomažic, T.Tuma:<br>Cost function definition for robust optimisation of<br>operational amplifier                                                                                     |

| MIDEM prijavnica                                                                                                                                                                                                    | 195 | MIDEM Registration Form                                                                                                                                                                                   |

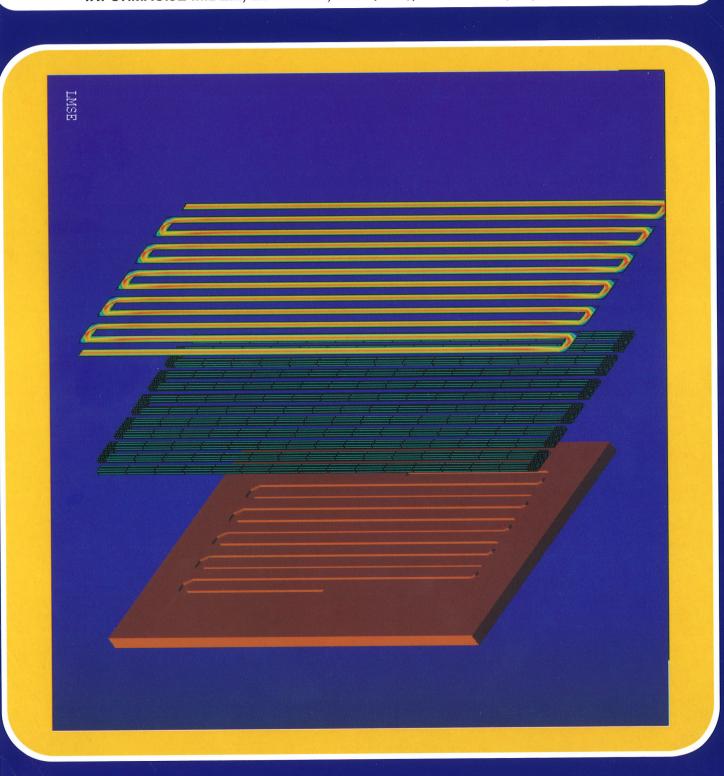

| Slika na naslovnici:<br>RR aktivnosti na področju mikrofluidnih struktur v<br>LMSE, UL FE<br>LMSE - Labaratorij za mikrosenzorske strukture in<br>elektroniko, Univerza v Ljubljani,<br>Fakulteta za elektrotehniko |     | Front page: R&D activities in the field of microfluidic structures in LMSE, UL FE LMSE - Laboratory of Microsensor Structures and Electronics, University of Ljubljana, Faculty of Electrical Engineering |

| Fakulteta za elektrotehniko                                                                                                                                                                                         |     | Faculty of Electrical Engineering                                                                                                                                                                         |

**VSEBINA**

CONTENT

### Obnovitev članstva v strokovnem društvu MIDEM in iz tega izhajajoče ugodnosti in obveznosti

Spoštovani,

V svojem več desetletij dolgem obstoju in delovanju smo si prizadevali narediti društvo privlačno in koristno vsem članom. Z delovanjem društva ste se srečali tudi vi in se odločili, da se v društvo včlanite. Življenske poti, zaposlitev in strokovno zanimanje pa se z leti spreminjajo, najrazličnejši dogodki, izzivi in odločitve so vas morda usmerili v povsem druga področja in vaš interes za delovanje ali članstvo v društvu se je z leti močno spremenil, morda izginil. Morda pa vas aktivnosti društva kljub temu še vedno zanimajo, če ne drugače, kot spomin na prijetne čase, ki smo jih skupaj preživeli. Spremenili so se tudi naslovi in način komuniciranja.

Ker je seznam članstva postal dolg, očitno pa je, da mnogi nekdanji člani nimajo več interesa za sodelovanje v društvu, se je Izvršilni odbor društva odločil, da stanje članstva uredi in vas zato prosi, da izpolnite in nam pošljete obrazec priložen na koncu revije.

Naj vas ponovno spomnimo na ugodnosti, ki izhajajo iz vašega članstva. Kot član strokovnega društva prejemate revijo »Informacije MIDEM«, povabljeni ste na strokovne konference, kjer lahko predstavite svoje raziskovalne in razvojne dosežke ali srečate stare znance in nove, povabljene predavatelje s področja, ki vas zanima. O svojih dosežkih in problemih lahko poročate v strokovni reviji, ki ima ugleden IMPACT faktor. S svojimi predlogi lahko usmerjate delovanje društva.

Vaša obveza je plačilo članarine 25 EUR na leto. Članarino lahko plačate na transakcijski račun društva pri A-banki: 051008010631192. Pri nakazilu ne pozabite navesti svojega imena!

Upamo, da vas delovanje društva še vedno zanima in da boste članstvo obnovili. Žal pa bomo morali dosedanje člane, ki članstva ne boste obnovili do konca leta 2007, brisati iz seznama članstva.

Prijavnice pošljite na naslov:

MIDEM pri MIKROIKS

Stegne 11

1521 Ljubljana

Ljubljana, september 2007

Izvršilni odbor društva

# CHARACTERISTICS OF ARGON AND HELIUM PLASMAS CREATED BY MICROWAVE DISCHARGE AT ATMOSPHERIC PRESSURE

T. Belmonte<sup>\*</sup>, R.P. Cardoso, C. Noël, G. Henrion, F. Kosior Laboratoire de Science et Génie des Surfaces, Nancy-Université, CNRS, Nancy Cedex, France

Key words: Microwave plasma, atmospheric pressure.

**Abstract:** A review of recent developments in the field of microwave plasmas created in noble gases at atmospheric pressure is presented. Several possible designs of discharge configuration are presented and the evolution of plasma jet is explained. The contraction and filamentation of plasma is explained and illustrated. Such plasma is characterized by a high temperature of both neutral and ionized gaseous atoms, which can easily reach several 1000K. The electron temperature is often between 15000 and 30000K, and the electron density usually exceeds  $10^{20} \, \text{m}^{-3}$ . At such conditions, several reactions untypical for low pressure plasmas occur. Among them, formation of dimmers is of particular interest. In some cases, the density of dimmers such as  $\text{He}_2^+$  may exceed the density of common  $\text{He}_2^+$  ions.

### Značilnosti argonske in helijeve plazme ustvarjene z mikrovalovno razelektritvijo pri atmosferskem tlaku

Kjučne besede: mikrovalovna plazma, atmosferski tlak

Izvleček: V prispevku opisujemo zadnja dognanja na področju mikrovalovne plazme, ki jo ustvarimo v žlahtnih plinih pri atmosferskem tlaku. Opisujemo nekatere možne konfiguracije razelektritve in razložimo razvoj plazemskega curka znotraj razelektritve. Curek plazme se pri teh razmerah običajno zoži znotraj razelektritvene cevi, pojavljo pa se tudi plazemske niti, kar ilustriramo in razložimo v tem prispevku. Takšno plazmo odlikuje visoka temperatura nevtralnega plina in ioniziranih atomov, ki zlahka doseže več 1000K. Temperatura elektronov je pogosto med 15000 in 30000K, medtem ko njihova gostota običajno preseže vrednost 10<sup>20</sup> m<sup>-3</sup>. Pri takšnih razmerah opazimo nekatere reakcije, ki niso značilne za nizkotlačne plazme. Med njimi je posebej zanimiva tvorba dvoatomnih molekul žlahtnih plinov. V nekaterih primerih, kot npr. He<sub>2</sub><sup>+</sup>, lahko gostota takšnih molekul celo preseže gostoto običajnih helijevih ionov He<sup>+</sup>.

#### 1. Introduction

High frequency plasmas are widely spread sources of active species which can be used in various applications /1-42/. When these sources are set up on processes working at atmospheric pressure, lower cost treatments can be achieved if efficiency is unchanged with respect to processes under low pressure. Therefore, there is a need to better understand and characterize high pressure sources to optimize the treatments /43-59/.

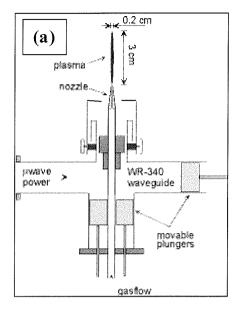

Microwave plasmas in CW mode operate at high treatment temperatures, namely a few thousands Kelvin. Several sources are widely studied like surface wave excited plasmas /60-64/, waveguide-based microwave torches, like the "Torche à Injection Axiale" /65-72/ and resonant cavities /73-76/. In Fig. 1, three sources are presented showing possible designs for atmospheric pressure microwave plasmas. The plasma is either created in open air, confined without wall contact or guided by a fused silica tube where the electric field propagates. Some of these sources cannot operate at high power since fused silica which is commonly employed as confinement vessel melts at ~2000 K. Discharges in rare gases are mostly studied, especially in argon and helium. Beyond design and arrange-

ment of the sources, strong efforts, both theoretical and experimental, were performed recently to better understand the physical processes that govern these plasmas. However, complementary studies are still necessary to improve our knowledge on these small-scale plasmas where huge gradients exist. Indeed, diagnostics with high spatial resolution are needed. Some basic data for kinetic processes and even for some species should be determined experimentally at high temperature. This would help develop predictive self-consistent collisional radiative models in optically thick media.

In the present paper, we review recent advances in microwave sources at atmospheric pressure. We describe the difficulties to overcome in order to progress in the understanding of these plasmas. The outline of the paper is then as follows: In section 2, a special attention is paid to recent theories available to describe contraction of some rare gas plasmas. A brief comment will also be given on filamentation. In section 3, we present the most relevant question on basic data needed in the field of atmospheric microwave sources. Finally, concluding remarks are provided in section 4.

Fig. 1: Some possible designs of microwave sources operating at atmospheric pressure. (a) The "Torche à Injection Axiale" /65/, (b) resonant cavity /73/ and (c) surfaguide wave launcher /60/. The plasma can be sustained in open air, confined without wall contact or guided along a dielectric, respectively.

### 2. Contraction and filamentation in rare gas plasmas

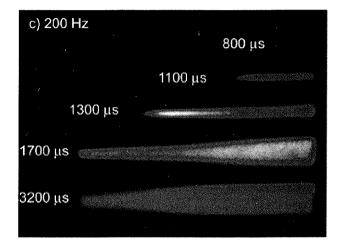

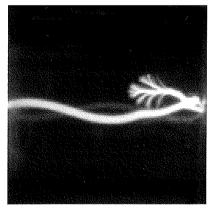

Contraction can be defined as the compression of plasma into a filament located at the discharge axis. It can be observed in various gases and excitation sources, not only microwave (see Fig. 2). It is characterized by a local increase in both the electron density and the gas temperature and by a decrease in the electron temperature. In the other hand, filamentation is observed only in high frequency discharges only. One single plasma filament splits into two or more filaments of smaller diameters /77, 78/ once the electron density is sufficiently increased radially.

Fig. 2: Illustration of contraction (left) and filamentation (right) phenomena. Left figure is the time evolution of a neon plasma column sustained at atmospheric pressure at 200 Hz (after /78/). Right figure is an argon plasma sustained in a microwave resonant cavity at atmospheric pressure pulsed at 2kHz (duty cycle is 41%).

Recently, study of contraction has gained interest because of the potentialities of these plasmas at atmospheric pressure. Two main mechanisms relying on the same idea, the radial decrease in the ionization rate, can be evoked to explain the contraction process. The first one deals with electron-electron collisions. Energetic electrons which are depleted by inelastic collision can be heated by electron-electron collisions that tend to give a Maxwellian distribu-

tion. However, this mechanism is only possible if the electron density is high enough, usually close to the discharge axis. Then, at the edge of the plasma, the tail of electron energy distribution function is likely depleted and the ionization rate decreases radially /79-80/. The second possible explanation is nonuniform heating of the gas along the discharge radius. It creates contraction through its influence on the kinetics of dimer ions, which controls the charged-particle balance. These descriptions rely on basic data that now need to be examined in detail for rare gases. Helium and argon are considered next.

#### 3. Basic data

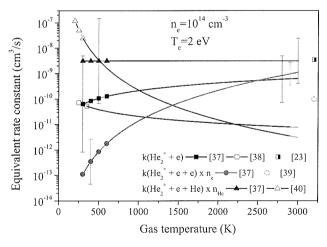

A common difficulty present in available works deals with the temperature dependence of rate constant of chemical reactions over wide ranges. Indeed, depending on the power delivered to the plasma, the temperature of the gas can vary over large range of values. Moreover, due to high temperature gradients, it varies spatially. The main consequence of this change in the gas temperature is the control of the kinetics of excimers, whether they are neutral or charged. There is no measurement on the excimer density nor on their vibrational distribution above 1500 K. In Fig. 3, we give an overview of the gas temperature dependence of the rate constant for the three possible recombination processes of He<sub>2</sub><sup>+</sup> ions /81-84/. Available data are spread over a wide range of values and experimental data are all given below 600 K.

Fig. 3: Equivalent two-body rate constants for recombination processes of He<sub>2</sub><sup>+</sup> ions as a function of the gas temperature. An electron temperature of 2 eV and an electron density of 10<sup>14</sup> cm<sup>-3</sup> are chosen. Data deduced from experiments are by /81/-/84/. Data used by /67/ is added for comparison. Extrapolations of available temperature dependences over the range [300-3200 K] are also given (solid lines). When available, the accuracy of the equivalent rate constant is reported.

Let's consider for example the case of  ${\rm He}^+$  and  ${\rm He_2}^+$  ions in helium atmospheric microwave discharges where several difficulties arise. Dimer ions are mainly produced from  ${\rm He}^+$  by a three-body collision:

$$He^+ + He + He \rightarrow He_2^+ + He$$

(1)

with a rate constant of 1.2  $\pm$  0.2 x 10<sup>-31</sup> cm<sup>6</sup> s<sup>-1</sup> at 300 K /85, 86/.

First, the temperature dependence of this process, extrapolated from data by Böhringer /85/ measured between 50 K and 350 K ( $T_g^{-0.60\pm0.10}$ ) is rather different from that determined by Russel /86/ between 80 K and 300 K ( $T_g^{-0.38\pm0.06}$ ). However, the two sets of experimental data differ by less than 30%. The accuracy of the measurements within this range of temperature is probably not high enough to determine correctly the exponent of the power law. The former dependence was used for example by /67/ to determine to role of dimer ions between 500 K and 3000 K.

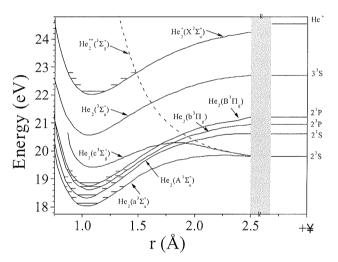

Fig. 4: Energy diagram of helium dimers. The doubly excited state He<sub>2</sub>\*\* is an antibonding triplet state intersecting the dimer ion close to the v=3 vibrational level.

Second, to estimate the ratio [He<sub>2</sub><sup>+</sup>]/[He<sup>+</sup>], three main processes are considered by /67/ to account for the reaction pathways possibly followed by He2+: direct electron recombination, He<sub>2</sub><sup>+</sup> creation by reaction (1) and loss by the reverse process, dissociation of dimer ions by electron impact being negligible. Assuming the Saha equilibrium, the rate constant of the reverse process of reaction (1) is estimated. This choice gives a ratio [He<sub>2</sub><sup>+</sup>]/[He<sup>+</sup>]~0.55 at 2500 K for n<sub>e</sub>=10<sup>14</sup> cm<sup>-3</sup>, i.e. similar number densities for the two species. The rate constant used for direct electron recom-. bination is 5.0 x 10<sup>-9</sup>  $/T_e^{0.5}$  cm<sup>3</sup> s<sup>-1</sup> where  $T_e$  is the electron temperature in eV. This rate constant is given with no gas temperature dependence. However, it does depend on it as shown in recent works based on ring storage experiments. Indeed, due to the unfavourable location of the doubly excited potential energy curves (see Fig. 4), the recombination route and rate (Eq. (2)) of ions depend

both on the electron energy and the initial rovibrational distribution (/87-89/).

$$He_2^+(J,v)+e \rightarrow \{He_2^*; He_2^{**}\} \rightarrow He^* + He$$

Autoionization (2)

A competing process has to be taken into account, namely the autoionization of the intermediate Rydberg He<sub>2</sub>\* or doubly excited He<sub>2</sub>\*\* neutral molecule, which can fragment back into an electron and a molecular ion in the (J',v') rovibrational level.

The unusually low values of the direct recombination rate found in experimental works are at least partially explained (see /82, 90/ for details). The dependence of the rate of the direct recombination process with the electron temperature was determined to be  $\propto T_e^{-0.9}$  /90/. The gas temperature dependence is not available on a large range of temperatures. However, such dependence is available for neon dimer ions /91/. Results obtained confirm a fall-off in efficiency of the direct recombination for vibrationally excited rare-gas dimer ions with increasing temperature, the contribution of autoionisation being not negligible /92/. Direct recombination should only be considered at low temperature and high electron energy.

Therefore, the two-body recombination of electrons with dimer ions should not be considered at high temperature in the estimation made by /67/. In fact, this consideration does not change significantly the predicted result. Despite ambipolar diffusion prevails at 2500 K and is much lower than direct recombination as used by /67/, the density ratio He<sub>2</sub><sup>+</sup>/He<sup>+</sup> is nearly the same than that these authors found. One of the two processes, the atom assisted association or its reverse process, has rate always much higher than the loss of He2+ by recombination or ambipolar diffusion which are known to be slow recombination processes. If the absolute value of the density of He2+ depends on direct and reverse rates of atom assisted association, the density ratio  $He_2^+/He^+$  does not (see Eqs. 10 and 11 p 466 in /67/). In fact, to modify the temperature dependence of the density ratio He<sub>2</sub><sup>+</sup>/He<sup>+</sup>, one should either increase the rate of the recombination or decrease the rate of dissociation by atom impact. A last remark deals with the role of associative ionization. Rate constants for these processes at high temperature are unknown and the reaction processes should be included in the calculation of the density ratio He<sub>2</sub><sup>+</sup>/He<sup>+</sup> if they are not negligible.

Considering now the temperature dependence by Russel /86/, if the balance of association and dissociation via atom impact is in equilibrium, one should find a ratio  $He_2^+/He^+-9.2$  at 2500 K for  $n_e=10^{14}$  cm<sup>-3</sup>, showing that at high temperature,  $He_2^+$  ions may possibly still prevail.

In argon, these same authors find a ratio  ${\rm Ar_2}^+/{\rm Ar}^+ \sim 3.0 \times 10^{-3}$  at 2500 K for  ${\rm n_e}$ =10<sup>15</sup> cm<sup>-3</sup>, a result used by /63/ more recently. This difference between helium and argon is attributed to the dissociation energy of the dimers (2.4 eV

versus 1.3 eV), which is nearly twice higher for the former and only partially compensated by the larger partition function of argon ion dimers. Here again, no experimental data is available to determine how the  ${\rm Ar_2}^+/{\rm Ar}^+$  ratio evolves versus gas temperature.

The same kind of problem arises for excimer creation or associative ionization despite theoretical data are available in the case of this latter processes for some triplet states of helium /87/. However, only experimental measurements would confirm the validity of available estimations.

#### 4. Conclusion

Atmospheric microwave plasmas are high-temperature non-equilibrium media where complex phenomena that are still under investigation occur. Better understanding these media requires specific measurements to determine rate constants at high temperature. Diagnostics with high spatial and temporal resolutions are needed to provide basic data that lack today to provide satisfying description of these sources of active species.

#### 5. Acknowledgement

The authors are indebted to N. Sadeghi for fruitful discussion of atmospheric pressure plasmas. They wish also to acknowledge the *Coordenação de Aperfeiçoamento de Pessoal de Nível Superior* (CAPES), institution from the Brazilian government, for the doctoral scholarship grant of R. P. Cardoso.

#### References

- /1/ U. Cvelbar, M. Mozetic and M. Klanjsek-Gunde, IEEE Trans. Plasma Sci. 33, 236 (2005).

- /2/ M. Mozetic, Informacije-MIDEM **33**, 222 (2003).

- /3/ Ricard, V. Monna and M. Mozetic, Surf. Coat. Technol. 174-175, 905 (2003).

- /4/ K. Norikazu, H. Yamada, T. Yajima and K. Sugiyama, Thin Solid Films 515, 4192 (2007).

- /5/ R. Peelamedu, D. Kumar and S. Kumar, Surf. Coat. Technol. 201, 4008 (2006).

- /6/ A. Anders, Surf. Coat. Technol. 200, 1893 (2005).

- /7/ S. Guruvenket, G. Mohan Rao, Manoj Komath and Ashok M. Raichur, Appl. Surf. Sci. 236, 278 (2004).

- /8/ P. Ganachev and H. Sugai, Plasma Sources Sci. Technol. 11, A178 (2002).

- /9/ Ricard, M. Gaillad, V. Monna, A. Vesel and M. Mozetič, Surf. Coat. Technol. 142-144, 333 (2001).

- /10/ Vesel, M. Mozetič and A. Zalar, Appl. Surf. Sci. **200**, 94 (2002).

- /11/ Vesel, E. Vamvakopoulos, M. Mozetič and G. A. Evangelakis, Phys. B Condens. Matter. 324, 261 (2002).

- /12/ Drenik, U. Cvelbar, A. Vesel and M. Mozetič. Inf. MIDEM 35, 85 (2005).

- /13/ Vesel, M. Mozetič, A. Drenik, S. Milosevic, N. Krstulovic, M. Balat-Pichelin, I. Poberaj and D. Babič, Plasma Chem. Plasma Process 26, 577 (2006).

- /14/ M. Mozetič, A. Vesel, A. Drenik, I. Poberaj and D. Babič, J. Nucl. Mater. 363-365, 1457 (2007).

- /15/ T. Vrlinič, A. Vesel, U. Cvelbar, M. Krajnc and M. Mozetič, Surf. Interface Anal. **39**, 476 (2007).

- /16/ Vesel, M. Mozetic, A. Hladnik, J. Dolenc, J. Zule, S. Milosevic, N. Krstulovic, M. Klanjšek-Gunde and N. Hauptmann, J. Phys. D: Appl. Phys. 40, (2007) in press.

- /17/ U. Cvelbar, S. Pejovnik, M. Mozetič and A. Zalar, Appl. Surf. Sci. 210, 255 (2003).

- /18/ M. Mozetič, A. Zalar, U. Cvelbar and I. Poberaj, Appl. Surf. Sci. 211, 96 (2003).

- /19/ U. Cvelbar, M. Mozetič and A. Zalar, Vacuum 71, 207 (2003).

- /20/ M. Mozetič, A. Zalar, U. Cvelbar and D. Babič, Surf. Interface Anal. 36, 986 (2004).

- /21/ M. Mozetič and U. Cvelbar, Adv. Mater. 17, 2138 (2005).

- /22/ U. Cvelbar, M. Mozetič and A. Ricard, IEEE Trans. Plasma Sci. 33, 834 (2005).

- /23/ M. Klanjšek-Gunde, M. Kunaver, A. Hrovat and U. Cvelbar, Prog. Org. Coat. 54, 113 (2005).

- /24/ U. Cvelbar, M. Mozetič, I. Poberaj, D. Babič and A. Ricard, Thin Solid Films 475, 12 (2005).

- /25/ M. Klanjšek-Gunde, M. Kunaver, U. Cvelbar, N. Barle, Vacuum 80, 189 (2005).

- /26/ U. Cvelbar, B. Markoli, I. Poberaj, A. Zalar, L. Kosec and S. Spaić, Appl. Surf. Sci. 253, 1861 (2006).

- /27/ U. Cvelbar, D. Vujošević, Z. Vratnica and M. Mozetič, J. Phys. D: Appl. Phys. **39**, 3487 (2006).

- /28/ U. Cvelbar and M. Mozetič, J. Phys. D: Appl. Phys. 40, 2300 (2007).

- /29/ M. Mozetič, A. Zalar and M. Drobnič, Appl. Surf. Sci. 144-145, 399 (1999).

- /30/ M. Mozetič, A. Zalar and M. Drobnič, Thin solid films 343-344, 101 (1999).

- /31/ M. Mozetič and A. Zalar, Appl. Surf. Sci. **158**, 263 (2000).

- /32/ M. Mozetič, A. Zalar, P. Panjan, M. Bele, S. Pejovnik and R. Grmek, Thin Solid Films **376**, 5 (2000).

- /33/ M. Mozetič, Vacuum 61, 367 (2001).

- /34/ M. Kunaver, M. Klanjšek-Gunde, M. Mozetič and A. Hrovat, Dyes Pigm. **57**, 235 (2003).

- /35/ M. Mozetič and A. Zalar, Mater. Sci. Forum 437-438, 81 (2003).

- /36/ M. Kunaver, M. Klanjšek-Gunde, M. Mozetič, M. Kunaver and A. Hrovat, Surf. Coat. Int. B 86, 175 (2003).

- /37/ M. Mozetič and A. Zalar, Vacuum 71, 233 (2003).

- /38/ M. Mozetič, Vacuum **71**, 237 (2003).

- /39/ M. Klanjšek-Gunde, M. Kunaver, M. Mozetić and A. Hrovat, Powder Technol. **148**, 64 (2004).

- /40/ M. Kunaver, M. Mozetič and M. Klanjšek-Gunde, Thin Solid Films 459, 115 (2004).

- /41/ Hassanien, M. Tokumoto, P. Umek, D. Vrbanić, M. Mozetič, D. Mihailović, P. Venturini and S. Pejovnik, Nanotechnology 16, 278 (2005).

- /42/ Arčon, M. Mozetič and A. Kodre, Vacuum 80, 178 (2005).

- /43/ U. Cvelbar, M. Mozetič, D. Babič, I. Poberaj and A. Ricard, Vacuum 80, 904 (2006).

- /44/ M. Mozetič, Surf. Coat. Technol. 201, 4837 (2007).

- /45/ M. Balat-Pichelin and A. Vesel, Chem. Physic **327**, 112 (2006).

- /46/ Vesel and M. Mozetič, Vacuum **61**, 373 (2001).

- /47/ M. Mozetič, A. Vesel, V. Monna and A. Ricard, Vacuum 71, 201 (2003).

- /48/ M. Mozetič, U. Cvelbar, A. Vesel, A. Ricard, D. Babič and I. Poberaj, J. Appl. Phys. 97, 103308-1 (2005).

- /49/ N. Krstulovic, I. Labazan, S. Milosevic, U. Cvelbar, A. Vesel and M. Mozetič, J. Phys. D: Appl. Phys. 39, 3799 (2006).

- /50/ M. Mozetič, A. Vesel, U. Cvelbar and A. Ricard, Plasma Chem. Plasma Process 26, 103 (2006).

- /51/ M. Mozetič, A. Ricard, D. Babič, I. Poberaj, J. Levaton, V. Monna and U. Cvelbar, J. Vac. Sci. Technol. A 21, 369 (2003).

- /52/ D. Babič, I. Poberaj and M. Mozetič, Rev. Sci. Instrum. 72, 4110 (2001).

- /53/ Ricard, V. Monna and M. Mozetič, Surf. Coat. Technol. 174-175, 905 (2003).

- /54/ Poberaj, M. Mozetič and D. Babič, J. Vac. Sci. Technol. A 20, 189 (2002).

- /55/ G. Cicconi, J. Phys. D: Appl. Phys. 15, 1403 (1982).

- /56/ C. Hollenstein, J.-L. Dorier, J. Dutta, L. Sansonnens and A.A. Howling, Plasma Sources Sci. Technol. 3, 278 (1994).

- /57/ V.J. Law, A.J. Kenyon, N.F. Thornhill, A.J. Seeds and I. Batty, J. Phys. D: Appl. Phys. 34, 2726 (2001).

- /58/ M. Mozetič, A. Vesel, A. Drenik, I. Poberaj and D. Babič, J. Nucl. Mat. 363-365, 1457 (2007).

- /59/ Vesel, M. Mozetic and M. Balat-Pichelin, Vacuum 81, (2007) 1088.

- /60/ M. Moisan and Z. Zakrzewski, J. Phys. D: Appl. Phys. 24, 1025 (1991).

- /61/ U. Kortshagen, H. Schlüter and A. V. Maximov, Phys. Scr. 46, 450 (1992).

- /62/ Yu. M. Aliev, H Schlüter and A Shivarova, Plasma Sources Sci. Technol. **5**, 514 (1996).

- /63/ E. Castańos-Martinez, Y. Kabouzi, K. Makasheva and M. Moisan, Phys. Rev. E **70**, 066405 (2004).

- /64/ Y. Kabouzi, D. B. Graves, E. Castańos-Martínez and M Moisan, Phys. Rev. E **75**, 016402 (2007).

- /65/ M. Moisan, G. Sauvé, Z. Zakrzewski and J. Hubert, Plasma Sources Sci. Technol. 3, 584 (1994).

- /66/ Jonkers, M. van de Sande, A. Sola, A. Gamero and J. van der Mullen, Plasma Sources Sci. Technol. 12, 30 (2003).

- /67/ Jonkers, M. van de Sande, A. Sola, A. Gamero, A. Rodero and J. van der Mullen, Plasma Sources Sci. Technol. 12, 464 (2003).

- /68/ R. Alvarez, M. C. Quintero and A. Rodero, J. Phys. D: Appl. Phys. 38, 3768 (2005).

- /69/ S. Y. Moon and W. Choe, Spectrochim. Act. B **58**, 249 (2003).

- /70/ C. Tendero, C. Tixier, P. Tristant, J. Desmaison and P. Leprince, Spectrochim. Act. B 61, 2 (2006).

- /71/ R. Stonies, S. Schermer, E. Voges and J. A. C. Broekaert, Plasma Sources Sci. Technol. 13, 604 (2004).

- /72/ I. Al-Shamma'a, S. R. Wylie, J. Lucas and C. F. Pau, J. Phys. D: Appl. Phys. 34, 2734 (2001).

- 73/ R. P. Cardoso, T. Belmonte, G. Henrion and N. Sadeghi, J. Phys.

D: Appl. Phys. 39 4178 (2006).

- /74/ R. P. Cardoso, T. Belmonte, P. Keravec, F. Kosior and G. Henrion, J. Phys. D: Appl. Phys. 40 1394 (2007).

- /75/ A. Skovoroda and A. V. Zvonkov, J. Exp. Theoret. Phys. 92, 78 (2001)

- /76/ H. Potts and J. Hugill, Plasma Sources Sci. Technol. 9, 18 (2000).

- /77/ N. Djermanova, D. Grozev, K. Kirov, K. Makasheva, A. Shivarova and Ts. Tsvetkov, J. Appl. Phys. 86, 738 (1999).

- /78/ Y. Kabouzi and M. Moisan, IEEE Trans. Plasma Sci. 33, 292 (2005).

- /79/ G. M. Petrov and C. M. Ferreira, Phys. Rev. E **59**, 3571 (1999).

- /80/ Yu. B. Golubovskii, H. Lange, V. A. Maiorov, I. A. Porokhova and V. P. Sushkov, J. Phys. D: Appl. Phys. 36, 694 (2003).

- /81/ R. Deloche, P. Monchicourt, M. Cheret and F. Lambert, Phys. Rev. A 13, 1140 (1976).

- /82/ Carata, A. E. Orel and A. Suzor-Weiner, Phys. Rev. A 59, 2804 (1999).

- /83/ P. C. Hill and P. R. Herman, Phys. Rev. A 47, 4837 (1993).

- /84/ R. J. van Sonsbeek, R. Cooper and R. N. Bhave, J. Chem. Phys. 97, 1800 (1992).

- /85/ H. Bohringer, W. Glebe and F. Arnold J. Phys. B: At. Mol. Phys. **16**, 2619 (1983).

- /86/ J. E. Russel, J. Chem. Phys. 84, 4394 (1986).

- /87/ J. S. Cohen, Phys. Rev. A 13, 86 (1976).

- /88/ J. B. Birks, Rep. Prog. Phys. 38, 903 (1975).

- /89/ C. Focsa, P. F. Bernath and R. Colin, J. Molec. Spectr. **191**, 209 (1998).

- /90/ X. Urbain, N. Djuric, C. P. Safvan, M. J. Jensen, H. B. Pedersen, L. Vejby Sogaard and L. H. Andersen, J. Phys. B: At. Mol. Opt. Phys. 38, 43 (2005).

- /91/ Jiang, J. A. Gutherie, R. C. Chaney and A. J. Cunningham, J. Phys. B: At. Mol. Opt. Phys. 22, 3047 (1989).

- /92/ J. Cunningham, T. F. O'Malley and R. M. Hobson, J. Phys. B: At. Mol. Phys. 14, 773 (1981).

T. Belmonte<sup>\*</sup>, R.P. Cardoso, C. Noël, G. Henrion, F. Kosior.

Laboratoire de Science et Génie des Surfaces,

Nancy-Université, CNRS, Parc de Saurupt – CS 14234

– 54042 Nancy Cedex – France

\*Corresponding author.

Fax: +33.3.83.53.47.64

E-mail: Thierry.Belmonte@mines.inpl-nancy.fr

**PACS number**: 34.50-Dy Interactions of atoms, molecules, and their ions with surfaces; photon and electron emission; neutralization of ions.

Prispelo (Arrived): 26.06.2007 Sprejeto (Accepted): 15.09.2007

### INTERACTION OF HIGHLY DISSOCIATED OXYGEN PLASMA WITH POLYMERS AND THEIR COMPOSITES

#### P. Eiselt

#### Plasmabull Engineering GmbH, Lebring, Austria

Key words: Oxygen plasma, Composite, Polymer, Coating, Particle dispersion, Image analysis, Surface characterization

Abstract: Recent application of fully dissociated oxygen plasmas with a low density of charged particles for treatment of polymers and polymer-matrix composite materials is described. Plasma is often created in a high frequency inductively coupled discharge to avoid ion acceleration. At the pressure of few mbar the plasma density is often of the order of 10<sup>16</sup> m<sup>-3</sup>, and the density of neutral oxygen atoms of the order of 10<sup>21</sup> m<sup>-3</sup>. The dissociation fraction of oxygen molecules may approach 100%. Plasma with such characteristics causes modification of solid materials. It is extensively used for surface cleaning and activation, selective etching and sterilization. The first effect of plasma treatment is surface activation. The wettability of materials is increased dramatically enabling their painting, printing and metallization. The treatment time depends on the type of materials and plasma parameters. Optimal wettability is often obtained in less than 1s of plasma treatment thus making the technology suitable for industrial use. Prolonged plasma treatment of polymer matrix composites causes selective etching. Different components are etched at different rates. The highest is the etching rate of the polymer matrix, while inorganic fillings are not etched at all. Oxygen plasma treatment of the composites thus represents a unique method for studying the distribution as well as the orientation of different fillings in composites. The application of this technology is illustrated with several examples.

# Interakcija visoko disociirane kisikove plazme s polimeri in njihovimi kompoziti

Kjučne besede: Kisikova plazma, Kompozit, Polimer, Prevleka, Porazdelitev delcev, Analiza slik, Preiskava površin

**Izvieček:** V prispevku je opisana uporabnost nizkotlačne popolnoma disociirane kisikove plazme za obdelavo polimerov in kompozitnih materialov s polimerno matriko. Takšno plazmo pogosto generiramo v visokofrekvenčni induktivno sklopljeni razelektritvi, s čimer se izognemo pospeševanju ionov v električnem polju. Pri tlaku nekaj mbar je gostota plazme reda velikosti 10<sup>16</sup> m<sup>-3</sup>, gostota nevtralnih kisikovih atomov pa reda 10<sup>21</sup> m<sup>-3</sup>. Stopnja disociiranosti kisikovih molekul se lahko približa 100%. Plazma s tovrstnimi značilnostmi povzroča spremembo trdnih materialov in se široko uporablja za čiščenje, aktivacijo, selektivno jedkanje in sterilizacijo. Prvi pojav, ki ga opazimo pri izpostavi trdnih materialov kisikovi plazmi, je površinska aktivacija. Omočljivost tako obdelanih materialov se dramatično poveča, kar omogoča dober oprijem materiala pri barvanju, tiskanju in metalizaciji. Značilni čas obdelave je odvisen od vrste materiala in plazemskih parametrov. Optimalno omočljivost pogosto dosežemo že v času, manjšem od 1s, kar omogoča industrijsko uporabo. Podaljšana plazemska obdelava kompozitov s polimerno matriko vodi k selektivnemu jedkanju. Različne komponente v kompozitu se jedkajo z različno hitrostjo. Največja je hitrost jedkanja polimerne matrike, medtem ko se anorganska polnila sploh ne jedkajo. Plazemska obdelava kompozitov tako predstavlja edinstveno metodo za preiskavo porazdelitve in celo orientacije polnil v kompozitih. Aplikacija te tehnologije je ilustrirana z različnimi primeri.

#### 1 Introduction

In the past decade, oxygen plasma has been successfully applied to novel technologies such as plasma ashing, plasma cleaning, selective plasma etching and plasma sterilization /1-18/. All the technologies are based on controlled oxidation of organic compounds. In contrary to standard oxidation that is carried on close to the thermodynamic equilibrium, the oxidation in plasma is a well non-equilibrium process. The main advantage of the non-equilibrium oxidation is the capability of controlling the oxidation rate independently from the sample temperature. This is possible due to a low potential barrier for oxidation with reactive particles from oxygen plasma. Oxygen plasma is a source of different reactive particles including excited molecules and atoms, positive and negative molecular and atomic ions, ozone and neutral oxygen atoms. The concentration of these particles depends largely on discharge parameters (i.e. type of discharge, discharge power and frequency, magnetic field, size and shape of discharge vessel, type of material facing plasma, pressure and gas mixture, etc.) Interaction of plasma radicals with solid materials is both

physical and chemical. Physical interaction is usually performed with charged radicals that can be accelerated by biasing samples, while neutral radicals usually do not have substantial kinetic energy so the interaction is purely potential and therefore very selective. Optimal oxidation selectivity is therefore obtained with plasma of low ion density and high neutral radical density.

#### 2 Inductively coupled RF oxygen plasma

Plasma is usually created in a gaseous discharge. Electrons are accelerated in electric field and thermalized at elastic collisions. Their energy distribution function is therefore rather Maxwellian with the temperature of several eV. Electrons in the high-energy tail of the distribution function have enough energy for direct ionisation of gaseous molecules, while those in the low energy part of the distribution function are only capable to excite rotational and vibrational excited states of molecules. In the case of oxygen molecules, the excitation energy for ro-vibrational states is well

below 1 eV, the excitation energy for metastable molecules  $O_2^{1}\Delta$  and  $O_2^{1}\Sigma$  is about 1 and 2 eV, respectively, the dissociation energy is 5.2 eV, while the ionisation energy is 12 eV. Electrons with the average energy of few eV are therefore likely to excite molecules into metastable states and ro-vibrational states, while dissociation and ionisation in less probable.

Excited particles tend to de-excite. There are many channels for de-excitation, some of them occur in the gas phase, while the others take place on the surface of the discharge chamber. In any case, the conservation of energy and momentum as well as rules of quantum mechanics should be obeyed. Vibrationally excited states are de-excited in the gas phase primarily by vibration interchanges (V-V transitions) and super-elastic collisions with atoms (V-T transitions) /8/. Neutral oxygen atoms in the ground state can recombine to molecules only at three-body collisions that are unlikely to occur at low pressure (say below few mbar) so they are rather stable in the gas phase.

Surface de-excitations often play a dominant role in low-pressure plasmas. The probability for ion recombination as well as metastables relaxation is close to unity /19/, while the recombination of neutral oxygen atoms depends largely on the type of material facing plasma as well as its temperature and morphology. The probability for recombination at heterogeneous surface recombination (O + O  $\rightarrow$  O<sub>2</sub>) for many glasses and some ceramics is often low (the typical order of magnitude in 10<sup>-4</sup>), while for many metals and some porous ceramics it is of the order of 10<sup>-1</sup>. The recombination probability does not depend only on the type of material, but also on other parameters.

At low flux of oxygen atoms onto the surface, the recombination probability depends on the surface coverage with O atoms. This phenomenon was often observed at high vacuum, when the flux of O atoms onto the surface is below say  $10^{22}$  m<sup>-2</sup>s<sup>-1</sup>. When the flux is increased, the surface becomes saturated with O atoms and the recombination probability approaches a constant value, that has been known as the recombination coefficient ( $\gamma$ ). The recombination coefficients depend on the material, the surface morphology, and often also on the temperature. There seems to be no general rule, but the recombination coefficient tends to increase with increasing surface roughness as well as increasing surface temperature.

The density of different excited species in plasma depends on excitation and de-excitation probabilities. The excitation probabilities depend mostly on electron density and temperature, while the de-excitation probabilities depend particularly on surface properties. By choosing smooth materials with low recombination coefficients for recombination of O atoms it is often possible to achieve plasma with a low density of ions but a high density of neutral atoms. It is often possible to obtain oxygen plasma with the ion density below  $10^{16} \, \mathrm{m}^{-3}$  and the neutral atom density above  $10^{21} \, \mathrm{m}^{-3}$  /20-23/.

High oxidation selectivity can only be obtained with cold plasmas. Cold plasma is a state of gas with a low kinetic energy of heavy particles, i.e. all particles except electrons. There are some channels for heating heavy particles in plasmas. Happily enough, elastic collisions between fast electrons and heavy particles do not lead to substantial kinetic energy exchange due to a small mass of the electrons. The major channel for heating heavy particles at collisions with energetic electrons is a dissociation event. At direct electron impact dissociation, the excessive kinetic energy of the electron can be observed as the kinetic energy of newly formed atoms, which can move apart with a substantial kinetic energy. Such energetic atoms get effectively thermallized at elastic collisions with other heavy particles. A good way to avoid this sort of plasma heating is application of plasma with a rather low electron temperature.

Another mechanism of heating heavy particles is superelastic collisions between vibrationally excited molecules and oxygen atoms. The reaction cross-section is large / 19/. The only way to avoid such collisions is application of fully dissociated plasma where such collisions are unlikely to occur.

An important channel for heating heavy particles may be acceleration of ions in electric field. The ions are accelerated in electric field as are the electrons. As long as the electric field frequency is low, the ions can follow any change of the local electric field. The energy an oxygen ion can pick from the electric field is

$$W = (e^2 E^2)/(2m\omega^2).$$

(1)

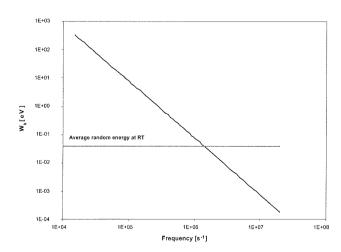

Here, e is the ion charge, E peak electric field, m ion mass and  $\omega$  electric field frequency. The kinetic energy an oxygen ion in a high vacuum can gain in electric field versus the frequency is plotted in Figure 1. As long as the frequency is low (say below 100 kHz), the ions are well accelerated in the field. But as the frequency is increased,

Fig. 1. Maximal kinetic energy of oxygen ions oscillating in a high frequency electric field of 100V/cm.

the ions are not able to follow the field. At the frequency of about few MHz, the kinetic energy an ion can pick from the field is less that average thermal energy of an ion at room temperature. This means that ions in the electric field with a frequency above 10 MHz cannot pick energy worth mentioning. As long as the electric field frequency is higher than 10 MHz, the ions thus cannot be accelerated in the field and cannot contribute to neutral gas heating.

Upper considerations lead to the conclusion that best oxygen plasma for selective oxidation of different materials is created in a radio-frequency discharge. A high degree of dissociation of oxygen molecules is obtained in a discharge chamber made from glass, which has a smooth surface and a low coefficient for recombination of oxygen atoms. There are two extreme modes for RF generator coupling: i) capacitive, and ii) inductive. In practice, the coupling is often a mixture of both extremes. Inductive coupling is often obtained using a coil wounded around a glass tube. In this case, electrons are accelerated in induced electric field sustained due to alternating magnetic field in the coil. The electric field in the axis is rather low, and is increasing towards the edge of the glass tube.

Another extreme is capacitive coupling. In this case, the charged particles are accelerated in the alternating electric field between two parallel electrodes. A sheath with a substantial potential is established next to the powered electrode. As long as the sheath is almost collisionless (i.e. the mean free path is larger than the sheath thickness) the ions entering the sheath from the gas phase are accelerated towards the electrode and do not transfer kinetic energy to other particles. They bombard the electrode and some are reflected as neutral fast atoms or molecules. These fast particles do heat the neutral gas. The heat exchange between positive ions and other heavy particles is increased in the case the sheath is not collisionless. In such cases there are more channels for kinetic energy exchange in the gas phase. This often occurs at elevated pressure, say above 0.1 mbar, where the density of atoms increases with increasing pressure.

As the electric field frequency increases towards the microwave range, the ions can gain practically no energy from the field, and also electrons cannot pick as much energy as in the case of radio-frequency discharges. As a general rule, the electron temperature in simple microwave discharges is always lower than in radio-frequency discharges with comparable power. More energy is transferred to neutral gas heating so the microwave plasmas are never as cold as the RF plasmas.

#### 3 Plasma parameters

Parameters of low pressure plasmas created by inductively coupled RF discharge in a glass tube depend on discharge power and pressure. Typical values are as follows: neutral gas kinetic temperature is often equal to ion kinetic temperature and is a bit more than room temperature - val-

ues between 300 and 500 K are common. The electron temperature is often about 50000 K or more. At the pressure of few 10 Pa, the density of electrons and ions is often between 10<sup>15</sup> and 10<sup>16</sup> m<sup>-3</sup>, the density of neutral oxygen atoms of the order of 10<sup>21</sup> m<sup>-3</sup> while the density of metastable oxygen molecules of the order of 10<sup>19</sup> m<sup>-3</sup>. The plasma potential is often of the order of 10 V and the Deby length about 10<sup>-4</sup> m. The density of neutral oxygen atoms is certainly the most important parameter.

Several methods have appeared to measure the O density in highly dissociated oxygen. The methods include optical spectroscopy /24-27/, mass spectrometry /28-29/, gas titration /22, 30/ and catalytic probes /31-42/. The latter was found to have some advantages over other techniques, as catalytic probes enable real/time measurements and do not disturb the original concentration of O atoms. The disadvantages include a poor understanding of surface recombination phenomena and sensitivity to high-frequency interferences. From the latter point of view, fibre optics catalytic probes (FOCP) have a definite advantage: as any connection is made optical, they are completely immune to stray effects caused by high frequency electromagnetic field /35-38/. On the other hand, the FOCPs cannot measure low densities of O atoms.

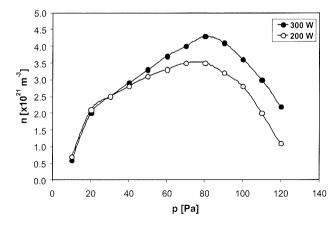

Figure 2 represents measured values of O density in inductively coupled RF plasma created in a discharge tube made from borosilicate glass. Measurements were performed with a FOCP. One can observe that the O density does not depend much on RF power as long as the pressure is low. As the pressure is increased, the O density increases monotonously until it reaches a broad maximum. At high pressure, the O density decreases with increasing power. The appearance of maxima on the curves presented in Figure 2 is explained by different mechanisms of oxygen atom production and loss. At low pressure the O density is limited by surface effects rather than the discharge power. At high pressure the limiting factor is the poor density of electrons as well as their temperature. At even high-

Fig. 2. Density of neutral oxygen atoms in a glass discharge tube with the inner diameter of 3.6mm versus pressure. The parameter is the discharge power.

er pressure the gas-phase atom loss by three-body would become important if the power were further increased. The optimal conditions for a large O density are met at pressure between about 50 and 100 Pa. In this range, the O density depends largely on the discharge power: a higher power causes a higher density. The pressure at which the maximum appears depends on power: at higher power the maximum is shifted to a higher pressure. In any case, the theoretical limit of the O density is full dissociation.

### 4 Interaction of plasma radicals with sample surfaces

The interaction of inductively coupled oxygen plasma with solid materials is almost entirely potential. As shown in upper text, the ion density is usually below 10<sup>16</sup> m<sup>-3</sup> and their kinetic energy at the sample surface about 10 eV. On the other hand we have neutral atoms with the density often exceeding 10<sup>21</sup> m<sup>-3</sup>. The dissociation degree therefore exceeds the ionization fraction by 5 orders of magnitude. A large flux of O atoms onto a sample surface assures rich surface chemistry if the samples are organic materials. The first effect of interaction is surface function-

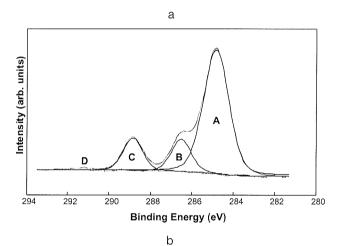

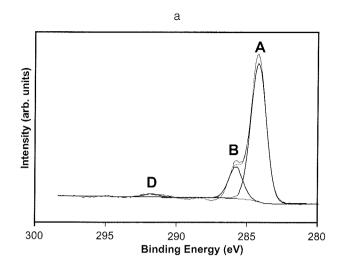

Fig. 3. High resolution XPS C1s peak of polyethyleneterephalate. a) before and b) after plasma treatment for 1s. The O atom density is  $6x10^{21}$  m<sup>-3</sup>. The peak A corresponds to C-C bond, B corresponds to C-O bond, C corresponds to O=C-C bond. D is the  $\pi^*$ - $\pi$ sh up.

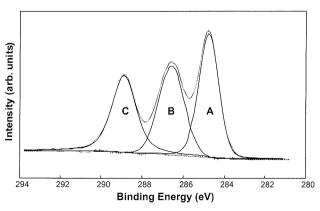

Fig. 4. High resolution XPS C1s peak of polyethersulphone. a) before and b) after plasma treatment for 1s. The O atom density is  $6x10^{21}$  m<sup>-3</sup>.

alization with oxygen-rich functional groups. Next effect is slow etching of the organic material. Since the interaction is almost purely potential, the etching largely depends on the nature and structure of organic materials.

The appearance of the O-rich functional groups is best monitored by X-ray Photoelectron Spectroscopy (XPS) / 43-45/. The resulting surface activation (change of surface energy) is often measured by a contact angle of a water drop, while the distribution of different particles (fillings) in a polymer matrix composite is best monitored by a Scanning Electron Microscopy /46-50/. The appearance of the reaction products is often detected by Optical Emission Spectroscopy (OES) [/51/].

#### 4.1 Surface activation

The first effect of oxygen plasma treatment of organic materials is surface activation. Figure 3 represents the effect of oxygen plasma treatment of polyethyleneterephalate. Figure 3a is the carbon C1s peak obtained by a high-resolution XPS. The carbon is almost entirely bonded to other

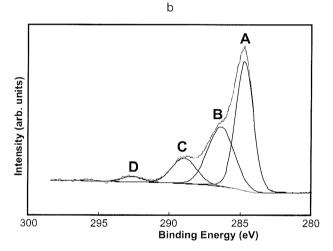

Fig. 5. High resolution XPS analysis of electrolytic graphite. a) O1s peak before and after plasma treatment for 20s, b) C1s peak before and after plasma treatment for 20s.

Binding energy [eV]

carbon atoms and some oxygen is presented in the form of ester group. The sample is exposed to inductively coupled oxygen plasma for 1 second. The carbon peak after this short plasma treatment is shown in Figure 3b. The peak is now enriched with oxygen functional groups. The surface of this material is saturated with functional groups in a second – further treatment does not influence the concentration of the groups on the surface.

Next example of quick plasma activation is presented in Figure 4. In this case, the organic material to be activated is polyethersulphone – a polymer containing sulphur. The C1s peak before plasma treatment is presented in Figure 4a, while after the treatment it is shown in Figure 4b. As in the case of polyethyleneterephalate, the treatment time is only 1 second. The surface is quickly saturated with oxygen rich functional groups such as C-O (peak B in the spectrum) and C=O (peak C). The most energetic peak (D) is a satellite peak  $(\pi \to \pi^*)$ .

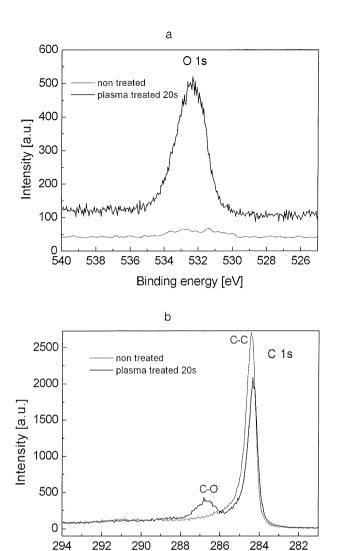

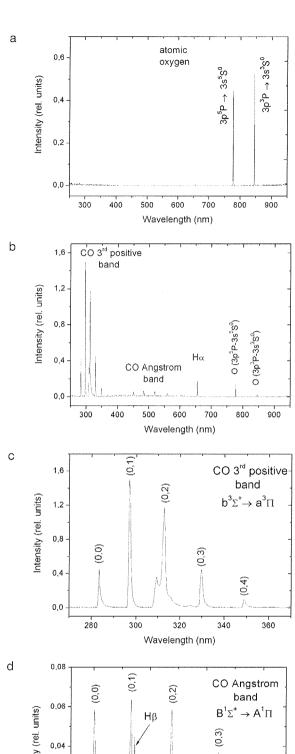

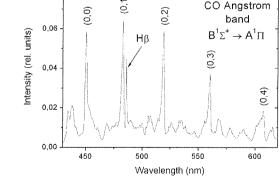

Fig. 6 Optical emission spectroscopy of oxygen plasma. a) before etching of organic material, b) during extensive etching, c) detail spectrum of the CO band corresponding to transitions within the 3<sup>rd</sup> positive system, d) detailed spectrum of the Angstom band.

Apart from organic materials, other forms of carbon are also activated by oxygen plasma treatment, but the required treatment time may be longer. Figure 5 demonstrates activation of pure electrolytic graphite. In this case, the required treatment time is about 20 s. Figure 5a represents the high resolution XPS O1s peak before and after the plasma treatment, while Figure 5b represents the C1s peak. As expected, there is no oxygen bonded to untreated graphite, but the 20 s treatment cause an appearance of oxygen bonded in the form of C – O bond.

#### 4.2 Polymer etching

As the surface is saturated with chemically bonded oxygen, the next step is slow chemical etching of carbon material. The etching rate depends on the type of material, its temperature, and the flux of oxygen atoms on the surface of the sample. The evidence of etching can be obtained by Optical Emission Spectroscopy. A simple optical spectrometer is good enough to monitor the appearance of the oxidation products. Figure 6a is a typical OES spectrum

29kU X500 50мm 17:40 BET.

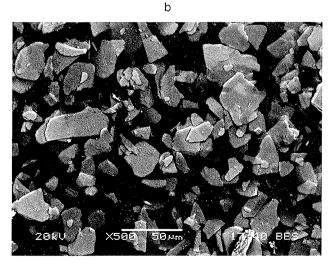

Fig. 7. SEM image of a metal paint with a pearl effect. a) untreated sample, b) sample treated in oxygen plasma for 40s. The O atom density is  $8 \times 10^{21}$  m<sup>-3</sup>.

а

soku Xuanaba Tun in sa bes

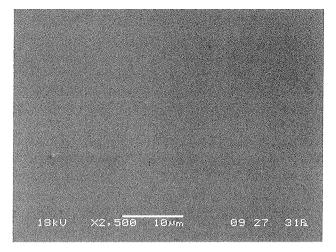

Fig. 8. SEM image of a powder coating. a) untreated sample, b) sample treated in oxygen plasma for 300s. The O atom density is  $6x10^{20}$  m<sup>-3</sup>.

from oxygen plasma before etching of organic materials. The only features worth mentioning are the oxygen atoms peaks at 777 nm and 845 nm. Other peaks are so small that cannot be visible in Figure 6a. As etching of organic materials starts, the OES spectrum becomes richer as shown in Figure 6b. The peaks that correspond to CO bands appear. Figure 6c is a detail of the CO band corresponding to the transition in the 3<sup>rd</sup> positive system, while Figure 6d represents the emission due to CO transitions in the Angstrom band. Optical emission spectroscopy therefore represents a powerful tool for detection etching of carbon-containing compounds. Since CO is normally not presented in oxygen plasma in reasonable concentration, the appearance of the CO bands indicate etching of carbon containing materials.

#### 4.3 Selective etching of composites

Composite materials with a polymer matrix are nowadays widely used as bulk materials and films. They combine the properties of polymers (easy instillation, low price) and the

д 2 до до до година и постава и пос

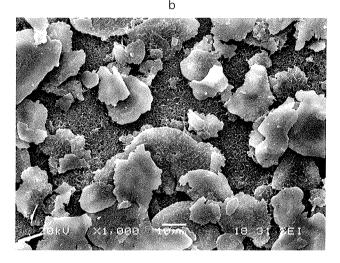

Fig. 9. SEM image of similar samples produced by two different producers. The plasma parameters were as follows: treatment time 120s, O atom density 2x10<sup>21</sup> m<sup>-3</sup>.

fillers (good mechanical, electrical and optical properties). Many materials referred as plastics are actually composites. The most usual fillers are pigments – they are used to give the material its colour. Different fibres are used to increase the material strength and toughness. Graphite is

often used to increase electrical conductivity, while different coatings and paints are actually composites with a variety of fillers. A typical paint for metal, for instance is a composite of et least 5 different fillers distributed in the polymer matrix. The characteristics of the composites depend on the type of polymer, the type and concentration of the fillers, and the production procedure. They often depend also on distribution and in some cases even orientation of the fillers in the polymer matrix. The term "pigment dispersion" in paint coatings describes the relative amount of pigment aggregates and agglomerates in solid media. It affects gloss and haze of the final coating and may also change viscosity of the coating. Dispersion of pigments is influenced by the properties of coating components and by the production process.

It is difficult to detect the exact distribution of fillers in the polymer matrix. Namely, the uppermost material is polymer that hides the fillers. The best way of making fillers visible is a gentle removal of the polymer. The treatment should leave the fillers intact and should be performed at low temperature to avoid any deformation of the polymer matrix. The best way of doing so is to perform low temperature etching by inductively coupled oxygen plasma. As mentioned before, the interaction of such oxygen plasma with the solid material is almost entirely potential: oxygen atoms react with polymer matrix while leaving the fillers fairly intact. The first example of such treatment is a coating with mica flakes. Figure 7a is the SEM image of the untreated sample, while Figure 7b represents the image of the same sample exposed to oxygen plasma for 30 s. Comparison of Figures 7a and 7b clearly shows a high etching selectivity obtained by inductively coupled oxygen plasma: the polymer is effectively etched, while the mica flakes are left intact.

Mild oxygen plasma treatment is even selective enough to have different etching rates for two different organic materials. Figure 8 represents results of the etching of paint for metal. Figure 8a is the SEM image of untreated sample, while Figure 8b represents the same paint after plasma treatment. While the original surface is perfectly flat (covered by the polymer), the surface of plasma treated sample is covered with small perfectly spherical features. These spheres are actually organic pigments. The structure of

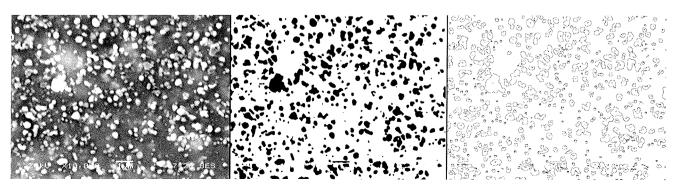

Fig. 10. SEM image of a sample before and after the image modification and outlined particles detected with appropriate program.

the organic pigments is different from the polymer matrix. The oxygen plasma is obviously gentle enough to distinguish between the polymer and the organic pigment. While polymer is etched at a high rate, the pigments are practically not etched at all, as observed by comparison of Figure 8 a and b.

The oxygen plasma treatment is used for study of fillers type, size and distribution in composites in order to detect small variations of similar products produced by different procedures. Figure 9 represents SEM images of similar products by two different producers. The similarity of the products is so high that classical testing of the two materials does not show any appreciable difference between them. The oxygen plasma etching, however, reveals small but important differences between the products in Figure 9 a and b. The product presented in Figure 9a is rich in small particles with the dimension of about 1em, while these particles are absent in the product shown in Figure 9b. Plasma etching of such products actually enables the reverse engineering. If the type and concentration of fillers in a product are unknown, one can learn about them by etching the material with oxygen plasma and image the surface by a SEM.

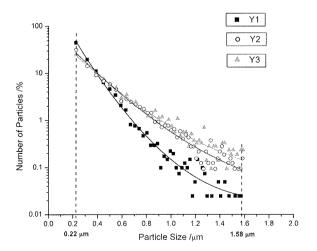

Advanced software allows for quantification of the filler distribution in the polymer matrix composites. Figure 10 shows the appropriated steps done to study the size distribution of filler grains. The left figure is the SEM image of the plasma etched material. The middle figure is the negative contrast black/white micrograph. The right figure 3 shows the results of particle detection using the appropriate software program. The results of the image analysis of these three micrographs are presented in the Figure 11, where the size distribution of pigment particles is shown. Large particles, of diameter greater than 2 mm, were excluded from the calculation because of their small population in the micrographs. The results in Figure 11 are shown for three mate-

Fig. 11. Particle diameter distribution in samples produced by three different procedures marked as Y1, Y2 and Y3.

rials with same ingredients but different production procedure.

#### 5 Conclusions

Highly reactive oxygen plasma is obtained in inductively coupled RF discharges. The degree of ionization is often of the order of 10<sup>-6</sup> while the dissociation fraction easily exceeds 10%. The neutral gas temperature is kept close to room temperature since there is practically no mechanism heating the neutral gas. The high dissociation rate, low kinetic temperature, low ion density and low plasma potential allow for practically pure potential interaction of plasma radicals with solid materials exposed to plasma. The etching of samples is extremely selective: while organic materials are etched, the inorganic materials are not etched at all. The etching rate depends on the type of organic materials. Simple polymers are etched at relatively high rate while graphite is practically not etched at all. Even different types of organic materials are etched at different rates. While epoxy resign is etched at a relatively high rate, the organic pigments are virtually untouched. This extremely high etching selectivity allows for development a method for determination of the distribution and orientation of fillers in polymer matrix composites. Several examples of the practical application of this technology are presented. The choice of plasma parameters depend on characteristics of particular samples. High etching rate is obtained using plasma with a high atom density, but extremely high etching selectivity is obtained using plasma with a moderate O density.

#### References

- /1/ M. R. Wertheimer, L. Martinu, E. M. Liston, Plasma sources for polymer surface treatment, Handbook of thin film Process Technology, ed. by D.A.Glocker and S.I. Shah. Bristol, Inst. of Physics Publishing, Bristol, 1998.

- /2/ K. G. Pruden, G. B. Raupp, S. P. Beaudoin, J. Vac. Sci. Technol. B, vol. 21, pp. 1496, 2003.

- /3/ J. S. Kim, F. Cacialli, R. Friend, Thin Solid Films, vol. 445, pp. 358, 2003.

- /4/ S. Gomez, P. G. Steen, W. G. Graham, Appl. Phys. Lett., vol. 81, pp. 19, 2002.

- /5/ H. Singh, J. W. Coburn, D. B. Graves, J. Appl. Phys., vol. 88, pp. 3748, 2000.

- /6/ D. J. Wilson, N. P. Rhodes, R. L. Williams, Biomaterials, vol. 24, pp. 5069, 2003

- /7/ Z. Y. Wu, N. Xanthopoulos, F. Reymond, J. S. Rossier, H. H. Girault, Electrophoresis, vol. 23, pp. 782, 2002.

- /8/ M. Mozetic, A. Zalar, Mater. Sci. Forum, vol. 437, pp. 81, 2003.

- /9/ A. G. Whittaker, E. M. Graham, R. L. Baxter, A. C. Jones, P. R. Richardson, G. Meek, G. A. Campbell, A. Aitken, H. C. Baxter, J. Hosp. Infect., vol. 56, pp. 37, 2004.

- /10/ K. Gorna, S. Gogolewski, Polym. Degrad. Stabil., vol. 79, pp. 475, 2003.

- /11/ M. Nagatsu, F. Terashita, Y. Koide, Jap. J. Appl. Phys, vol. 42, pp. L856, 2003.

- /12/ M. K. Gunde, M. Kunaver, Appl. Spect., vol. 57, pp. 1266, 2003.

- /13/ M. Kunaver, M. K. Gunde, M. Mozetic, M. Kunaver, A. Hrovat, Surf. Coat. Int. B, vol. 86, pp. 175, 2003.

- /14/ M. Mozetic, U. Cvelbar, M. K. Sunkara, S. Vaddiraju, Adv. Mater., vol. 17, pp. 2138, 2005.

- /15/ A. Vesel, M. Mozetic, A. Drenik, S. Milosevic, N. Krstulovic, M. Balat-Pichelin, I. Poberaj, D. Babic, Plasma Chem. Plasma Proc., vol. 26, pp. 577, 2006.

- /16/ A. Vesel, M. Mozetic, A. Zalar, Appl. Surf. Sci., vol. 200, pp.94, 2002.

- /17/ M. Mozetic, Vacuum, vol. 71, pp. 237, 2003.

- /18/ U. Cvelbar, D. Vujosevic, Z. Vratnica, M. Mozetic. J. Phys. D Appl. Phys., vol. 39, pp. 3487, 2006.

- /19/ A. Ricard, Reactive plasmas, SFV, 1996.

- /20/ A. Ricard, V. Monna, Plasma Sourc. Sci. Technol., vol. 11, pp. A150, 2002.

- /21/ A. Vesel, M. Mozetic, Vacuum, vol. 61, pp. 373, 2001.

- /22/ S. Villeger, S. Cousty, A. Ricard, M. Sixou, J. Phys. D Appl. Phys., vol. 36, pp. L60, 2003.

- /23/ A. Drenik, U. Cvelbar, A. Vesel, M. Mozetic, Inf. MIDEM, vol. 35, pp. 85, 2005.

- /24/ J. J. Robbins, R. T. Alexander, W. Xiao, T. L. Vincent, C. A. Wolden, Thin Solid Films, vol. 406, pp. 145, 2002.

- /25/ M. C. Kim, S. H. Yang, J. H. Boo, J. G. Han, Surf. Coat. Technol., vol. 174, pp. 839, 2003.

- /26/ A. Granier, M. Vervloet, K. Aumaille, C. Vallee, Plasma Sourc. Sci. Technol., vol. 12, pp. 89, 2003.

- /27/ H. Biederman, V. Stelmashuk, I. Kholodkov, A. Choukourov, D. Slavinska, Surf. Coat. Technol., vol. 174, pp. 27, 2003.

- /28/ G. F. Leu, A. Brockhaus, J. Engemann, Surf. Coat. Technol., vol. 174, pp. 928, 2003.

- /29/ Y. C. Hong, H. S. Uhm, Phys. Plasmas, vol. 10, pp. 3410, 2003.

- /30/ G. B. I. Scott, D. A. Fairley, D. B. Milligan, C. G. Freeman, M. J. McEwan, J. Phys. Chem. A, vol. 103, pp. 7470, 1999.

- /31/ L. Elias, E. A. Ogrizlo, H. I. Schiff, Can. J. Chem., vol. 37, pp. 1680, 1959.

- /32/ M. R. Carruth, R. F. DeHaye, J. K. Norwood, A. F. Whitaker, Rev. Sci. Instr., vol. 61, pp. 1211, 1990.

- /33/ I. Sorli, R. J. Rocak, Vac. Sci. Technol. A, vol. 18, pp. 338, 2000.

- /34/ M. Mozetic, A. Vesel, M. Gaillard, A. Ricard, Plasmas Polym., vol. 6, pp. 41, 2001.

- /35/ D. Babič, I. Poberaj, M. Mozetič, Rev. Sci. Instr., vol. 72, pp. 4110, 2001.

- /36/ I. Poberaj, D. Babič, M. Mozetič, J. Vac. Sci. Technol. A, vol. 20, pp. 189, 2002.

- /37/ M. Mozetic, A. Ricard, D. Babic, I. Poberaj, J. Levaton, V. Monna, U. Cvelbar, J. Vac. Sci. Technol. A, vol. 21, pp. 369, 2003.

- /38/ M. Balat-Pichelin, A. Vesel, Chem. Phys., vol. 327, pp. 112, 2006.

- /39/ A. Vesel, M. Mozetic, M. Balat-Pichelin, Vacuum, in press, (doi:10.1016/j.vacuum.2007.02.003), 2007.

- /40/ M. Mozetic, A. Vesel, U. Cvelbar, A. Ricard, Plasma Chem. Plasma Process., vol. 26, pp. 103, 2006.

- /41/ M. Mozetic, A. Vesel, V. Monna, A. Ricard, Vacuum, vol. 71, pp. 201, 2003.

- /42/ M. Mozetic, U. Cvelbar, A. Vesel, A. Ricard, D. Babic, I. Poberaj. J. Appl. Physic., vol. 97, pp. 103308-1, 2005.

- /43/ T. Vrlinic, A. Vesel, U. Cvelbar, M. Krajnc, M. Mozetic, Surf. Interface Anal., in press, (DOI: 10.1002/sia.2548), 2007.

- /44/ A. Vesel, M. Mozetic, A. Zalar, Vacuum, in press, 2007.

- /45/ A. Vesel, M. Mozetic, J. Kovac, A. Zalar, Appl. Surf. Sci., vol. 253, pp. 2941, 2006.

- /46/ M. Mozetic, A. Zalar, P. Panjan, M. Bele, S. Pejovnik, R. Grmek, Thin solid films, vol. 376, pp. 5, 2000.

- /47/ M.K. Gunde, M. Kunaver, M. Mozetic, P. Pelicon, J. Simcic, M. Budnar, M. Bele, Surf. Coat. Int., Part B, Coat. Trans., vol. 85, pp. 115, 2002.

- /48/ M. Kunaver, M. K. Gunde, M. Mozetic, A. Hrovat, Dyes Pigm., vol. 57, pp. 235, 2003.

- /49/ M. K. Gunde, M. Kunaver, M. Mozetic, A. Hrovat, Powder Technol., vol. 148, pp. 64, 2004.

- /50/ M. Kunaver, M. Mozetic, M. K. Gunde, Thin solid films, vol. 459, pp. 115, 2004.

- /51/ N. Krstulovic, I. Labazan, S. Milosevic, U. Cvelbar, A. Vesel, M. Mozetic, J. Phys. D Appl. Phys., vol. 39, pp. 3799, 2006.

P. Eiselt Plasmabull Engineering GmbH, Parkring 6, A – 8403 Lebring, Austria

Prispelo (Arrived): 07.05.2007 Sprejeto (Accepted): 15.09.2007

## GRAPHICAL FRAMEWORK FOR SYSTEM LEVEL DESIGN SPACE EXPLORATION

Klemen Perko<sup>1</sup>, Andrej Trost<sup>2</sup>

<sup>1</sup>Sipronika d.o.o., Ljubljana, Slovenia <sup>2</sup>Faculty of Electrical Engineering, Laboratory for Integrated Circuits Design, University of Ljubljana, Ljubljana, Slovenia

Key words: abstraction, design-space exploration, graphical modeling, high-level design, system-level simulation.

Abstract: As technology advances, options for realization of heterogeneous systems increase. Designers use a variety of hardware (HW) and software (SW) co-design methodologies in order to meet application constraints as fast as possible. The paper presents a graphical modeling framework used for high-level modeling and design-space exploration of heterogeneous systems. The framework provides designer graphical elements for using modeling concepts from system modeling libraries. Graphical modeling relieves the designer of the manual-typing source code and thus hides many details of system-level design languages that normally need to be taken care of. The graphical framework also provides different constraint checks during modeling and automatically generates an executable model for evaluation of a heterogeneous system. Our case study exemplifies the use of the framework and shows what information is obtained from an executable model built on a high-level of abstraction. Evaluation of results serves as a basis for further design decisions. Graphical modeling enables rapid changes in the model and thus speeds-up design-space exploration.

# Grafično okolje za raziskovanje načrtovalskega prostora na nivoju sistemov

Kjučne besede: abstrakcija, modeliranje, raziskovanje načrtovalskega prostora, visokonivojsko načrtovanje.

Izvleček: S tehnološkim napredkom se povečuje nabor možnih realizacij heterogenih sistemov. Načrtovalci za čimprejšnje izpolnjevanje načrtovalskih zahtev uporabljajo širok spekter metodologij za sočasno načrtovanje strojne in programske opreme. Članek predstavlja grafično modelirno okolje za modeliranje in raziskovanje načrtovalskega prostora heterogenih sistemov. To okolje omogoča načrtovalcu uporabo grafičnih elementov pri modeliranju konceptov iz knjižnic za modeliranje na sistemskem nivoju. Grafično okolje načrtovalca razbremenjuje ročnega pisanja programske kode, tako da mu ni več potrebno poznati točne sintakse ukazov programskih jezikov za modeliranje na sistemskem nivoju. Okolje med izdelavo modela preverja njegovo skladnost z različnimi omejitvami. Po končanem modeliranju heterogenega sistema, za njegovo ovrednotenje okolje avtomatsko ustvari izvršljiv model. Uporaba okolja je prikazana na praktičnem primeru. Prikazano je, katere informacije dobimo iz izvršljivega modela zgrajenega na visokem nivoju abstrakcije. Ovrednoteni rezultati predstavljajo podlago nadaljnjim načrtovalskim odločitvam. Grafično modelirno okolje omogoča hitre spremembe modela in tako pospeši raziskovanje načrtovalskega prostora.

#### 1 Introduction

Advances in technology provide various options for realization of embedded systems. Designers are encouraged to use a variety of HW and SW implementation technologies in order to meet application constraints and provide quick time-to-market solutions. The increasing complexity of modern embedded systems requires new design methodologies and system-level design tools /1/.

Many research studies are concentrated on the issues of HW/SW co-design, co-simulation and various optimization techniques. The research activity is slowly drifting away from modeling heterogeneous aspects of the system towards system description on a higher abstraction level /2/.

This paper will present a design framework for system-level design space exploration. The presented framework is used for a quick evaluation of design decisions in the first stages of the design process. The evaluation is based on the results obtained from a high-level model of the system composed in a graphical framework.

#### 2 Design space exploration

HW and SW components of digital systems are designed by using specialized languages. The HW description language VHDL /3/ or Verilog is used for design and implementation of HW components and the C or C++ is used for SW description. These languages are mature and provide automatic implementation and various optimization possibilities.

On the system level, we need tools and languages for modeling systems composed of HW and SW components. The result of research in this area is several system level design languages (SLDL) and HW/SW co-design methodologies /4/.

A typical design flow starts with a high-level system model containing architecture description, functionality description and mapping information /5/. During design-space exploration, the model is repeatedly evaluated and changed until the application constraints are met. If the design methodology supports different levels of abstraction, we have

to repeat design-space exploration on each level. In each level we add new information thus lowering the level of abstraction. Finally, a description of HW and SW components prepared for automatic implementation tools is obtained.

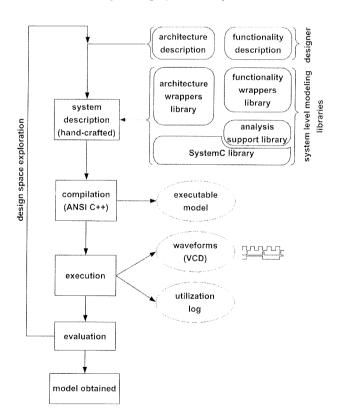

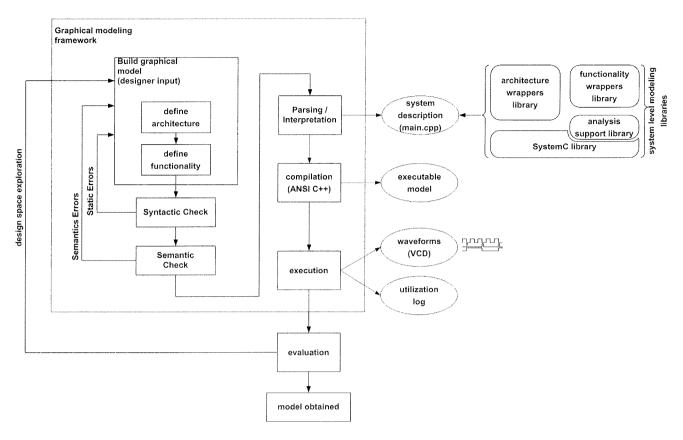

#### 2.1 SystemC Design Flow

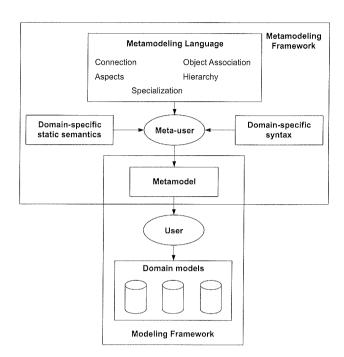

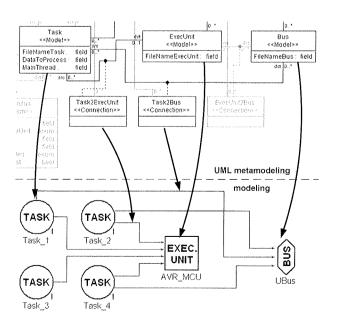

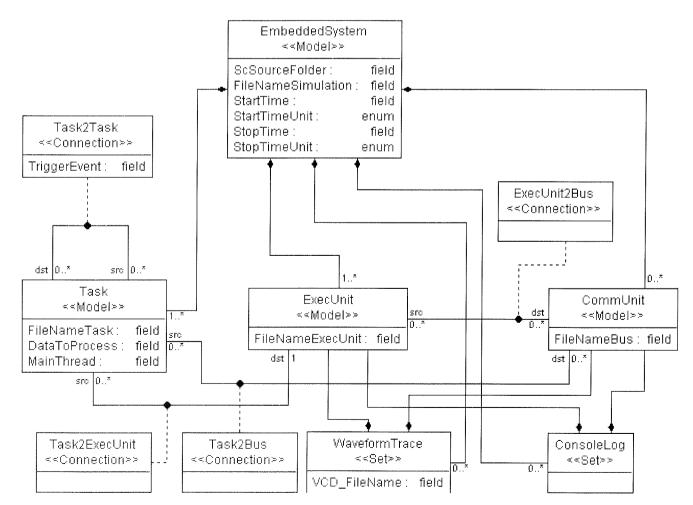

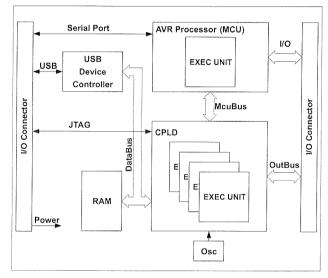

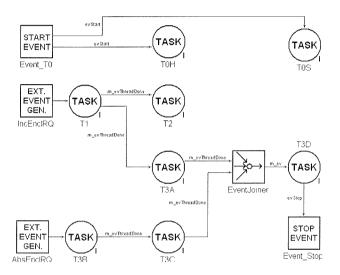

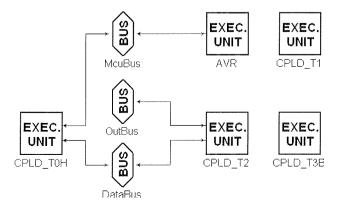

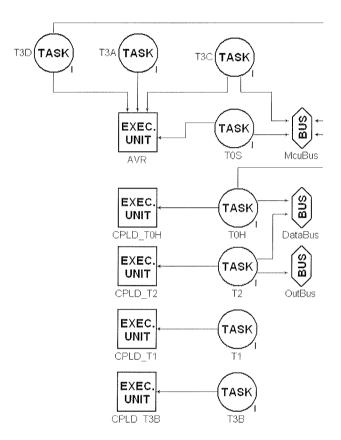

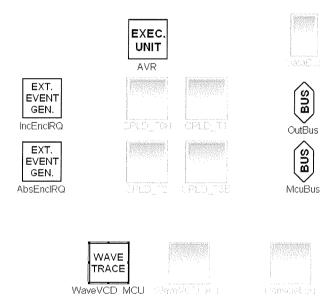

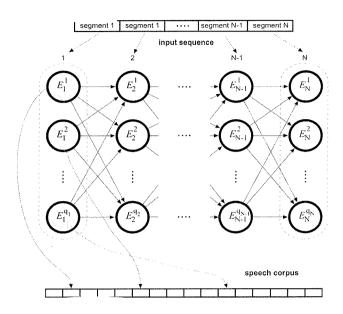

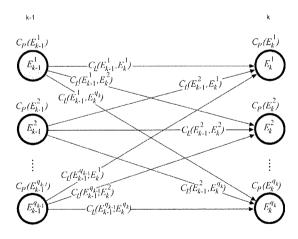

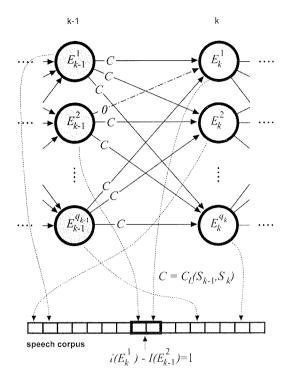

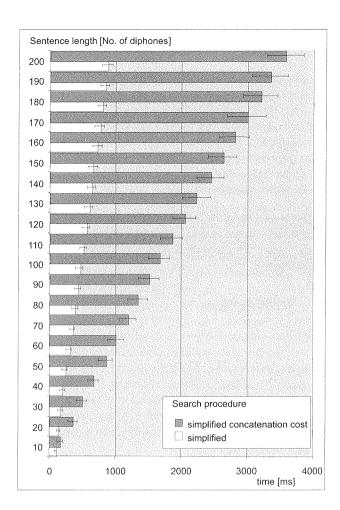

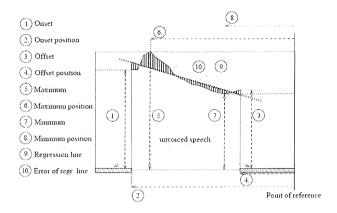

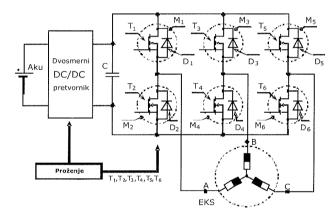

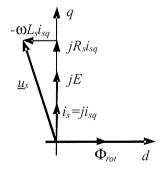

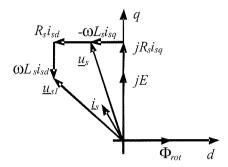

The SystemC is a system-level description language based on the C++ language. The programming language C++ can be used also as an extensible object-oriented modeling language. The SystemC extends the capabilities of the C++ by enabling modeling of hardware descriptions /6/, /7/.