# INFORMACIJE

Strokovno društvo za mikroelektroniko elektronske sestavne dele in materiale

# 4 • 1993

Časopis za mikroelektroniko, elektronske sestavne dele in materiale Časopis za mikroelektroniku, elektronske sastavne dijelove i materijale Journal of Microelectronics, Electronic Components and Materials

INFORMACIJE MIDEM, LETNIK 23, ŠT. 4(68), LJUBLJANA, DECEMBER 1993

### INFORMACIJE

# **MIDEM**

**4** ° 1993

| INFORMACIJE MIDEM | LETNIK 23, ŠT. 4(67), LJUBLJANA, | DECEMBER 1993 |

|-------------------|----------------------------------|---------------|

| INFORMACIJE MIDEM | GODINA 23, BR. 4(67), LJUBLJANA, | DECEMBAR 1993 |

| INFORMACIJE MIDEM | VOLUME 23, NO. 4(67), LJUBLJANA, | DECEMBER 1993 |

Izdaja trimesečno (marec, junij, september, december) Strokovno društvo za mikroelektroniko, elektronske sestavne dele in materiale. Izdaja tromjesečno (mart, jun, septembar, decembar) Stručno društvo za mikroelektroniku, elektronske sastavne dijelove i materiale. Published quarterly (march, june, september, december) by Society for Microelectronics, Electronic Components and Materials - MIDEM.

Glavni in odgovorni urednik Glavni i odgovorni urednik **Editor in Chief**

Iztok Šorli, dipl.ing., MIKROIKS d.o.o., Ljubljana

Tehnični urednik Tehnički urednik **Executive Editor**

Janko Colnar, MIDEM, Ljubljana

Uredniški odbor Redakcioni odbor **Editorial Board**

Doc. dr. Rudi Babič, dipl.ing., Tehniška fakulteta Maribor Dr.Rudi Ročak, dipl.ing., MIKROIKS d.o.o., Ljubljana mag.Milan Slokan, dipl.ing., MIDEM, Ljubljana Zlatko Bele, dipl.ing., MIKROIKS d.o.o., Ljubljana Miroslav Turina, dipl.ing., Zagreb mag. Meta Limpel, dipl.ing., MIDEM, Ljubljana Miloš Kogovšek, dipl.ing., Iskra INDOK d.o.o., Ljubljana

Časopisni svet Izdavački savet **Publishing Council**  Prof. dr. Slavko Amon, dipl.ing., Fakulteta za elektrotehniko in računalništvo, Ljubljana, PREDSEDNIK

Dr. Jean-Marie Haussonne, C.N.E.T. Centre LAB, Lannion

Dr. Marko Hrovat, dipl.ing., Inštitut Jožef Stefan, Ljubljana Prof. dr. Zvonko Fazarinc, dipl.ing., CIS, Stanford University, Stanford, USA

Dr. Marija Kosec, dipl.ing., Inštitut Jožef Stefan, Ljubljana Prof.dr.Drago Kolar, dipl.ing., Inštitut Jožef Stefan, Ljubljana RNDr. DrSc. Radomir Kužel, Charles University, Prague

Dr. Giorgio Randone, ITALEL S.I.T. spa, Milano

Prof.dr. Štane Pejovnik, dipl.ing., Kemijski inštitut Boris Kidrič, Ljubljana

Dr. Giovanni Soncini, University of Trento, Trento

Prof.dr. Janez Trontelj, dipl.ing., Fakulteta za elektrotehniko in računalništvo,

Ljubljana

Dr. Anton Zalar, dipl.ing., IEVT, Ljubljana

Dr. Peter Weissglas, Swedish Institute of Microelectronics, Stockholm

Naslov uredništva Adresa redakcije Headquarters

Uredništvo Informacije MIDEM Elektrotehniška zveza Slovenije Dunajska 10, 61000 Ljubljana, Slovenija (0)61 - 316 886

Letna naročnina znaša 7000,00 SIT, cena posamezne številke je 1750,00 SIT. Člani in sponzorji MIDEM prejemajo Informacije MIDEM brezplačno. Godišnja pretplata iznosi 7000,00 SIT, cijena pojedinog broja je 1750,00 SIT. Članovi i sponzori MIDEM primaju Informacije MIDEM besplatno. Annual subscription rate is DEM 100, separate issue is DEM 25. MIDEM members and Society sponsors receive Informacije MIDEM for free.

Znanstveni svet za tehnične vede I je podal pozitivno mnenje o časopisu kot znanstveno strokovni reviji za mikroelektroniko, elektronske sestavne dele in materiale. Izdajo

revije sofinanci rajo Ministrstvo za znanost in tehnologijo in sponzorji društva. Scientific Council for Technical Sciences of Slovene Ministry of Science and Technology has recognized Informacije MIDEM as scientific Journal for microelectronics,

electronic components and materials. Publishing of the Journal is financed by Slovene Ministry of Science and Technology and by Society sponsors.

Znanstveno strokovne prispevke objavljene v Informacijah MIDEM zajemamo v:

\* domačo bazo podatkov ISKRA SAIDĆ-el, kakor tudi

\* v tujo bazo podatkov INSPEC

Scientific and professional papers published in Informacije MIDEM are assessed into: \*domestic data base ISKRA SAIDC-el and

\* foreign data base INSPEC

Po mnenju Ministrstva za informiranje št.23/300-92 šteje glasilo Informacije MIDEM med proizvode informativnega značaja, za katere se plačuje davek od prometa proizvodov po stopnji 5 %.

Grafična priprava in tisk Grafička priprema i štampa Printed by Naklada Tiraž

Circulation

BIRO M, Ljubljana

1000 izvodov 1000 primjeraka 1000 issues

| l.Šorii:                                                                                                                                                                               | 244 | I. Šorli:                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Društvo MIDEM in njegove dejavnosti ZNANSTVENO STROKOVNI PRISPEVKI                                                                                                                     |     | MIDEM Society and its Activities PROFESSIONAL SCIENTIFIC PAPERS                                                                                                                |

|                                                                                                                                                                                        |     |                                                                                                                                                                                |

| MIEL-SD 93 VABLJENA PREDAVANJA                                                                                                                                                         |     | MIEL-SD 93 INVITED PAPERS                                                                                                                                                      |

| M.B. Johnson, H.W.M. Salemink:<br>Rasterska tunelska mikroskopija presekov heteroslojnih polprevodnikov:<br>Atomska ločljivost, sestava, fluktuacije in dopiranje                      | 245 | M.B.Johnson, H.W.M.Salemink:<br>Cross-Sectional Scanning Tunneling Microscopy on Heterostructures:<br>Atomic Resolution, Composition, Fluctuations and Doping                  |

| C,Cini:<br>Mešana bipolarna - CMOS - DMOS tehnologija za pametna močnostna<br>integrirana vezja                                                                                        | 253 | C.Cini:<br>Mixed Bipolar-CMOS-DMOS Smart Power IC Technology                                                                                                                   |

| J.Furlan, W.Kusian, G.Conte:<br>Tandemske amorfne silicijeve sončne celice                                                                                                             | 259 | J.Furlan, W.Kusian, G.Conte:<br>Tandem Amorphous Silicon Solar Cells                                                                                                           |

| A.J.Williams, I.R.Harris:<br>Magneti kovin prehoda in redkih zemelj: proizvodnja, lastnosti in uporaba                                                                                 | 264 | A.J.Williams, I.R.Harris:<br>Rare Earth-Transition Metal Magnets: Their Processing, Properties and<br>Applications                                                             |

| J.W.Ciognani, E.Gramegna, M.Wiegand:<br>Pregled trenutnega stanja razvoja keramične in poliimidne tehnologije za<br>multičip module                                                    | 272 | J.W.Ciognani, E.Gramegna, M.Wiegand:<br>An Overview of Recent Developments in Ceramic and Polyimide<br>Technologies for Multichip Modules                                      |

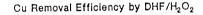

| M.Maček:<br>Pregled sodobníh postopkov mokrega čiščenja silicijevíh rezin                                                                                                              | 275 | M.Maček:<br>A Review of Advanced Wet Cleaning                                                                                                                                  |

| Pregled sodomin postopkov mokrega ciscenja silicijevin rezin  UPORABA POLPREVODNIŠKIH IN MIKROELEKTRONSKIH KOMPONENT                                                                   |     | A REVIEW OF ADVANCED WELL CHARMING APPLICATION OF SEMICONDUCTOR AND MICROELECTRONIC COMPONENTS                                                                                 |

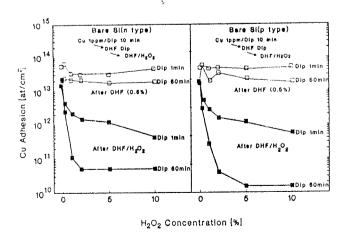

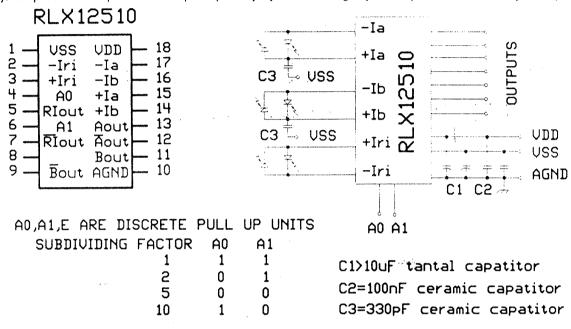

| J.Novek:<br>Mikroelektronika v službi natančnega merjenja pomikov in zasukov.<br>Integrirano vezje RLX 12510                                                                           | 284 | J.Novak:<br>Use of Microlectronic Technology for Exact Position and Shaft<br>Measurements. RLX 12510 Integrated Circuit                                                        |

| KONFERENCE, POSVETOVANJA, SEMINARJI, POROČILA                                                                                                                                          |     | CONFERENCES, COLLOQUYUMS, SEMINARS, REPORTS                                                                                                                                    |

| M.Slokan, I.Šorli:<br>21.Mednarodna konferenca o mikroelektroniki, MIEL'93 in 29.Simpozij o<br>elektronskih sestavnih delih in materialih, SD'93, 29.09 01.10.1993, Bled,<br>Slovenija | 285 | M.Slokan, I.Šorii:<br>21st International Conference on Microelectronics, MIEL'93 and 29th<br>Symposium on Devices and Materials, SD'93, 29.09. • 01.10.1993, Bled,<br>Slovenia |

| ESSDERC 93                                                                                                                                                                             | 288 | ESSDERC 93                                                                                                                                                                     |

| D.Križaj:<br>EPE - 5.evropska konferenca o močnostni elektroniki in njeni uporabi                                                                                                      | 289 | D.Križaj:<br>EPE - 5.th European Conference on Power Electronics and Applications                                                                                              |

| A.Zalar:<br>ECASIA 93 • 5.evropska konferenca o uporabi metod za analizo površin in<br>faznih meja                                                                                     | 290 | A.Zalar:<br>ECASIA 93 - 5.th European Conference on Application for Surface and<br>Interface Analysis                                                                          |

| A.Cvelbær:<br>ICTF 9 • 9.mednarodna konferenca o tankih plasteh                                                                                                                        | 292 | A.Cvelbar:<br>ICTF 9 - 9th International Conference on Thin Films                                                                                                              |

| A.Pregelj:<br>44.posvetovanje o metalurgiji in kovinskih gradivih ter 1. posvetovanje o<br>materialih                                                                                  | 293 | A.Pregelj:<br>44th Symposium on Metallurgy and Metal Compounds and 1st Symposium<br>on Materials                                                                               |

| PREDSTAVLJAMO PODJETJE Z NASLOVNICE                                                                                                                                                    |     | REPRESENT OF COMPANY FROM FRONT PAGE                                                                                                                                           |

| CMP servis                                                                                                                                                                             | 294 | CMP Service                                                                                                                                                                    |

| VESTI                                                                                                                                                                                  | 301 | NEWS                                                                                                                                                                           |

| KOLEDAR PRIREDITEV                                                                                                                                                                     | 309 | CALENDAR OF EVENTS                                                                                                                                                             |

| TERMINOLOŠKI STANDARDI                                                                                                                                                                 | 310 | TERMINOLOGICAL STANDARDS                                                                                                                                                       |

| MIDEM prijavnica                                                                                                                                                                       | 315 | MIDEM Registration Form                                                                                                                                                        |

| VSEBINA LETNIKA 1993                                                                                                                                                                   | 318 | CONTENT - VOLUME 1993                                                                                                                                                          |

| Slika na naslovnici:<br>CMP • Multičip servis; GaAs rezina z digitalnimi integriranimi vezji z<br>minimalno razsežnostjo 0.8 µm izdelano v firmi TCS                                   |     | Front page:<br>CMP - Multi-Projets Circuits; 0.8 µm digital GaAs wafer from TCS                                                                                                |

### **MIDEM Society and its Activities**

MIDEM - Slovene Society for microelectronics, electronic components and materials is an international society integrating experts working on this field from all over the world. Main activities of the Society are:

- organization of an international professional conference on microelectronics, electronic components and materials **MIEL SD**

- □ publishing of the professional Journal Informacije MIDEM

- organization of professional seminars, workshops and colloquiums, as well as other publishing activities covering the field

Through years our Journal Informacije MIDEM has also been slowly transformed into international journal. Not only that many authors from abroad contribute their scientific-professional articles into the Journal but, as You have probably noticed, members of the Editorial Board are distinguished experts from foreign countries who guarantee high quality of the published contributions. Scientific and professional papers, as well as Journal itself are edited in such a way that they meet all requirements needed for scientific journal. All contributions have title, key words and abstract written in original, as well as in English language. They are subject to scientific review. Scientific and professional papers are assessed into domestic (Iskra SAIDC-el) and foreign data base (INSPEC).

Being expert in the field of microelectronics, electronic components and materials, You and Your colleagues are also invited to actively participate in Society activities, as well as in preparation of the Journal. Any comments, suggestions or information in oral or written forms are appreciated.

In every issue of the Journal You will find a REGISTRATION FORM as well as INFORMATION or an INVITATION to participate in the Society activities. Please, take Your time, fill in the form, write Your suggestions and ideas. For our part, we will try to do our best to constantly improve the Society service and Journal quality to fulfill Your expectations and needs.

We hope that in forthcoming year we will continue collaborating to mutual satisfaction and we wish You healthy, fruitful and successful 1994.

MIDEM Society President Dr. Rudolf Ročak

Fried 2.

Editor in Chief Iztok Šorli

Latob Sinli

# CROSS-SECTIONAL SCANNING TUNNELING MICROSCOPY ON HETEROSTRUCTURES: ATOMIC RESOLUTION, COMPOSITION FLUCTUATIONS AND DOPING

### M.B. Johnson and H.W.M. Salemink IBM Research Division, Zurich Research Laboratory, Ruschlikon, Switzerland

#### **INVITED PAPER**

21<sup>st</sup> International Conference on Microelectronics, MIEL'93 29<sup>th</sup> Symposium on Devices and Materials, SD'93 September 29 - October 1, 1993, Bled, SLOVENIA

Key words: semiconductors, STM scanning tunneling microscopy, analysis, structural properties, chemical properties, electronic properties, spatial dimensions, atomic scale, nanometer scale, Al-Ga-As-Ga-As heterostructure, measurements, dopants, UHV ultrahigh vacuum, experimental results

Abstract: Cross-sectional scanning tunneling microscopy on semiconductor structures is evolving into a technique to analyze structural, chemical, and electronic properties on the atomic and nanometer scale in all spatial dimensions, in particular in the lateral and in-depth spatial dimensions of the structure. This technique has been used on the ultrahigh vacuum cleaved (110) plane of (001)-grown AlGaAs/GaAs heterostructures. We report on measurements of i) interface roughness, as well as alloy fluctuations and ordering; ii) the variation of electronic properties over an interface as well as fluctuations within the alloy; and iii) the distribution of individual dopant sites.

# Rasterska tunelska mikroskopija presekov heteroslojnih polprevodnikov: atomska ločljivost, sestava, fluktacije in dopiranje

Ključne besede: polprevodniki, STM mikroskopija skanirna tunelna, analiza, lastnosti strukturne, lastnosti kemične, lastnosti elektronske, dimenzije prostorske, skala atomska, skala nanometerska, Al-Ga-As-Ga-As heterostrukture, meritve, dopanti, UHV vakum ultravisoki, rezultati eksperimentalni

Povzetek: Rasterska tunelska mikroskopija presekov polprevodniških struktur se razvija v tehniko, ki bo sposobna analizirati strukturne, kemične in elektronske lastnosti na atomski in nanometrski skali v vseh prostorskih dimenzijah, še posebej v lateralni in vertikalni prostorski dimenziji raziskovane strukture. Omenjeno tehniko smo uporabili na vzorcih AlGaAs/GaAs z orientacijo (001) na površini razcepljeni v smeri (110) in pripravljeni v ultravisokem vakuumu. V delu prikazujemo meritve i) hrapavosti površine kakor tudi fluktuacijo urejenosti in sestave legure, ii) spremembe elektronskih lastnosti po površini kakor tudi znotraj legure in iii) porazdelitev posameznih atomov dopantov

#### 1. Introduction:

As semiconductor devices become smaller, knowledge of the electronic properties on the nanometer scale and of the crystallographic and chemical structure on the atomic scale will be of paramount importance in all dimensions. However, conventional analytical tools do not readily afford this knowledge on such a scale. For example in molecular beam epitaxial (MBE) growth, electron diffraction is usually used during epitaxy to monitor the layer-by-layer growth, whereas high-resolution transmission electron microscopy (TEM)<sup>2</sup> and Xray diffraction3 are used to determine the structure after growth. These techniques, however, produce crystallographic information averaged over many lattice unit cells. The electronic parameters of such structures are often derived from photoluminescence<sup>4</sup> photoemission⁵ which measure semiconductor properties related to the band structure (eg. valence-band offset and band gap), including their variation across interfaces, but again averaged over many lattice unit cells in volume or a large surface area. Analysis of electronic properties of device structures by capacitance-voltage (C-V) or current-voltage (I-V) probes and spreading resistance profiling (SRP) require modeling and are difficult to extend to the lateral dimensions.6 Similarly, analysis of electronic properties of devices by means of the device performance itself requires sophisticated modeling, and the determination of the physical characteristics is difficult. Finally, chemical profiling techniques such as secondary ion mass spectroscopy (SIMS) and Auger electron spectroscopy (AES) are limited to a depth resolution in the range of 5 nm and are difficult to extend to lateral dimensions.<sup>6</sup> On the other hand scanning tunneling microscopy (STM)7-9 is an extremely surface- sensitive tool with atomic lateral res-

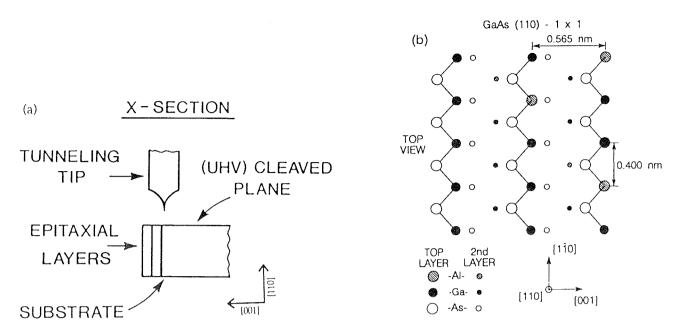

Fig. 1:

(a) Sketch of cross-sectional STM on heterostructures. © 1991 Elsevier Science Publishers B.V./ (b) Top view of atomic arrangements of the group-III Ga and AI and group-V As sites on the (110) face. Tunneling can be out of the group-V valence As states or into the group-III conduction states by negative and positive sample voltage. The [001] and [110] directions and dimensions are shown. The distance to the next monolayer in the (110) plane is 0.2 nm. © 1990 John Wiley & Sons, Inc./

olution and sensitivity to crystallographic, chemical and electronic information. Thus when used on a suitable cross-sectional surface, STM can yield structural, chemical, and electronic information in the depth and lateral dimensions with unprecedented resolution. Hence there is growing interest in the analysis of epitaxially grown multilayers by cross-sectional STM (XSTM). 10-18 Figure 1 (a) shows the XSTM configuration. The preparation of this cross-sectional surface is a crucial requirement for successful application of XSTM. The best results require an atomically flat, uncontaminated surface. This is readily achieved in the III-V materials system with a (110) facet cleaved in ultrahigh vacuum (UHV). The work of this paper concerns Al-GaAs/GaAs heterostructures (see Fig. 1(b)) where we demonstrate: i) spatial resolution and chemical sensitivity on an atomic scale, which allows the measurement of interface roughness, as well as alloy fluctuations and ordering; ii) electronic sensitivity on a near- atomic scale, which allows the measurement of the variation of band structure within alloys and across interfaces; and iii) the direct sensitivity to dopants, which allows the determination of dopant density. The extension of this work to other heterostructure systems, such as Si and SiGe, depends principally on the generation of a cross-sectional surface that is atomically flat and uncontaminated.

#### 2. Experimental

The results described in this paper are obtained with two UHV-STM's: one early system built into a UHV-compatible SEM (scanning electron microscope), 19 and a second version with optical access instead of the SEM. Both STM's have been successfully used to study cross

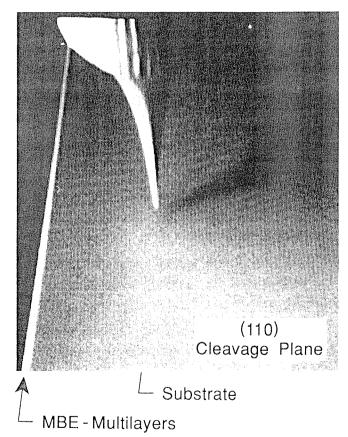

Fig 2: Secondary electron SEM image of tunneling tip in approach to cleaved multilayer stack. In the (110) cleaved cross section, the multilayer stack is seen as a white stripe to the left of the (gray) substrate (see also Fig. 1a). Note the tip shadow on the substrate due to blocking of the electron beam. This effect at close proximity (≅ 1.0 μm) is used to guide the tip towards the multilayer stack (SEM magnification factor is 10 K).

sections of nanometer-size, MBE-grown multilaver structures. The SEM is used for three purposes: i) to evaluate the apex shape of the tunneling tip, ii) to analyze the suitability of the particular cleavage plane under study and iii) to guide the STM tip into the area of interest within the heterostructure stack, typically with a positional accuracy of 25 nm. Figure 2 shows an SEM image of the tunneling tip in approach to the cleaved sample. An iterative method for guiding the tip to the edge<sup>18</sup> using reliable positioning piezo-sliders as well as more reliable tip preparation and sample cleaving methods have largely replaced the use of SEM in recent work. Pressure in the STM environments is ⋖ x 10<sup>-11</sup> mbar. The GaAs/AlGaAs multilayer samples were grown by MBE on (001) GaAs substrates. The results described here are for highly-doped p-type (Be) samples with dopant concentration ranging from 1 to -10 x 10<sup>18</sup> cm<sup>-3</sup> and Al concentration in the alloy typically Al<sub>x</sub>Ga<sub>1-x</sub>As with x=0.30 to 0.35. Various different structures are used in the stack, and several repetitions of the stack are grown to facilitate the location of the structure of interest. Atomic resolution on III-V heterojunctions became routine after several improvements were made, notably i) thinning back the substrate to 150 µm by mechanical polishing (to facilitate the (110) cleaving across the stack), ii) use of lower tunneling current (0.1 nA or lower)

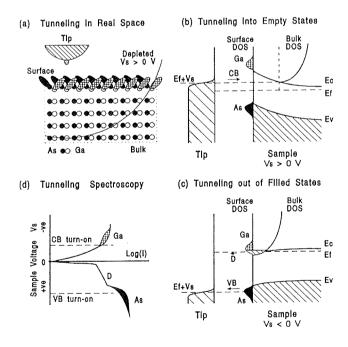

Fig 3: Schematic views of STM tunneling on n-type GaAs (clockwise). (a) Tunneling between tip and sample in real space. (b) Tunneling energy diagram for sample voltage > 0 sensitive to empty Ga and Al states; also sketched is the tip-induced band-bending with the semiconductor in depletion. (c) Tunneling energy diagram for sample voltage < 0 sensitive to filled As states; also sketched is the tip-induced band-bending with the semiconductor in accumulation. (d) Schematic current-voltage characteristic with contributions from VB and CB; D shows tunneling via dopant levels. From /26/.

and more highly doped samples and iii) optimization of the tip preparation procedure.<sup>20</sup>

The atomic arrangement on the (110) cleavage plane (top view) is drawn in Fig. 1(b). Note that for AlGaAs material a fraction of the group-III sites is replaced. On the charge-neutral (110) plane the group-III and V atoms maintain their valence character. As a result the filled (group V) and empty (group III) states can be sensed by tunneling out of or into the sample<sup>8</sup> as shown in Fig. 3. In addition the valence and conduction band (VB and CB) turn-ons can be determined with respect to E<sub>F</sub> via simultaneous current voltage spectroscopy. <sup>21, 22</sup> Spectroscopy on the clean UHV cleaved III-V (110) surface displays both VB and CB band onsets and a gap region of approximately 1.45 eV, free of surface states, as reported previously. <sup>21</sup>

#### 3. Results and Discussion

In this work we describe four different sets of STM measurements, each associated with various aspects of GaAs/AlGaAs heterostructures. They are: i) filled-state images that show AI sensitivity and hence interface roughness as well as alloy fluctuations and ordering. Furthermore these images allow the determination of the layer metrology by STM and this is compared to that obtained with HRTEM; ii) filled-state images in combination with I-V spectroscopy that are sensitive to the variation of the band structure across a AlGaAs/GaAs interface and within the AlGaAs layer; and iii) filled-state images of a Be-doped GaAs buffer layer, of a Zn-doped GaAs substrate, and of a Be-doped sample with variable doping concentrations that are directly sensitive to the electronically active dopant atoms and allow the direct measurement of dopant density.

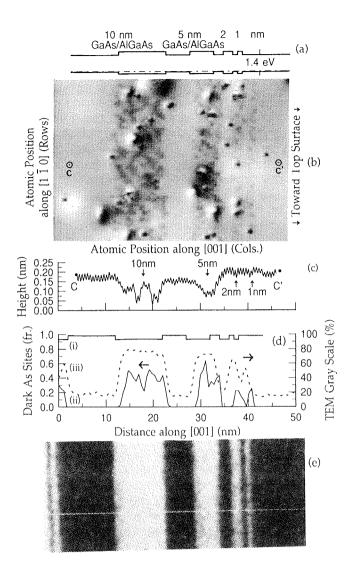

An STM image of a heterostructure stack consisting of a series of adjacent, equally thick pairs of Alo.3 Gao.7 As/GaAs layers of 10, 5, 2, and 1 nm thickness is shown in Fig. 4./see Ref. 23/ Figure 4(a) shows the bulk-band diagram for the stack. Figure 4(b) shows an area of nearly 30 x 50 nm with all layers in one period of the stack clearly displayed. The image was taken with a sample voltage of -2.1 V and a demand current of 0.1 nA, thus probing the As-related filled states.8 Note that atomic corrugation is apparent in both the [001] and [110] directions. In the image in Fig. 4(b) the GaAs regions are uniform, while the AlGaAs ternary regions have a mottled texture.<sup>24</sup> Several types of localized features are present in the layers, but the discussion here concerns the clean regions. Figure 4(c) shows that the topographic corrugation on line C-C' of Fig. 4(b) extends through one period of the stack along the [001] direction away from localized contamination features. In the GaAs regions the corrugation is regular with an amplitude of 0.03 nm, while in the 10 and 5 nm thick AlGaAs layers the corrugation is irregular and the layers appear nearly 0.1 nm lower than the surrounding GaAs. The smaller 2 and 1 nm thick AlGaAs layers are observ-

Fig. 4: Large-scale STM image of a (110)-cleaved GaAs/AlGaAs heterostructure stack. (a) Calculated bulk-band structure for the as-grown heterostructure. (b) Topographic image of the stack taken with a sample voltage of -2.1 V and a demand current of 0.1 nA. The image is nearly 50 x 50 nm and the As sublattice is indexed along the [110] and [001] directions. The relative tip height is represented by a gray scale, from 0 (black) to 0.43 nm (white). Topographic corrugation along line C-C' in registry with that displayed in (b). (d) Comparison of STM with dark-field TEM. (i) Intended growth plan. (ii) TEM gray scale across layers from dark- field image (e) (iii) Fraction of dark As sites along a [110] corrugation line in the neighborhood of C-C' versus position along the [001] direction. (e) TEM dark-field image of the stack in registry with (d). From /23/.

able, but their contrast is much less than that of the two thicker layers. Note that this height variation is not real topography because there are no atomic steps on the surface; instead, it is electronic in nature. The regular corrugation in the GaAs is the result of the homogeneous As surface site bonding configuration there. In contrast, the bonding configuration of As surface sites in the ternary AlGaAs is variable depending on the number

of Al nearest-neighbor sites. Because the Al-As bond is more ionic than the Ga-As bond. At nearest-neighbors result in more charge being transferred to the nearest As sites, thereby lowering the energy and changing the spatial extent of the As-related surface state. Thus the As corrugation fluctuates depending on the number of Al atoms bonded to the surface As. Conversely the fluctuation of the As corrugation indicates a variation of the number of Al atoms bonded to the surface As. The apparent topographic lowering in the thicker AlGaAs layers is the result of the different electronic properties of the barrier region; it most probably occurs because the barriers are completely depleted, which requires the tip to approach the surface. The distance over which this apparent height varies from GaAs to the AlGaAs - about 3-4 [001] corrugations - and the lack of contrast in the 1 and 2 nm barrier is consistent with the expected wave function penetration of the holes from the quantum wells into the barriers that result from the near-atomic scale variation of band offsets.

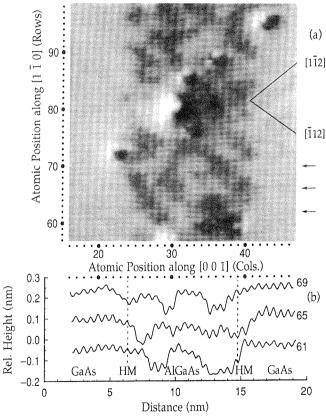

Figure 5 shows an expanded image of the 10 nm thick AlGaAs layer. The occurrence of dark or light bands 3-4 lattice spacings in width (about 2 nm) extending in the [112] and [112] directions is clearly visible (it is also displayed in parts of the 5 nm layer). This suggests that

Fig. 5: Expanded STM image of 10 nm AlGaAs layer in Fig. 4 (a) Topographic image of an area of about 20 x 20 nm; relative tip height represented by a gray scale from 0 (black) to 0.38 nm (white). The [112] and [112] directions are indicated. (b) Topographic line scans along rows 61, 65, and 69 as indicated. The positions of the half- maximum of the AlGaAs layer are indicated by HM. From /23/

Al-rich regions nucleate at the GaAs/AlGaAs interface in isolated positions and grow preferentially. The interfaces shown in Fig. 5 also have roughness on this 2 nm length scale. This is in agreement with measurements made by other techniques.<sup>2</sup>

Finally, we consider quantitative metrology of these layers on the (sub-)nanometer scale. Let us consider selected contamination-free regions in the image in Fig.4(b) that span the entire superlattice period in a piecewise manner near line C-C'. From these regions we can determine the fraction of dark As sites along the [110] row in this area. In Fig. 4(d) curve (iii) shows this fraction of dark As positions plotted versus its position along the [001] direction - typically more than 30 sites per vertical line are counted. This fraction of dark As positions is indicative of the Al fraction, and is sufficient for estimating the actual thickness of the layers grown, as shown. Curve (ii) is the percentage gray scale from the TEM dark field image shown in Fig. 4(e) which is also indicative of Al content. And finally, curve (i) indicates the intended growth plan for the stack. Comparing curves (ii) and (iii) (STM and TEM) shows 4% agreement in the layer thickness's which is reasonable, considering that different parts of the wafer were measured. Note the TEM and STM-measured GaAs layers are systematically longer than the matching AlGaAs layer.

Local I-V curves can be acquired simultaneously with the topography to assess the transition in the electronic band structure across the GaAs- AlGaAs interface. /see Ref. 22/In Fig. 5(a) the filled-state image of an interface is shown together with the sampling points for the I-V curves at a 1.5 nm grid. In the interest of high stability in spectroscopy, topographic resolution is traded off slight-Iv. A set of I-V curves from a line across the interface is shown in Fig. 5(b) and the transition region is noted by the drop in the VB turn-on voltage. The observed VB turn-on energy is plotted as a function of distance to the interface in Fig. 5(c) together with the calculated positions for the bulk (C) and surface (S) VB edge energy. The tip-induced electrostatic depletion of the semiconductor is explicitly taken into account in curve (S). 22 The lack of change at the CB onset is somewhat surprising and possibly due to interference with surface states. Note the fluctuations in the VB edge in the AlGaAs from the experimental data: this might reflect the local variation of the VB edge energy due to the Al fluctuations (Fig. 4) and the effect of the lateral extent of the depletion region present during spectroscopy measurements /.Fig. 1(a)/. The data in Fig. 5 demonstrate the measurement of electronic band parameters on a near-atomic scale in semiconductor structures.

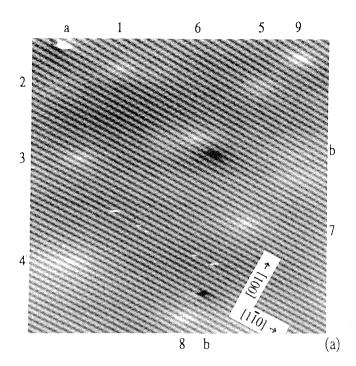

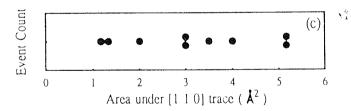

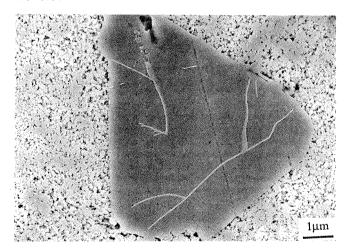

Figure 7 shows a filled-state image of a Be doped p-type GaAs MBE-grown buffer layer with  $p=1 \times 10^{19}$  cm<sup>-3</sup>. /see Ref. 25/ Nine hillock features are observed scattered throughout the 31 x 29 nm scan and labeled on the perimeter of the image. Figure 7(b) shows corrugation traces across several of these hillock features in [001] and [110] directions. In Fig. 7(b) the hillocks have a height of up to 0.02 nm and a diameter of about 2

Fig. 7:

(a) STM image of a (110)-cleaved, 1 x 1<sup>19</sup> cm<sup>-3</sup>, Be-doped GaAs surface. Image displays 31 x 29 nm of the As sublattice taken with sample voltage -2.1 V and demand current 0.1 nA. The relative tip height is represented by a gray scale from 0 (black) to 0.2 nm (white). Nine hillocks (dopants) are identified using numbers at the closest point on the perimeter. (b) Tip height traces along the [110] direction of a selection of the hillocks identified in (a). (c) Scatter plot of area under the [110] tip height traces (integrated intensity) of all nine hillocks - note the uniform distribution. From /25/

nm.<sup>25,26</sup> These hillocks correspond to the enhancement of the surface density of states expected in the neighborhood of Be acceptor sites which gives rise to a slight increase of the tip-surface distance as observed. The observed diameter - roughly the size of the acceptor

Bohr radius (2.5 nm) - and height of these hillocks are in agreement with calculations of the change in the surface density of states due to a nearby dopant and its effect on tunneling process. At a doping density of 1 x 10<sup>19</sup> cm<sup>-3</sup> in the area shown in Fig. 7(a) one expects two dopant atoms per monolayer. Thus the observation of nine hillocks indicates a sensitivity to dopant atoms in the top five monolayers corresponding to about 1 nm (the distance between monolayers is 0.2 nm in the [110] direction). This is in agreement with the acceptor Bohr radius and the calculations described above.<sup>27</sup>

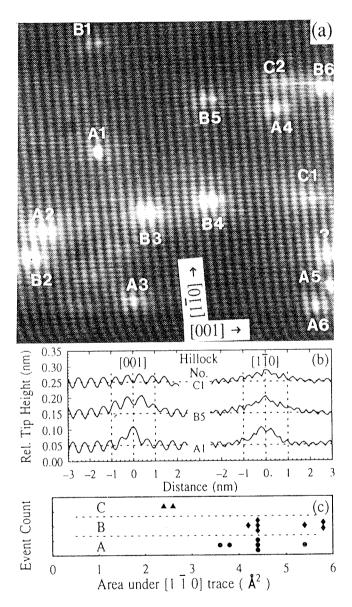

Fig. 8:

(a) STM image of a (110)-cleaved, 5 x 10<sup>19</sup> cm<sup>-3</sup>, Zn-doped GaAs surface. Image displays 20 x 28 nm of the As sublattice taken with sample voltage -2.1 V and demand current 0.1 nA. The relative tip height is represented by a gray scale from 0 (black) to 0.2 nm (white). Six type A hillocks, six type B hillocks, and one type C hillock are identified with numbers. (b) Tip height traces along the [110] and [001] directions of a selection of the hillocks of type A, B, and C identified in (a). (c) Scatter plot of area under the [110] tip height traces (integrated intensity) or all hillocks labeled. From /25/

Figure 8 shows a filled-state image of a very highly-Zn doped p-type GaAs substrate buffer layer with p =5 x 10<sup>19</sup> cm<sup>-3</sup>. /see Ref. 25/ Many hillock features are scattered throughout the 20 x 28 nm scan. The prominent hillock features are labeled A, B and C according to their symmetry. Corrugation traces of examples of each of these types of hillock in [001] and [110] directions are shown in Fig. 8(b). The diameter and height of these hillocks are similar to those observed above for the Be-doped buffer layer. Moreover in this case, the number and symmetry of the features indicate that hillock feature A corresponds to a dopant in the top layer, feature B to a dopant in the second layer and C to a dopant in a still deeper layer. Thus the dopant can be localized in all three dimensions with atomic precision.

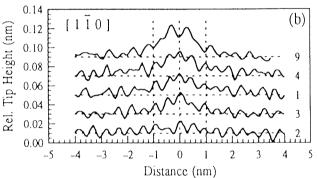

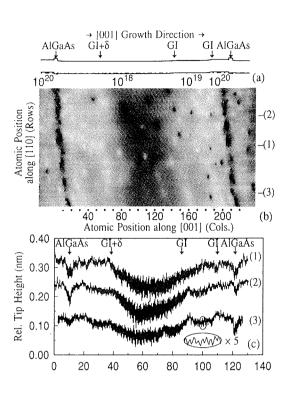

An STM image of a heterostructure modulation-doped stack consisting of 100 nm thick layers of Be-doped GaAs between 2.5 nm thick AlGaAs marker layers is shown in Fig. 9. /see Ref. 28/ Figure 9(b) is a large-scale STM image and (c)-(f) present a series of depth profiles (along the growth direction) over a single set of the modulation-doped layers. Figure 9(b) shows the 100 x 50 nm STM topographic image of a set of GaAs layers including the AlGaAs marker layers (spotted dark vertical lines) imaging the filled As states. Above and in registry with Fig. 9(b), Fig. 9(a) shows the intended growth plan including Be concentration, growth interruptions (marked GI), and the delta-doped layer (marked  $\delta$ ). Figure 9(c) shows several horizontal line scans taken across Fig. 9(b) at the positions indicated. Note that atomic corrugation is observed throughout the STM image as indicated in the inset (enlarged 5x). In the STM image /Fig. 9(b)/ the dark spots are cleave-induced As vacancies<sup>5</sup> and are not of interest here. The white spots indicate individual ionized dopants in the top several atomic layers. They are typically 2 nm in diameter and about 0.05 nm in height as shown above. The overall contrast - dark in the middle and bright on the sides - is due to the tip approaching the sample by about 0.1 nm in the low doped region in the middle of the image as indicated by the line scans in Fig. 9(c). Figure 9(f) shows SIMS and C-V profiles of a typical set of the GaAs layers between the AlGaAs markers. Figure 9(d) plots a line scan corresponding to the average of all the line scans making up the top half of the image in Fig. 9(b). Figure 9(e) is a histogram plot of the white spots (ionized dopant sites) counted in 10-nm- wide vertical stripes between the marker layers versus horizontal position along with the SIMS data (dotted) for comparison. The disagreement between the intended doping and the SIMS data is due to the segregation to the surface, and to bulk diffusion of the Be during growth. The SIMS plot is thought to reflect the actual Be concentration. Figure 9(d) shows qualitative agreement between the linear plot of the average tip height and the logarithmic plot of the Be concentration. The average tip height is sensitive to the dopant concentration because the surface band bending under the tunneling tip that affects the tip height is governed by the dopant concentration. The histogram of the Be dopant sites in Fig. 9(e) shows quantitative agreement with the SIMS Be concentration. This agree-

Fig. 9: Large-scale STM image of GaAs layers with variable dopant concentration and various depth profiles. (a) Calculated bulk-band structure for the intended heterostructure. In registry below, (b) shows the topographic image, 100 x 50 nm in size, of the layers taken with sample voltage -2.1 V and demand current 0.1 nA. The relative tip height is represented by a gray scale from 0 (black) to 0.2 nm (white). (c) Several topographic line scans across the image (b) along the [100] direction with the AlGaAs layers vertically aligned. Note the atomic corrugation shown in inset. (d) Line scan (solid) corresponding to the averaged line scan over the top half of Fig. 1(b) taking the slight drift into account. The line scan is smoothed slightly to remove atomic corrugation and is compared to the Be concentration measured by SIMS (dotted, right log. axis). (e) Dopant histogram determined by counting the white hillocks (dopants) in a series of rectangles across (b) (solid, left linear axis) and compared to the measured Be concentration measured by SIMS (dotted, right linear axis). (f) Be concentration (solid) and Al counts (dotted) measured by SIMS as well as dopant concentration determined by Polaron C-V analysis (dashed). From /28/

ment is for a sensitivity of the STM to the top 1 nm as was observed above. Thus both the dopant number and the relative tip height can be used to indicate the dopant concentration. The former shows the actual position of the dopant while the latter shows the behavior of the bands at the surface which is sensitive to the carrier concentration. Note the weak signature of the delta-doped layer is observed in the SIMS profile, the average tip height profile in Fig. 9(d), and dopant number histogram in Fig. 9(e). Thus STM appears to be an ideal tool for the study of such delta-doped layers.

#### 4. Summary

Cross-sectional STM on heterostructures is evolving into a technique to analyze structural and electronic

properties on the atomic and nanometer scale in all spatial dimensions. Because of the cross-sectional aspect involved, this represents both lateral and in-depth spatial dimensions. Other conventional techniques average one or more dimensions over a given length scale. In this work on the (110) plane of (001)-grown III-V heterostructures this high-resolution capability has been used to measure directly: i) interface roughness as well as alloy fluctuations and ordering; ii) the variation of electronic properties over an interface as well as fluctuations within the alloy; and iii) the distribution of individual dopant sites. In the future, such issues as incorporation of bulk and delta doping as well as their interdiffusion in III-V materials can be investigated. The extension of this technique from III-V materials to other heterostructure systems, such as Si and SiGe structures, is critically dependent on the preparation of a suitable cross-sectional surface.

#### Acknowledgments

We acknowledge the MBE growth provided by H.P. Meier, expert sample preparation by L. Perriard and H. Richard, technical assistance from U. Maier, STM software provided by B. Michel, transmission electron microscopy provided by R. Broom, and SIMS analysis provided by F. Cardone.

#### REFERENCES

- 1. J.M. van Hove, P.I. Cohen, J. Cryst. Growth 81, 13 (1987).

- 2. A. Ourmazd, D.W. Taylor, J. Cunningham and C.W. Tu, Phys. Rev. Lett. **62**, 933 (1989).

- 3. J.M. Vandenberg, R.A. Hamm, M.B. Panish, and H. Temkin, J. Appl. Phys. **62**, 1278 (1987).

- 4. B.G. Streetman and Y.C. Shih, J. Vac. Sci. Technol. B 10, 296 (1992).

- 5. E.T. Yu, D.H. Chow, and T.C. McGill, Phys. Rev. B 38, 12764 (1988).

- 6. See Proc. of the First Int'l Workshop on the Measurement and Characterization of Ultra-shallow Doping Profiles in Semiconductors, J. Vac. Sci. Technol. B 10, (1992). In particular W. Vandervorst and T. Clarysse, J. Vac. Sci. Technol. B 10, 302 (1992).

- 7. G. Binnig, Ch. Gerber, H. Rohrer, and E. Weibel, Phys. Rev. Lett. 49, 57 (1982).

- 8. R.M. Feenstra, J.A. Stroscio, J. Tersoff, and A.P. Fein, Phys. Rev. Lett. **58**, 1192 (1987).

- 9. R.J. Hamers, R.M. Tromp, and J.E. Demuth, Phys. Rev. Lett. **56.**, 1972 (1986).

- 10. S. Hosaka, S. Hosoki, K. Takata, K. Horiuchi, and N. Natsuaki, Appl. Phys. Lett. **53**, 487 (1988).

- 11. S. Kordic, E.J. van Loenen, D. Dijkkamp, A.J. Hoeven, and H.K. Moraal, J. Vac. Sci. Technol. A **8**, 549 (1990).

- 12. H.W.M. Salemink and O. Albrektsen, J. Vac. Sci. Technol. B 10. 1799 (1992).

- 13. P. Muralt, Appl. Phys. Lett. 49, 1441 (1986).

- 14. P. Muralt, H. Meier, D.W. Pohl, and H.W.M. Salemink, Appl. Phys. Lett. **50**, 1352 (1987).

- 15. H.W. Salemink, H.P. Meier, R. Ellialtioglu, J.W. Gerritsen, and P.R. Muralt, Appl. Phys. Lett. **54**, 1112 (1989).

- 16. R.M. Feenstra, E.T. Yu, J.M. Woodall, P.D. Kirchner, C.L. Lin, and G.D. Pettit. Appl. Phys. Lett. 61, 795 (1992).

- 17. M.B. Johnson and J.M. Halbout, J. Vac. Sci. Technol. B 10, 508 (1992).

- 18. E.T. Yu, M.B. Johnson, and J.-M. Halbout, Appl. Phys. Lett. **61**, 201 (1992).

- 19. Ch. Gerber, G. Binnig, H. Fuchs, O. Marti and H. Rohrer, Rev. Sci. Instrum. **57**, 221 (1986); Vacuum Generators VG-HB 100 Multi-lab UHV-SEM/SAM.

- 20. O. Albrektsen, K.A. Mörch, A.R. Thölen and H. Salemink, in preparation.

- 21. R.M. Feenstra and J.A. Stroscio, J. Vac. Sci. Technol. B 5, 923 (1987).

- 22. H.W.M. Salemink, O. Albrektsen, and P. Koenraad, Phys. Rev. B 45, 6946 (1992).

- 23. M.B. Johnson, U. Maier, H.-P. Meier, and H.W.M. Salemink, Appl. Phys. Lett. **63**, 1273, (1993).

- 24. O. Albrektsen, D.J. Arent, H.P. Meier, and H.W.M. Salemink, Appl. Phys. Lett. **57**, 31 (1990).

- 25. M.B. Johnson, O. Albrektsen, R.M. Feenstra, and H.W.M. Salemink, Appl. Phys. Lett. **63**, 2923, (1993).

- 26. M.B. Johnson, H. Salemink, O. Albrektsen and E.T. Yu, Proc. of 7th Int'l Winter School, Mauterndorf, Austria, February 24-28, 1992, in "Low-Dimensional Electronic Systems," edited by G. Bauer, F. Kuchar and H. Heinrich (Springer-Verlag, Berlin, 1992) pp.108-119.

- 27. S.M. Sze. Physics of Semiconductor Devices, 2nd Edition, (Wiley, New York, 1981).

- 28. M.B. Johnson, H.P. Meier, and H.W.M. Salemink, Appl. Phys. Lett. **63**, 3636, (1993).

M.B. Johnson and H.W.M. Salemink IBM Research Division, Zurich Research Laboratory, 8803 Rüschlikon, Switzerland tel. +41 1 724 86 47 fax. +41 1 724 31 70

Prispelo (Arrived): 11.12.93 Sprejeto (Accepted): 23.12.93

# MIXED BIPOLAR-CMOS-DMOS SMART POWER IC TECHNOLOGY

### Carlo Cini SGS - THOMSON Microelectronics, Milano, Italia

#### **INVITED PAPER**

21<sup>st</sup> International Conference on Microelectronics, MIEL'93 29<sup>th</sup> Symposium on Devices and Materials, SD'93 September 29 - October 1, 1993, Bled, SLOVENIA

Key words: semiconductors, integrated circuits, BCD technology, power transistors, bipolar transistors, CMOS circuits, DMOS circuits, power ciircuits, signal circuits

**Abstract:** First introduced in the mid eighties, mixed bipolar-CMOS-DMOS (BCD) smart power IC technology has brought significant advances in the art of integrating signal and power circuits on the same chip. This paper describes the origin and evolution of the BCD technology family from the beginning to the present day, using as examples some practical integrated circuit designs that exploit effectively its benefits.

# Mešana bipolarna - CMOS - DMOS tehnologija za pametna močnostna integrirana vezja

Ključne besede: polprevodniki, vezja integrirana, BCD tehnologija, transistorji močnostni, transistorji bipolarni, CMOS vezja, DMOS vezja, vezja močnostna, vezja signalna

Povzetek: Od sredine osemdesetih let, ko se je prvič pojavila, pa do danes, je mešana bipolarna - CMOS - DMOS (BCD) tehnologija omogočila izreden napredek in prinesla nove možnosti pri integraciji digitalne in močnostne elektronike na enem čipu. V tem prispevku opisujemo začetke in razvoj družin BCD tehnologij do danes. Obenem predstavljamo nekaj načrtanih in izdelanih integriranih vezij kot praktične primere vseh možnosti, ki jih ta tehnologija ponuja.

#### INTRODUCTION

In the early eighties power integrated circuits were produced using pure bipolar technology. These devices, mainly operating in switching mode, were severely limited by the poor efficiency of bipolar power transistors. This poor efficiency meant that a significant amount of power was dissipated inside the device, and since there is a limit to the dissipation capacity of an IC package this represented a fundamental limitation on the delivered power available. Pure bipolar power ICs suffer from another limitation: the poor density of bipolar logic.

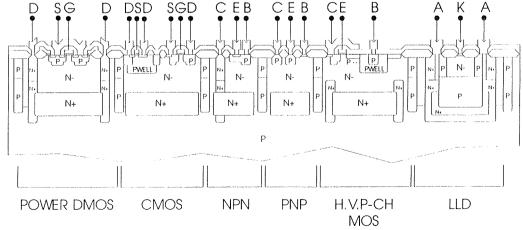

Clearly the answer to these problems was to use DMOS/CMOS technology. DMOS power devices solved the dissipation problem, while CMOS provided very high density signal circuits. However, at the same time it was necessary to guarantee the high-precision analog performance that only bipolar technology can provide. Consequently the ideal solution was to combine bipolar, CMOS and DMOS on the same chip. This was achieved by SGS-THOMSON in 1986 with the introduction of a new technology called Multipower-BCD.

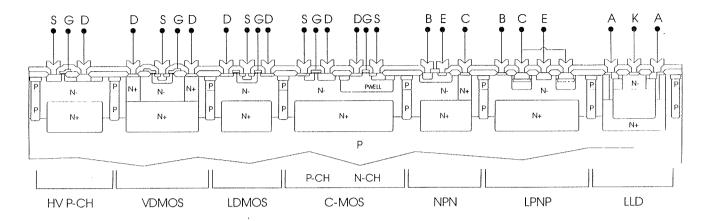

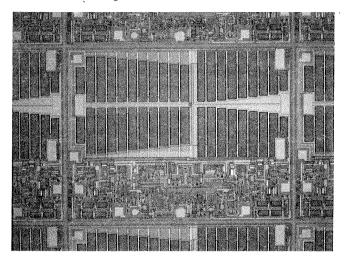

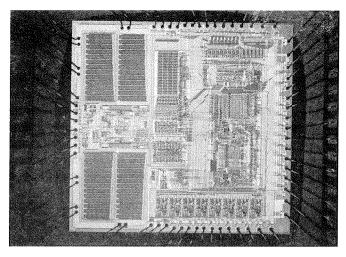

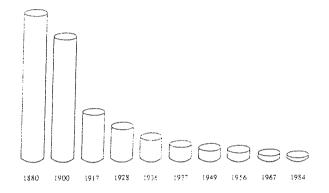

While most smart power IC processes are created by adding power elements to an existing signal process or vice-versa, "BCD" technology emerged from a project to develop a completely new, optimal process. Borrowing elements from junction- isolated IC technology and discrete DMOS technology, it allowed the integration of bipolar, CMOS and DMOS structures on the same chip (figure 1).

IC technologies combining power DMOS with signal circuits had existed previously, but where this technology differed lay in the use of isolated DMOS power transistors having all of the contacts on the top surface. In contrast, other processes used discrete-type DMOS structures where the lower surface of the die is the drain contact, so that two or more DMOS devices can only be placed on the same chip if they have a common drain contact. In contrast, with Multipower-BCD designers were free for the first time to integrate any number of DMOS power transistors connected in any way including bridge configurations.

In the first version of BCD technology, now called BCDI, the minimum breakdown voltage was specified at 60V, a figure defined by the original target application of the

## MULTIPOWER BCD 20/60 II

Fig. 1 "BCD" technology, developed in the mid-eighties, combined vertical DMOS and junction isolation technologies.

Since the DMOS transistors are fully isolated and have all contacts on the top surface any kind of power stage can be integrated.

Fig. 2 Because BCD technology allows the integration of isolated DMOS transistors it became possible to realize integrated circuits like this H bridge motor driver, the first BCD IC to be marketed.

technology. BCDI was developed at a time when most smart power devices were used in applications like motor and solenoid driving in computer peripherals, where supplies for 30-50V are commonly used.

The first commercial product to be developed using this technology was the L6202 H-bridge motor driver (figure 2). A bipolar bridge with identical power performance was designed at the same time for the purpose of comparison. Both chips operated on 48V supplies and delivered 1.5A continuous output current. But while the L6202 was assembled in a DIP package and needed no heatsink, its bipolar counterpart needed a power package and a hefty heatsink. Eliminating this heatsink was a dramatic demonstration of the importance of reduced dissipation in power ICs.

There were other advantages in favor of the BCD version, too. Since a DMOS power stage has intrinsic

recirculation diodes no external discrete diodes were needed, saving components. Moreover, the BCD version offered CMOS logic, which allowed designers to consider the use of complex logic in power ICs.

Though the BCD IC had many advantages over a bipolar equivalent it should be emphasized that the die size of the two chips was almost identical. And since the BCD process uses standard production equipment and is roughly equivalent in terms of process complexity this means that the die cost was comparable.

#### HIGHER CURRENT

Having demonstrated the benefits of low dissipation, designers set out to explore other limits of power IC technology, beginning with output current. The first BCD

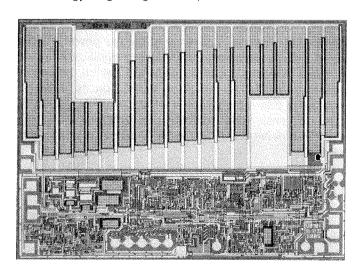

Fig. 3 BCD technology has also been applied effectively in the power supply field. This high power switching regulator IC delivers 10A output current, more than twice that of an equivalent bipolar power IC.

IC to enter this unexplored territory was the L4970 switching regulator, a one-chip switchmode power supply delivering 10A output current (figure 3).

To deal with current levels this high it was necessary to have two thicknesses of interconnect metal: a thin layer for normal signal interconnections and a thicker layer for the main connections to the DMOS power transistor. This thicker metal reduced the voltage drop on the metal tracks inside the chip, while the thinner signal metal allowed the use of finer pitches, hence greater density.

A new bonding technique was developed, too, to reconcile the conflicting needs of power and signal connections. Thick aluminum bonding wires are needed for the high current connections because a single gold wire would be insufficient and multiple wires inherently unreliable. However, these thicker wires need a larger bonding pad on the die so if they were used for all of the connections silicon area would be wasted. The answer to this problem was to use thick aluminum wires just for the power connections and thin gold wires for the signal connections.

Operating at switching frequencies up to 500kHz the L4970 also demonstrated the speed advantage of DMOS power transistors in fast switching designs. Even at high frequencies the efficiency of the device is high enough to allow a DIP- packaged version to deliver 4A the output current capability of a similar bipolar device in a Multiwatt power package.

#### HIGHER VOLTAGE

After raising the current limits, smart power designers turned towards higher voltages to extend the range of applications. The first step was the development of a 100V version, designed to satisfy the needs of applica-

Fig. 4 High voltage technology is useful in both industrial and telecom applications. This IC, produced with 250V BCD technology, is a solid-state hook switch for telephone sets.

tions in telecommunications and automotive. Though the battery voltage in automotive applications is only 12V this higher voltage capability is needed to ensure survival in an environment where high voltage transients occur.

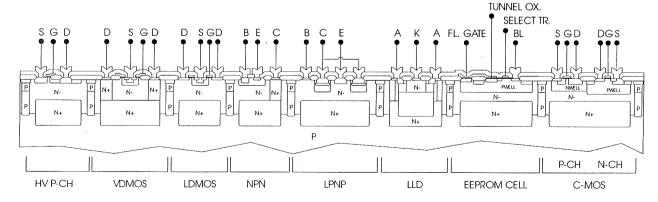

The 100V process was followed by a 250V version, aimed at telecom and industrial applications. While it was sufficient to increase the epitaxial layer thickness to reach 100V, more substantial changes were required to reach 250V. Most important of these is the use of a technique where the isolation diffusions are made in two parts. A seed of dopant is implanted in the substrate before epi growth; during subsequent processing this expands, meeting a conventional diffusion from above (figure 5).

## **MULTIPOWER BCD 250**

Fig. 5 Cross section of the BCD250 technology. Compared to the lower voltage versions, this 250V technology has a thicker epitaxial layer so the top-bottom isolation technique is used.

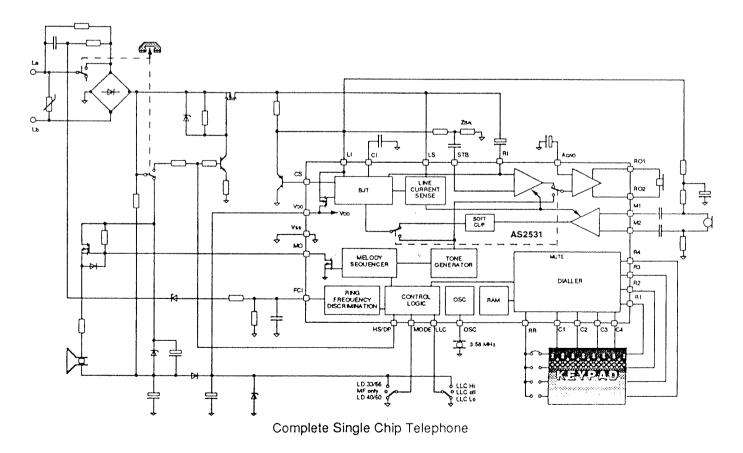

An example of the application of high-voltage technology in the telecom field is the telephone hook switch shown in figure 4.

In the high voltage field another version called BCD-Offline extends the capability of the technology to "offline" voltages (up to 700V). This process exploits the reduced surface field approach to integrate lateral DMOS highvoltage transistors.

BCD-Offline combines on a single chip low voltage CMOS and bipolar control circuits with high-voltage grounded-source lateral double-diffused MOS transistors (HV LDMOS) and grounded-source lateral insulated gate bipolar transistors (HV LIGBT). In source-follower configuration the source can float up to 20V.

A full custom circuit for a fluorescent lamp application is the first circuit in BCD- Offline technology to be qualified for production. This circuit, shown in figure 6, includes all of the functions for a fluorescent lamp driver in the preheat, ignition and on-state phases, driving two external MOS transistors.

Other products in development or qualification include a custom lamp driver with power factor correction and a high voltage half bridge driver aimed at appliance motor applications. This motor driver will be a standard part sold on the merchant market. BCD-Offline circuits are also in development for other applications such as power supplies.

SGS-THOMSON has derived lower voltage versions of this technology, rated at 300V and 170V, which will be suitable for application fields such as telecom, where circuits using high voltage technology are used to produce subscriber line interface circuits and hook switches.

#### HIGHER COMPLEXITY

While the trends towards higher current and voltage were easily predictable, at the end of the eighties a new trend emerged that was not expected by most experts in the field: the advent of high complexity smart power ICs.

Two factors made this possible. Firstly, the fact that BCD technology allowed the integration of isolated DMOS transistors meant it was possible not only to integrate any kind of power stage, but also any number of power stages. Second, the dissipation of power DMOS transistors was low enough to ensure that when multiple power stages are integrated the overall power dissipation is within the limits of normal packages.

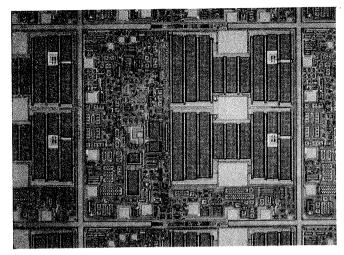

High complexity smart power reached the market in 1988 when SGS-THOMSON introduced a single IC that integrated two 1A stepper motors drivers, a 3A solenoid driver and a 5V switchmode power supply (figure 7). This

Fig. 6 A new development, "BCD-Offline" technology is suitable for offline supply circuits or fluorescent lamp ballast circuits, like the proprietary device shown in this photo.

Fig. 7 The first example of an LSI smart power IC, this circuit integrates two 1A motor drivers, a 3A solenoid driver and a 5V switching power supply.

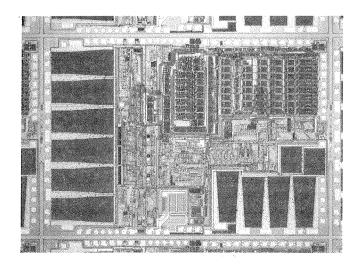

Fig. 8 When the second generation 2.5 µm BCD technology was introduced it was applied to make very complex ICs like this disk drive circuit that integrates the spindle motor driver and head positioner of a hard disk drive.

Fig. 9 Another example of LSI smart power is this IC that controls and drives the three motors of a fax machine. Because of the very low dissipation of the power DMOS output stage this IC is packaged in a plastic PLCC package.

chip, designed for a portable typewriter application, was controlled by loading commands through a bus into a set of internal registers. Among the innovative features of this device was the use of output stages that could be configured under software control.

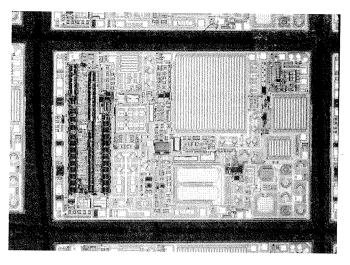

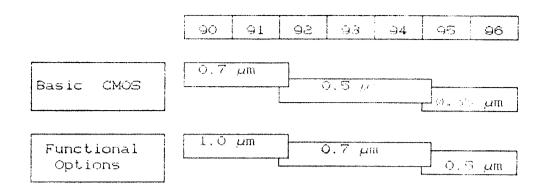

The arrival of complex smart power chips prompted an acceleration of the trend towards finer lithographies. In fact soon after the introduction of the L6280 a second generation BCD process was introduced with 2.5m lithography. This doubled both the current density in the power stages and the component density in the signal section. As a result complex chips became much more cost effective.

This second generation BCD technology has found applications in many fields. One area where it has had the greatest impact is in hard disk drives for computers. Very little space is available in 2.5" and sub 2.5" drives, so

Fig. 11 The first smart power IC to integrate a microcontroller, this technology demonstrator IC combines an 8-bit microcontroller core plus a 3A/60V power section.

drive designers are always looking for new ways to reduce the component count. With BCD2 they were able to integrate all of the circuits for controlling the spindle motor and head positioner on a single chip. Figure 8 shows a circuit that integrates this function.

Similar circuits are used in other products where several motors must be driven. An example is the complex IC shown in figure 9, which was developed for a Japanese fax machine application. This IC drives the scanner, paper feed and cutter motors.

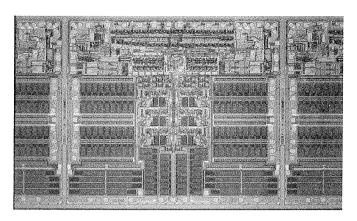

In 1993 a third generation BCD technology was announced (figure 10). Compared to the second generation this version offered a significant gain in density, thanks to a shrink from 2.5 to 1.2  $\mu$ m lithography. More importantly, however, it brought the process into line with SGS-THOMSON's CMOS processes used for logic and memory circuits. Consequently, this version not only allows the integration of bipolar, CMOS and DMOS, but

# MULTIPOWER BCD 20/60 III

Fig. 10 In the third generation BCD technology minimum linewidths of 1.2 µm are used. Other important characteristics are two levels of polysilicon, three levels of metal and a modular process structure that permits the inclusion of additional functions like EEPROM to the basic flow chart.

it also lets designers insert in a BCD chip any cell or macrocell available within the company, including micro cores and advanced non-volatile memories.

Designers have been wary of the idea of integrating a micro on a power chip, expressing concerns that high voltage, high current pulses might disturb the micro. To allay these fears a demonstrator chip was produced in the spring of 1993 that integrated a 60V/3A bridge and a standard SGS-THOMSON ST6 microcomputer core (figure 11). Since this was a demo chip designed to demonstrate feasibility the program memory was external. In fact all of the internal connections in this chip are available externally for evaluation purposes.

Future evolutions of BCD technology, already planned, will reduce the lithography to 0.8 then 0.5  $\mu m.$  In addition, new functionalities like flash memory will be added.

Technologies like BCD3 make it possible to reduce the component count of applications by integrating a microcontroller with the circuits it controls. However, the technology also allows designers to create a completely new type of general purpose power integrated circuit that is completely defined by software. Such circuits will have a microcontroller, memory, supply and some uncommitted power DMOS devices. Through software it will be possible to define the output configurations and define the functionality of the circuit. These general purpose circuits will become the power equivalent of PLDs, and greatly simplify small production runs or prototyping where a large volume custom circuit is unthinkable.

#### **EMERGENT APPLICATIONS**

In parallel with the development of these very high complexity circuits, there has also been an increase in the number of application fields where smart power technologies like BCD are applied.

While the technology was first applied in computer peripherals, it has spread to other sectors such as automotive, telecom and consumer. Automotive applications are primarily in the control and driving of motors, solenoids and relays, all applications that are growing very rapidly as electronic engine controls and electronic-

based systems like ABS become more common. In addition, though, smart power is also a key technology behind multiplex wiring schemes. Telecom applications of smart power technologies include functions like the telephone hook switch, and subscriber line interface components for switching systems. Consumer applications include audio power amplifiers, like the 100W/100V device shown in figure 12, and power circuits for monitors, TVs and VCRs.

Fig. 12 In addition to the trend towards greater complexity, there is also a trend to use smart power technologies in new application areas. This audio power amplifier, for example, uses BCD100 technology to achieve an unprecedented 100W output power (180W peak).

Additionally there are some important new application areas related to the development of high voltage technology: fluorescent lamp driving and motor control for appliances. In both cases there is a major new market driving technology and product development.

Carlo Cini SGS - THOMSON Microelectronics via Tolomeo 1, 20010 Cornaredo Milano, Italia tel. +39 2 935 191 fax. +39 2 935 19473

Prispelo (Arrived): 23.01.94

Sprejeto (Accepted): 25.01.94

### TANDEM AMORPHOUS SILICON SOLAR CELLS

J. Furlan, W. Kusian\*, G. Conte\*\*

Faculty of Electrical and Computer Engineering, Ljubljana, Slovenia

\*Siemens AG, Corporate Research and Development, Muenchen, Germany

\*\*ENEA, Centro Ricerche Fotovoltaiche, Portici-Napoli, Italy

#### **INVITED PAPER**

21<sup>st</sup> International Conference on Microelectronics, MIEL'93 29<sup>th</sup> Symposium on Devices and Materials, SD'93 September 29 - October 1, 1993, Bled, SLOVENIA

Key words: photovoltaic energy, solar cells, tandem cells, amorphous silicon, state of the art, conversion efficiency, stability, series tandem, parallel tandem, fabrication

Abstract - Recent progress in the field of amorphous silicon tandem solar cells is reviewed. The advantages of series connected tandem cells with regard to single junction amorphous solar cells are discussed. Partitioning a thicker cell into two or three thinner cells results in higher inherent built-in electric fields in the cells with better conversion efficiency and stability. A new approach is described, utilizing parallel connection of cells in tandem structure to additionally improve efficiency, stability and sensitivity to thickness tolerances. The essential similarities and differences between series and parallel tandem cell arrangements are discussed and the present status of tandem cells fabrication is presented.

### Tandemske amorfne silicijeve sončne celice

Ključne besede: energija fotonapetostna, celice sončne, celice tandemske, silicij amorfni, stanje razvoja, izkoristek konverzijski, stabilnost, tandem serijski, tandem paralelni, izdelava

Povzetek: Prikazani so dosežki s področja amorfnih silicijevih tandemskih celic. Opisane so prednosti serijskih tandemskih celic proti eni sami amorfni silicijevi sončni celici. Razdelitev debelejše celice v dve ali tri tanjše vodi do večjih vgrajenih električnih polj v posameznih celicah in k boljšim izkoristkom pretvorbe in večji stabilnosti delovanja. Opisan je novi pristop z vzporedno vezavo posameznih celic, pri kateri je pričakovati dodatno izboljšanje izkoristka, stabilnosti in neobčutljivosti na tolerance debelin celic. Prikazane so glavne podobnosti in razlike med serijsko in paralelno vezavo ter trenutno stanje tehnologije izdelave tandemskih celic.

#### INTRODUCTION

The majority of photovoltaic energy conversion devices on the market today are silicon solar cells, including most efficient but expensive single crystalline devices, less expensive recrystallized metallurgical silicon devices, as well as low cost thin film solar cells from amorphous silicon which received a great attention during the last decade as one of the most prospective materials for low cost solar cells.

Amorphous silicon (a-Si) can be inexpensively deposited on large substrates of various materials and shapes. During its deposition it needs to be treated to relatively low temperatures in the range of 200-300°C. Due to high light absorption of a-Si, the a-Si solar cell thickness can be very small, typically less than 1μm.

The main limitation in obtaining high solar cell conversion efficiency are poor transport properties of charge carriers in amorphous silicon. The photogenerated electrons and holes which make up the collected solar cell photocurrent have very short diffusion lengths which are much too short to provide effective collection of these

carriers. Therefore, the a-Si cell has to be very thin and an aiding electric field is built inside of the cell to assist more effective charge separation and collection. On the other hand, the cell should be sufficiently thick in order to provide a suitable absorption of light flux. These opposing criteria directed to the idea of tandem a-Si solar cell structures where the individual cells are deposited sequentially forming a multilayer solar cell structure in which the unit cells are optically and electrically connected in series /1/. Since the collected photocurrent must be the same in all unit cells, each consecutive cell in a series tandem structure must be thicker than the preceding one.

A parallel connected tandem a-Si cell structure in which the individual cells are optically connected in series and electrically in parallel has been proposed recently /2/. This configuration which is presently under intensive investigations is hoped to outperform its series tandem counterpart with respect to conversion efficiency and stability promising also lower sensitivity of solar cell efficiency on nonuniform a-Si deposition rate in large area solar cell modules /3/.

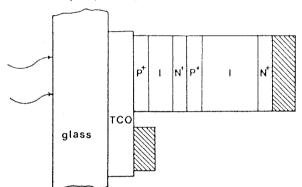

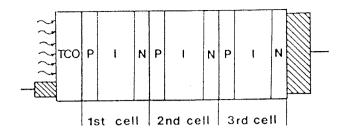

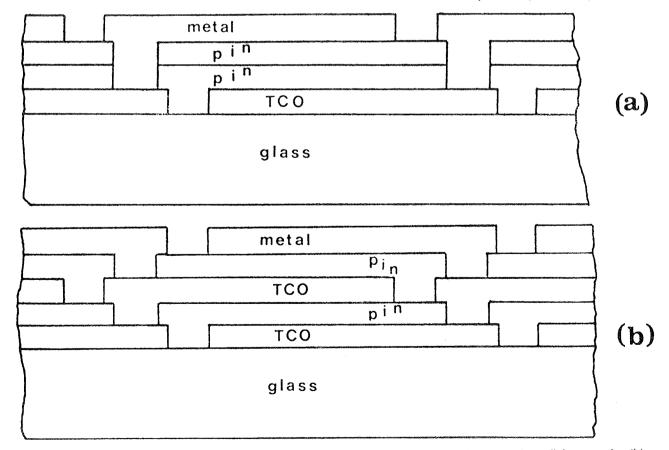

#### SERIES TANDEM CELL STRUCTURE

In series tandem structures two or three cells are optically and electrically connected in series, as shown in Fig. 1 /1/. The front p<sup>+</sup>in<sup>+</sup> cell is covered by a transparent conductive oxide (TCO) layer providing electric contact to the p<sup>+</sup> layer of this cell. The metal on n<sup>+</sup> layer is serving for electric contact to the back p<sup>+</sup>in<sup>+</sup> cell. Junctions n<sup>+</sup>p<sup>+</sup> interfacing consecutive unit cells are acting as ohmic contacts, electrically interconnecting succeeding p<sup>+</sup>in<sup>+</sup> cells.

The individual cells in such serially stacked devices can use the same amorphous material in all unit cells. Such structure which affords a sufficient absorption of photon flux and enables a satisfactory collection of photogenerated carriers is regarded as one of the most practical solutions. The fact that the electric current in a series connected tandem cell is the same in all unit cells demands a greater thickness of each consecutive cell. Consequently, a practical stacked a-Si cell structure consists of only two cells. Atriple tandem structure would require an unacceptably thin front and thick back unit cell. Most frequently these double stacked cells are fabricated by depositing thin layers of TCO, amorphous

Fig. 1: The basic series tandem structure.

silicon and metal on a glass substrate, as shown schematically in Fig. 2. The p<sup>+</sup> and n<sup>+</sup> layers are indispensable for creating the built-in electric field in i-layers assisting charge carrier separation and collection. Since the diffusion lengths in highly doped a-Si are extremely short, these dead layers must be very thin, usually in the range between 15 and 30nm.

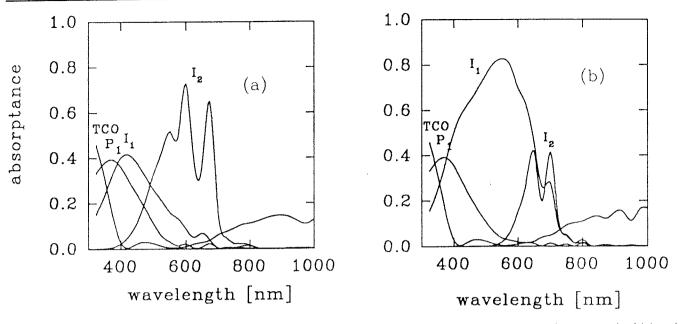

Even a very thin p<sup>+</sup> layer of the front cell parasitically absorbs a large amount of photons at short wavelenghts. For this reason the energy gap of the front p+ layer is increased to about 2eV by mixing amorphous silicon with carbon, resulting in a sort of optical window. In spite of a wider band-gap a relatively large part of light flux is absorbed in this so-called p<sup>+</sup> window layer, as shown in Figs. 3.a and b, representing the calculated portions of the absorbed sunlight flux in specific layers of a double stacked tandem cell for two sets of solar cell thicknesses, given in Table I. It can be noticed from these plots that the absorbed fluxes in i-layers of both cells are matched when the top cell is much thinner than the bottom cell.

Fig. 2: Schematic presentation of double-stacked a-Si/a-Si series tandem solar cell.

The absorbed photons in both i-layers generate electrons and holes which are collected at opposite electrodes. The effectiveness of this charge collection greatly depends on the density of localized states in the gap of a-Si. Higher is the density of states in the i-layer, greater is the decrease of the built-in electric field and higher are thermal recombinations of photogenerated carriers, resulting in a decreased collection efficiency. The so-called Staebler-Wronski effect (SW effect), which originates from increased states density in the gap during a strong illumination, is the main cause of unstable operation of a-Si cells. When decreasing the thicknesses of individual cells in a-Si tandem structures, the built-in electric field in i-layers increases, and the solar cell degradation due to SW effect is reduced.

Table I Thicknesses of thin layers selected for calculation of absorptance

|                                                |          | Thickness (nm) |

|------------------------------------------------|----------|----------------|

| layer(s)                                       | case (a) | case (b)       |

| TCO                                            | 200      | 200            |

| P <sub>1</sub>                                 | 15       | 15             |

| I <sub>1</sub>                                 | 30       | 470            |

| N <sub>1</sub>                                 | 15       | 15             |

| P <sub>1</sub> /I <sub>1</sub> /N <sub>1</sub> | 60       | 500            |

| P <sub>2</sub>                                 | 15       | 15             |

| 12                                             | 370      | 570            |

| N <sub>2</sub>                                 | 15       | 15             |

| P <sub>2</sub> /I <sub>2</sub> /N <sub>2</sub> | 400      | 600            |

The initial efficiency of double stacked a-Si/a-Si cells has been obtained around 11% /4/. However, after light induced degradation the stabilized efficiencies of 8% were obtained in large area modules.

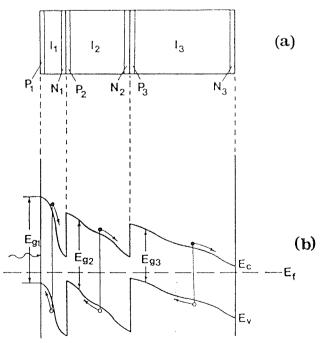

The second kind of series tandem cell structure consists of two or three p<sup>+</sup>in<sup>+</sup> amorphous cells having different band-gaps. This so-called multi-gap amorphous solar cell uses the principle of spectral splitting. As shown in Fig. 4, the incident light enters the first cell made from a wide band-gap material, absorbing only the blue portion

Fig. 3: Absorptance of sunlight in various layers of a double-stacked a-Si/a-Si solar cell in cases of an unmatched (a) and a matched (b) structure.

of the solar spectrum and producing inherently high open-circuit voltage. Higher wavelength light passes through the first cell without being absorbed and generates charge carriers in amorphous material of the second cell having smaller band-gap. The rest of the long wavelength flux which passes also the second cell is finally absorbed in the third cell made from the smallest band-gap material. Atypical three cell configuration uses amorphous silicon-carbon, amorphous silicon, and amorphous silicon-germanium as semiconductor materials in such tandem configuration. As in case of double stacked a-Si/a-Si tandem structure the photogenerated currents in all cells in series must be equal, so that the thicknesses of individual cells are tailored with regard to their light absorption properties and carrier collection capabilities.

Fig. 4: Multi-gap stacked solar cell structure (a) with its band-gap representation (b).

Triple cell modules have been fabricated with initial conversion efficiencies between 10 and 11%, which degraded for less than 20% after extended light soaking /5/.

#### PARALLEL TANDEM CELL STRUCTURE

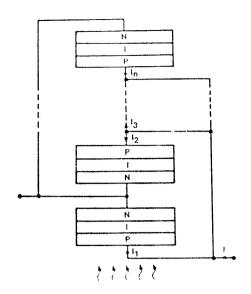

A new a-Si tandem solar cell structure has been proposed recently in which individual cells are optically connected in series and electrically in parallel /2/. This structure, shown schematically in Fig. 5, consists of two or more a-Si cells stacked in the sequence pin-nip-pin...etc. At each interface between consecutive cells the electric contact to both joining cells is provided by a thin transparent conductive layer.

In contrast with series tandem structure in which the current passing all unit cells is the same, the parallel tandem arrangement requires equal photovoltages in all cells. This voltage, being in the vicinity of the open-circuit voltage, does not vary strongly with different light generated and collected charge carrier densities. This is because the voltage at the maximum cell collection efficiency markedly depends on strongly varying dark current and much less on gradually changing photocurrent component. This suggests that all unit cells in a parallel tandem arrangement must have equal dark characteristics, demanding the same amorphous semiconductor for all unit cells.

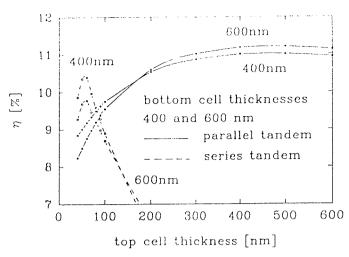

Intensive studies and experiments are currently carried on in fabricating a double stacked parallel tandem structure, and computer simulation of parallel tandem cell has also been initiated /3/. Computer modelling of a-Si tandem cells has indicated that the expected sensitivity of a parallel tandem arrangement on the thickness variations of individual cells is much lower than in case of senes tandem structure. As an example, Fig. 6 shows

Fig. 5: Parallel tandem a-Si cell connection.

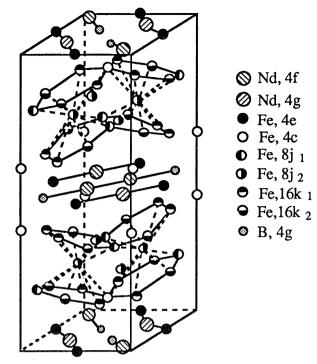

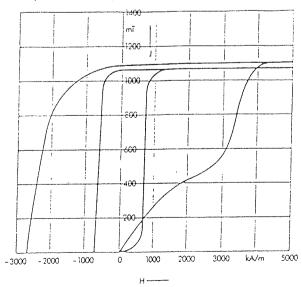

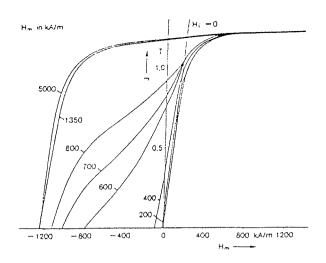

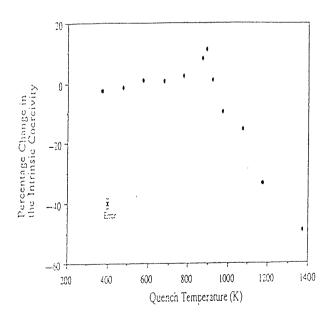

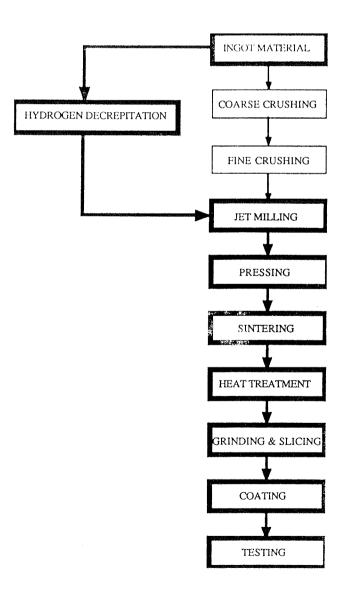

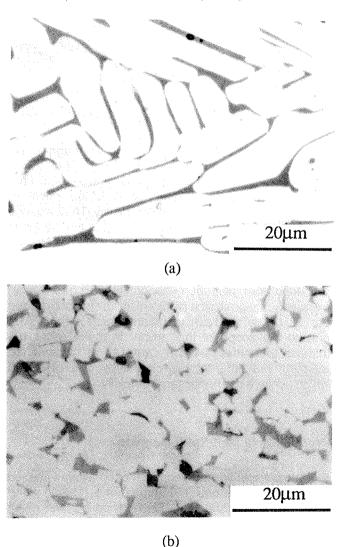

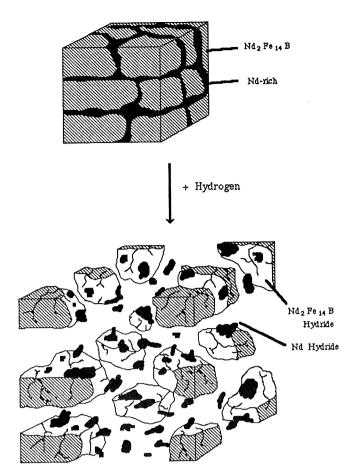

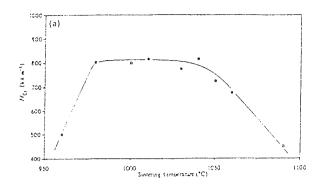

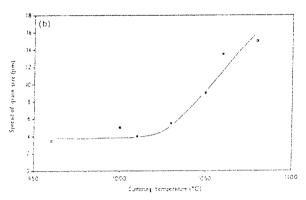

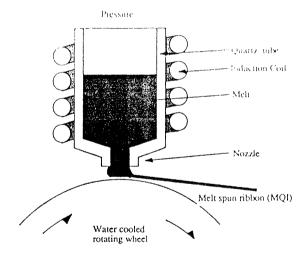

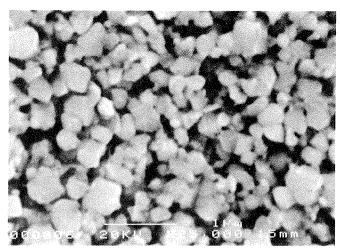

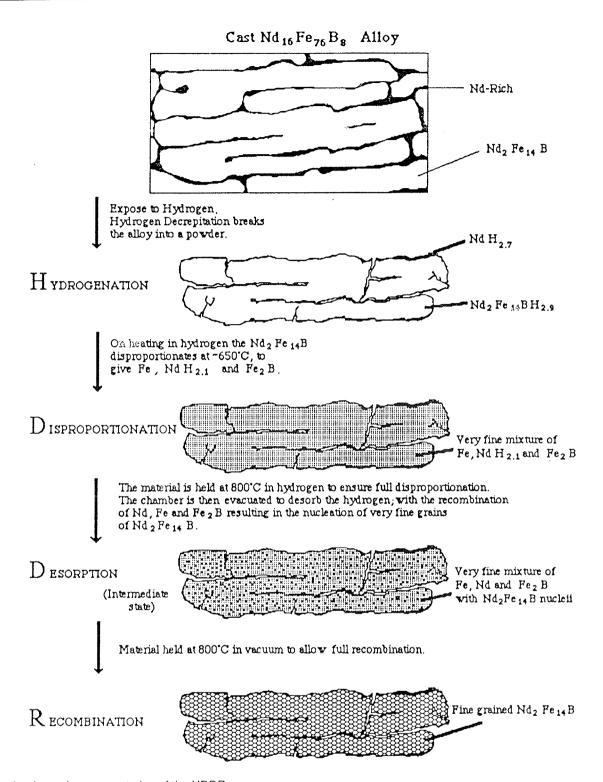

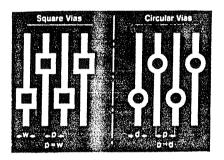

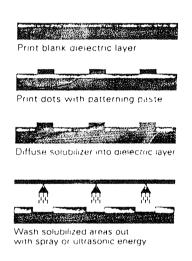

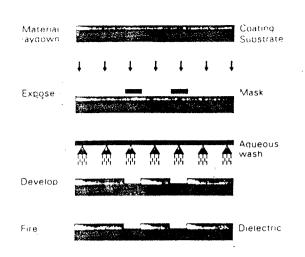

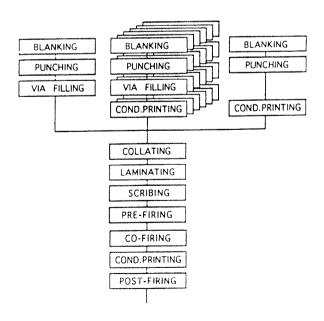

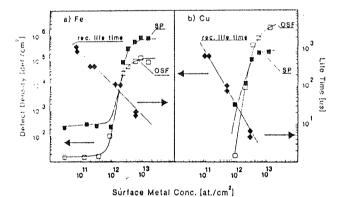

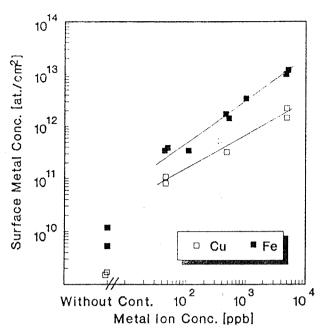

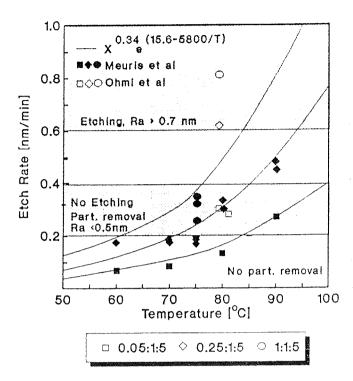

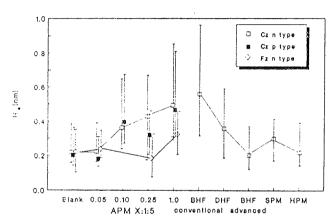

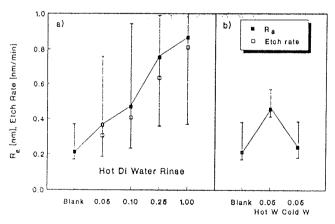

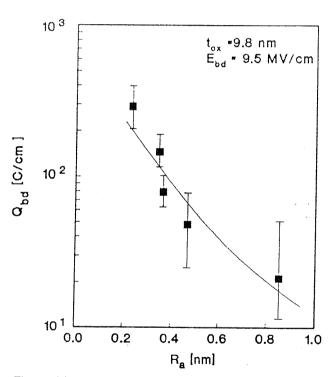

the computed conversion efficiency of parallel and series tandem cells having a fixed bottom cell thickness and a varying top cell thickness. It can be noticed that in contrast with series tandem cell the thickness of the front cell in parallel connection can vary broadly not affecting strongly the conversion efficiency. Since the thickness of unit cells in parallel tandem connection is not critical it can be expected that this tandem arrangement will outperform the series tandem structure by having a smaller decrease of conversion efficiency due to nonuniform a-Si deposition rate in large area solar cell mo-