## Informacije

MIDEM

Journal of Microelectronics, Electronic Components and Materials **Vol. 50, No. 4(2020), December 2020**

Revija za mikroelektroniko, elektronske sestavne dele in materiale **letnik 50, številka 4(2020), December 2020**

## Informacije MIDEM 4-2020 Journal of Microelectronics, Electronic Components and Materials

#### VOLUME 50, NO. 4(176), LJUBLJANA, DECEMBER 2020 | LETNIK 50, NO. 4(176), LJUBLJANA, DECEMBER 2020

Published quarterly (March, June, September, December) by Society for Microelectronics, Electronic Components and Materials - MIDEM. Copyright © 2020. All rights reserved. | Revija izhaja trimesečno (marec, junij, september, december). Izdaja Strokovno društvo za mikroelektroniko, elektronske sestavne dele in materiale – Društvo MIDEM. Copyright © 2020. Vse pravice pridržane.

#### Editor in Chief | Glavni in odgovorni urednik

Marko Topič, University of Ljubljana (UL), Faculty of Electrical Engineering, Slovenia

#### Editor of Electronic Edition | Urednik elektronske izdaje

Kristijan Brecl, UL, Faculty of Electrical Engineering, Slovenia

#### Associate Editors | Odgovorni področni uredniki

Vanja Ambrožič, UL, Faculty of Electrical Engineering, Slovenia Arpad Bürmen, UL, Faculty of Electrical Engineering, Slovenia Danjela Kuščer Hrovatin, Jožef Stefan Institute, Slovenia Matija Pirc, UL, Faculty of Electrical Engineering, Slovenia Franc Smole, UL, Faculty of Electrical Engineering, Slovenia Matjaž Vidmar, UL, Faculty of Electrical Engineering, Slovenia

#### Editorial Board | Uredniški odbor

Mohamed Akil, ESIEE PARIS, France Giuseppe Buja, University of Padova, Italy Gian-Franco Dalla Betta, University of Trento, Italy Martyn Fice, University College London, United Kingdom Ciprian Iliescu, Institute of Bioengineering and Nanotechnology, A\*STAR, Singapore Marc Lethiecq, University of Tours, France Teresa Orlowska-Kowalska, Wroclaw University of Technology, Poland Luca Palmieri, University of Padova, Italy Goran Stojanović, University of Novi Sad, Serbia

#### International Advisory Board | Časopisni svet

Janez Tronteli, UL, Faculty of Electrical Engineering, Slovenia - Chairman Cor Claeys, IMEC, Leuven, Belgium Denis Đonlagić, University of Maribor, Faculty of Elec. Eng. and Computer Science, Slovenia Zvonko Fazarinc, CIS, Stanford University, Stanford, USA Leszek J. Golonka, Technical University Wroclaw, Wroclaw, Poland Jean-Marie Haussonne, EIC-LUŚAC, Octeville, France Barbara Malič, Jožef Stefan Institute, Slovenia Miran Mozetič, Jožef Stefan Institute, Slovenia Stane Pejovnik, UL, Faculty of Chemistry and Chemical Technology, Slovenia Giorgio Pignatel, University of Perugia, Italy Giovanni Soncini, University of Trento, Trento, Italy Iztok Šorli, MIKROIKS d.o.o., Ljubljana, Slovenia Hong Wang, Xi'an Jiaotong University, China

#### Headquarters | Naslov uredništva

Uredništvo Informacije MIDEM MIDEM pri MIKROIKS Stegne 11, 1521 Ljubljana, Slovenia T. +386 (0)1 513 37 68 F. + 386 (0)1 513 37 71 E. info@midem-drustvo.si www.midem-drustvo.si

Annual subscription rate is 160 EUR, separate issue is 40 EUR. MIDEM members and Society sponsors receive current issues for free. Scientific Council for Technical Sciences of Slovenian Research Agency has recognized Informacije MIDEM as scientific Journal for microelectronics, electronic components and materials. Publishing of the Journal is cofinanced by Slovenian Research Agency and by Society sponsors. Scientific and professional papers published in the journal are indexed and abstracted in COBISS and INSPEC databases. The Journal is indexed by ISI® for Sci Search®, Research Alert® and Material Science Citation Index™. |

Letna naročnina je 160 EUR, cena posamezne številke pa 40 EUR. Člani in sponzorji MIDEM prejemajo posamezne številke brezplačno. Znanstveni svet za tehnične vede je

podal pozitivno mnenje o reviji kot znanstveno-strokovni reviji za mikroelektroniko, elektronske sestavne dele in materiale. Izdajo revije sofinancirajo ARRS in sponzorji društva. Znanstveno-strokovne prispevke objavljene v Informacijah MIDEM zajemamo v podatkovne baze COBISS in INSPEC. Prispevke iz revije zajema ISI® v naslednje svoje produkte: Sci Search®, Research Alert® in Materials Science Citation Index™.

## Content | Vsebina

| Original scientific papers                                                                                                                                                                                            |     | Izvirni znanstveni članki                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I. Mamatov, Y. Özçelep, F. Kaçar:<br>Voltage Differencing Transconductance Amplifier<br>based Ultra-Low Power, Universal Filters and<br>Oscillators using 32 nm Carbon Nanotube<br>Field Effect Transistor Technology | 233 | I. Mamatov, Y. Özçelep, F. Kaçar:<br>Univerzalni filtri in oscilatorji na osnovi napetostnega<br>transkonduktančnega ojačevalnika v tehnologiji 32 nm<br>poljskega tranzistorja z ogljikovimi nanocevkami |

| E. Erdem, A. M. Garipcan:<br>Hardware Implementation of Chaotic Zigzag Map<br>Based Bitwise Dynamical Pseudo Random Number<br>Generator on Field-Programmable Gate Array                                              | 243 | E. Erdem, A. M. Garipcan:<br>Strojna implementacija bitnega dinamičnega<br>psevdo-random generatorja števil v FPGA na<br>osnovi kaotične zigzag karte                                                     |

| L. F. Rahman, L. Alam, M. Marufuzzaman:<br>Design of a Low Power and High-Efficiency Charge<br>Pump Circuit for RFID Transponder EEPROM                                                                               | 255 | L. F. Rahman, L. Alam, M. Marufuzzaman:<br>Zasnova vezja črpalke naboja z majhno močjo in<br>visoko učinkovitostjo za RFID transponder EEPROM                                                             |

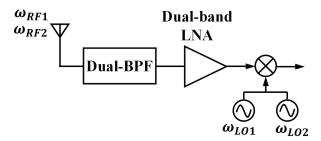

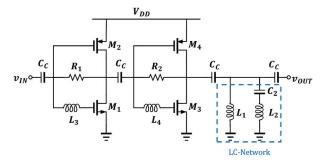

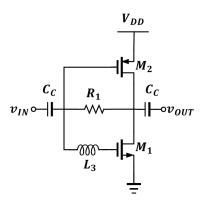

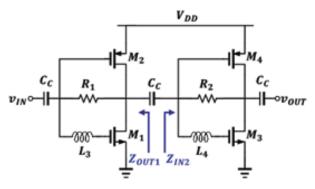

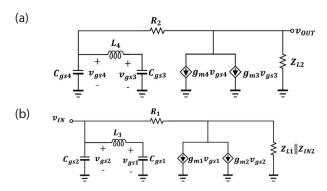

| A. Bijari, H. Khosravi, M. Ebrahimipour:<br>A Concurrent Dual-Band Inverter-Based Low Noise<br>Amplifier (LNA) for WLAN Applications                                                                                  | 263 | A. Bijari, H. Khosravi, M. Ebrahimipour:<br>Sočasni dvopasovni ojačevalnik z nizkim šumom<br>(LNA) za aplikacije WLAN                                                                                     |

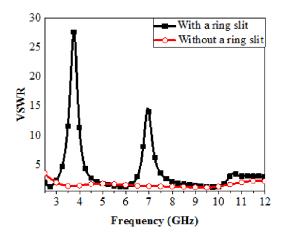

| A. Chaabane, O. Mahri, D. Aissaoui, N. Guebgoub:<br>Multiband Stepped Antenna for Wireless<br>Communication Applications                                                                                              | 275 | A. Chaabane, O. Mahri, D. Aissaoui, N. Guebgoub:<br>Večpasovna stopničasta antena za brezžične<br>komunikacijske aplikacije                                                                               |

| K. Palanichamy, P. Poornachari, G. Madhan M:<br>Performance Analysis of Dispersion Compensation<br>Schemes with Delay Line Filter                                                                                     | 285 | K. Palanichamy, P. Poornachari, G. Madhan M:<br>Analiza učinkovitosti disperzijskih kompenzacijskih<br>načrtov z linijskim kasnilnim sitom                                                                |

| Slovene Science Awards 2020                                                                                                                                                                                           | 293 | Najvišje nagrade v slovenski znanosti v letu 2020                                                                                                                                                         |

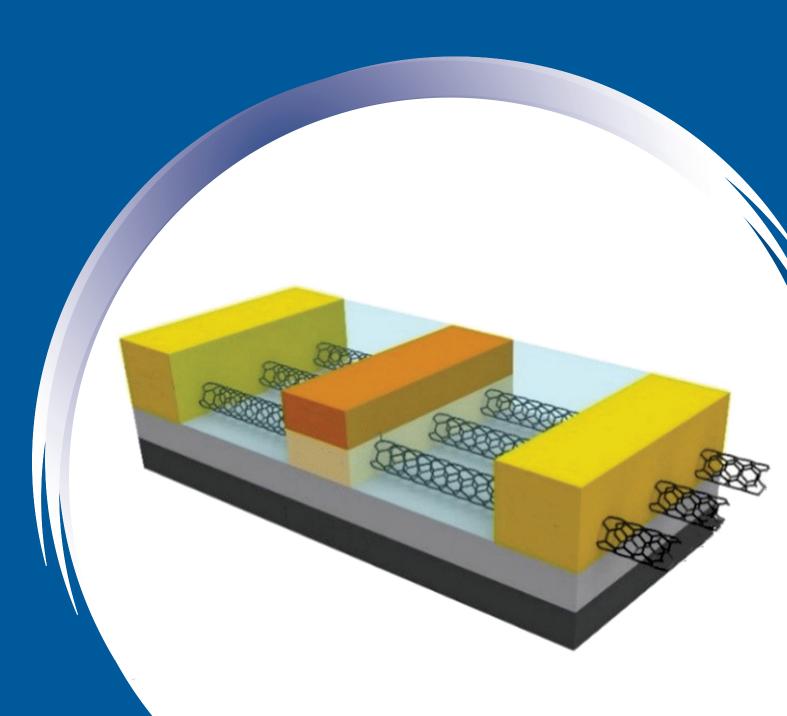

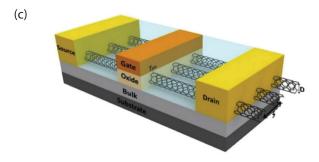

| Front page:<br>3-D view of typical TG CNTFET<br>(I. Mamatov et al.)                                                                                                                                                   |     | Naslovnica:<br>3-D pogled na tipičen TG CNTFET<br>(I. Mamatov et al.)                                                                                                                                     |

| 1 | 2 | 1 |

|---|---|---|

| / | 5 | / |

| _ | _ | _ |

https://doi.org/10.33180/InfMIDEM2020.401

Vol. 50, No. 4(2020), 233 - 241

## Voltage Differencing Transconductance Amplifier based Ultra-Low Power, Universal Filters and Oscillators using 32 nm Carbon Nanotube Field Effect Transistor Technology

Islombek Mamatov, Yasin Özçelep, Firat Kaçar

Istanbul University- Cerrahpasa, Department of Electrical and Electronics Engineering, Istanbul, Turkey

**Abstract:** Carbon nanotube field-effect transistor (CNTFET) is a strong candidate to replace existing silicon-based transistors. The ballistic transport of electrons in the CNTFET channel leads to ultra-low-power and high-frequency devices. Although a lot of digital applications of CNTFETs were presented, less work was done in analog applications of CNTFETs. This paper presents analog applications of CNTFET and its implementation of voltage differencing transconductance amplifier (VDTA). The CNTFET VDTA based filters and oscillators were proposed. The VDTA circuits are resistorless and can be tuned electronically only by changing transconductance. The proposed CNTFET VDTA shows power consumption of 4000 times less than compared to silicon CMOS technology and a significant reduction in chip area. All simulations were performed using SPICE and MATLAB simulation tools.

**Keywords:** Carbon Nanotube (CNT); Carbon Nanotube Field Effect Transistors(CNTFET); Voltage differencing Transconductance Amplifiers (VDTA); MOSFETS

## Univerzalni filtri in oscilatorji na osnovi napetostnega transkonduktančnega ojačevalnika v tehnologiji 32 nm poljskega tranzistorja z ogljikovimi nanocevkami

**Izvleček:** Poljski transistor z ogljikovimi nanocevkami (CNTFET) je močen kandidat za zamenjavo obstoječih silicijevih tranzistorjev. Balističen prenos elektronov v CNTFET kanalu omogoča nizko porabo moči in visoke frekvence. Kljub številnim digitalnim aplikacijam CNTFETov, je na analognem področju zelo malo objav. Članek opisuje uporabo CNTFET v analognem vezju napetostno diferencialnega transkonduktančnega ojačevalnika (VDTA). Vezja so brez uporov in elektronsko nastavljiva s spreminjanjem transkonduktance. Predlagano vezje ima 4000 krat nižjo porabo moči kot ekvivalentna izvedba v silicijevi CMOS tehnologiji. Simulacije so izvedenev SPICE in MATLAB okolju.

**Ključne besede:** Ogljikove nanocevke (CNT); poljski transistor z ogljikovimi nanocevkami (CNTFET); napetostno diferencalni transkonduktančni ojačevalnik (VDTA); MOSFET

#### 1 Introduction

Silicon-based MOSFETs have already reached their limits in scaling. CNTFET, with its ultra-long mean free

path (MFP), looks to overcome the limitations of conventional silicon-based MOSFETs due to its unique electronic and mechanical properties. These properties come from their strong atom-to-atom bonds, ballistic or near ballistic transport, and quasi 1D features

<sup>\*</sup> Corresponding Author's e-mail: islombek90@gmail.com

of the CNT channel. Besides, by changing the chirality of the CNT its material properties can be changed from semiconducting to metallic. Many attempts at building CNTFET models have been reported in the literature [1-9].

Two major geometries are available for CNTFET design, which are planar and gate-all-around. Sanchez et al. have compared all available architectures and their performances [1]. Dokania et al. have proposed gateall-around (GAA) or also known as wrap gate, analytical SPICE model [2]. The gate capacitance and drain current in the channel should be accurately designed to predict the precise performance of CNTFETs. Ahmed et al. proposed a model of the gate capacitance in which CNTs are arranged arbitrarily, unlike other models in which CNTs are placed at a fixed distance [3]. The authors of [3] have reported a 3% error with numerical simulations. Ballistic or near ballistic transport models for the drain current are proposed in [4-9]. These models are SPICE compatible, which means that the model can be easily compiled and integrated with any other circuit. The model used in this paper is from the articles [8-9].

Nizamuddin et. al proposed CNTFET and CMOS-based three-stage, hybrid operational transconductance amplifiers (OTA) [7]. Marani et al. reported improvement in DC gain by 17%, 40% less power consumption, and a decrease in output resistance by 90% in comparison to CMOS OTA [7]. Low power mixed-mode active filter using 12 CNT and 2 capacitors was presented by Zanjani et al. [14]. Jooq et al. designed CNTFET based ring oscillators suitable for the internet of things (IoT) applications [17]. Low power CNTFET based RF oscillator is reported in [18]. Digital applications of CNTFET, such as adders and multipliers can be found in papers [19-21].

Most of the CNTFET studies are limited to simulations only since commercially CNTFETs are not available. Mindy et al. have proposed a method for the production of CNTFETS in commercial silicon manufacturing facilities and reported experimental measurements of CNTFETs fabricated in two different manufacturing facilities [22]. Besides, the authors have improved the speed of the fabrication process 1100 times, by decreasing the deposition of CNT on the wafer from 48 hours to 150 seconds. Rebecca et al. have reported the first experimental data for CNTFET CMOS analog circuitry [23]. They have successfully fabricated 2 stages CTNFET CMOS op-amp with the channel length of 3 μm, which achieves the gain > 700. Thus, the basics of CNTFET technology is CMOS too. Even so, when we write CMOS, we refer to silicon-based CMOS in this paper.

The first Voltage differencing transconductance amplifier (VDTA) was introduced by D. Biolek as an

active element for analog signal processing[10]. However, any author did not perform the circuit implementation and application until the authors of proposed the realization of CMOS filters using VDTA [11]. The miniaturizations of electronic gadgets are becoming mainstream in today's technology. It will get harder and harder to integrate passive inductors into nano level circuits. VDTAs can be used to simulate inductors in signal processing circuits.

This work is organized as follows: Section 2 and 3 present the fundamentals of CNTFETSs and VDTAs respectively. The simulations' results and discussion of CNTFETVDTA including its comparison with CMOSVDTA are presented in section 4. In section 5,the application example of VDTA is presented. The universal filter realization is presented in section 5.1. The simulation results of CNTFET VDTA based oscillators are presented in section 5.2. Finally, in section 6 the conclusion of this paper is presented.

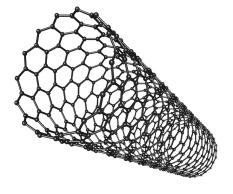

## 2 Carbon nanotube field-effect transistors fundamentals

Carbon nanotubes can be classified as single-walled and multi-walled. CNTFETs presented in this paper are made from single-walled CNTS as shown in Fig. 1. The chirality of CNT is the key parameter that determines whether a material is metal or semiconducting. There are two parameters of chirality, n and m (in some books or papers also referred to as n1 and n2). The values of these chirality parameters vary according to the rolling up method of CNT. The CNT is metallic if the difference of n and m is a multiple of 3. Otherwise, if the difference of n and m is not a multiple of 3 then the CNT is semiconducting [12-13]. The CNTFET presented in this paper is designed with semiconducting CNT.

Figure 1: Rolled up Graphene sheet (Carbon Nanotube).

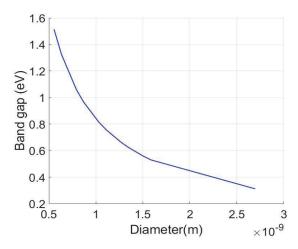

The bandgap is another key parameter which can be calculated from [12]:

$$E_G = \frac{2a_{cc}|t|}{2d} \approx \frac{0.8eV}{d} \tag{1}$$

Where, tight binging energy t is 3.0eV (also referred to as C-C bonding energy) and C-C bonding distance  $a_{cc}$  of the nearest neighbor is 1.42A°. Whereas, equations for CNT diameter CNTFET threshold are given as [13]-[14]:

$$D_{CNT} = \frac{\sqrt{n^2 + m^2 + mn}}{\pi} a \tag{2}$$

$$V_T \approx \frac{aV_{\pi}}{\sqrt{3}eD_{CNT}} \tag{3}$$

Here, *a* (C-C unit vector length) is 0.246 nm. From equations, it is obvious that both bandgap and threshold voltages are dependent on the diameter of CNT. The width of CNTFET can be calculated from the parameters like the number of tubes, the distance between tubes, and the diameter of CNT.

$$W = (N-1)S + D_{CNT} \tag{4}$$

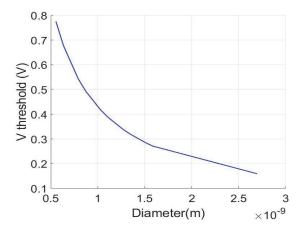

Numerical simulations of equations (1) and (3) were performed via MATLAB tool and the results are shown in Fig. 2 and Fig. 3. The exponential proportional dependency of CNT diameter for both bandgap and threshold voltage was observed. Both, threshold and band gap values increase as the CNT diameter value decreases.

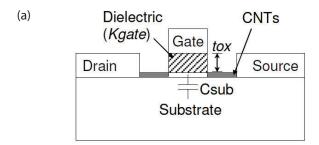

The CNTFET model used in this research is shown in Fig. 4 [8-9;14]. The CNTs are placed under the gate separated by high-k (high dielectric constant) material. The CNT extension regions between S/D and gate are heavily doped. Default parameter values provided by authors of the model [8-9;24] are shown in Table 1.

Figure 2: CNT Diameter vs V threshold.

Figure 3: CNT Diameter vs bandgap.

**Figure 4:** MSOFET-like CNTFET, a)1-D side view b) top view, c) 3-D view of typical TG CNTFET [8-9].

#### 3 VDTA

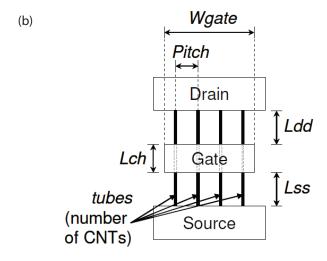

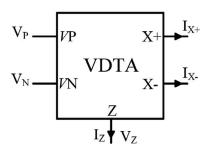

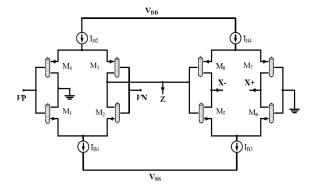

The proposed VDTA's circuit symbol and its circuit architecture at CNTFET level are shown in Fig. 5 and Fig. 6 respectively. The VDTA is an active element with high impedance input terminals  $V_{\rm p}$ ,  $V_{\rm N}$ , and high impedance output terminals Z, X+, and X-. The relationship between I/O terminals of an ideal VDTA can be expressed as follow [11]:

$$\begin{bmatrix} I_{Z} \\ I_{x+} \\ I_{x-} \end{bmatrix} = \begin{bmatrix} g_{m1} & -g_{m1} & 0 \\ 0 & 0 & g_{m2} \\ 0 & 0 & -g_{m2} \end{bmatrix} \begin{bmatrix} V_{VP} \\ V_{VN} \\ V_{VZ} \end{bmatrix}$$

(5)

Figure 5: The Circuit Symbol of VDTA.

**Figure 6:** CNTFET implementation of VDTA.

Where  $g_{m1}$  is the transconductance of the first stage and  $g_{m2}$  is the transconductance of the second stage. The voltage difference at the input terminals P and N transforms into output currents at terminal Z by  $g_{m1}$ . Then the voltage at the terminal Z is converted to output currents by  $g_{m2}$  at the output terminals x+ and x- [15]. VDTA can be tuned electronically by adjusting the values of  $g_m$  of the first stage or second stage.

#### 4 Simulations, results, and Discussions

All simulations were performed using HSPICE software. The parameters of CNT transistors used to get DC

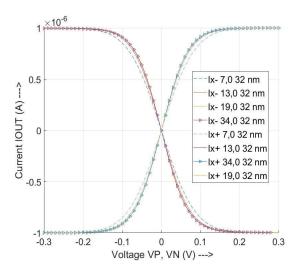

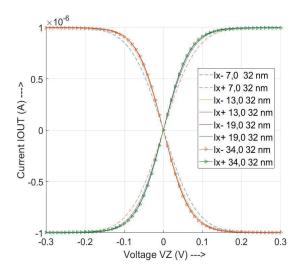

and AC characteristics of CNTFET VDTA are shown in Table 2. Supply voltages are fixed to  $V_{DD} = -V_{SS} = 0.3V$ and biasing currents are –considered as  $I_{B1} = I_{B2} = I_{B3} =$ 1μA. DC varying between -0.3V and 0.3V was applied first to the P and N terminals to measure the output current and to the Z terminal. Then DC changing between -0.3V and 0.3V was applied Z terminal of VDTA to measure output currents at terminals +X and -X. The results of DC transfer characteristics for ideal current sources are shown in Fig. 7 and Fig. 8 in two steps. As expected, the output current increases as the CNT diameter increases. Because the  $I_{op}$  of CNTFET increases as diameter increases due to an increase in carrier mobility and velocity [25]. For instance, in Fig. 7, the output current of CNTFET VDTA for 0.1V with CNT (7,0) is around 0,85μA, CNT (13,0) is around 0,89μA, CNT (19,0) and CNT (34,0) is 0,90 μA.

**Table 1:** Design parameters and definitions [24].

| Parameter | Definition                                                                   | Value   |

|-----------|------------------------------------------------------------------------------|---------|

| Lch       | Length of channel                                                            | 32nm    |

| Lss, Ldd  | The length of the doped CNT source/drain extension region.                   | 32nm    |

| Pitch     | The distance between the centers of two adjacent CNTs within the same device | 20nm    |

| Dcnt      | The diameter of Carbon<br>Nanotubes                                          | 1.5nm   |

| Tox       | The thickness of the high-k top gate dielectric material                     | 4nm     |

| Parameter | Definition                                                                   | Value   |

| Kox       | The dielectric constant of a high-k gate oxide material.                     | 16      |

| Tubes     | The number of tubes in the device.                                           | 3       |

| (n1, n2)  | The chirality of tube                                                        | (19, 0) |

**Table 2:** Transistor dimension of Proposed CNFET VDTA FCS.

| Transistors | W(nm) | L(nm) | Chirality | <i>D<sub>CNT</sub></i> (nm) | Tubes |

|-------------|-------|-------|-----------|-----------------------------|-------|

| M1,M2,M5,M6 | 41.5  | 32    | 19,0      | 1.5                         | 3     |

| M3,M4,M7,M8 | 221.5 | 32    | 19,0      | 1.5                         | 12    |

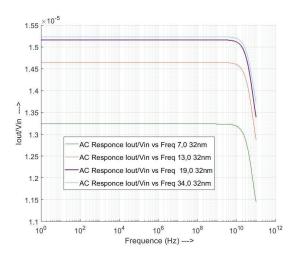

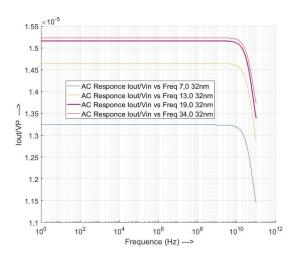

The AC response of CNTFET VDTA for different CNT parameters is shown in Fig. 9 and Fig. 10. The same supply voltage and bias currents as in the previous section were used. Similar to DC simulations, two-step simulation and measurement was done to get the AC response of VDTA. In the first step, the input AC voltage of 1V was applied at one of the input terminals P or N, and the gain at the output terminal Z was measured. In the second step, both input terminals were grounded and the input AC voltage of 1V was applied to the Z

**Figure 7:** DC Characteristcs of CNTFET VDTA. Step 1  $V_{in} = V_{p}$  and  $V_{N}$  vs  $I_{p}$ .

**Figure 8:** DC Characteristics of CNTFET VDTA. Step 2  $V_{in} = V_z \text{ vs } I_{x+} \text{ and } I_{x-}$ .

terminal. The output gain was measured from the X+ terminal. Both steps of DC/AC simulations show the same results which prove that CNTFET VDTA is operating properly.

Table 3: Comparison of CNFET and CMOS technologies.

| VDTA Structure | Supply voltage | Biasing current | Power<br>consumption | Transistor<br>dimension<br>N-type<br>(channel WxL) | Transistor<br>dimension<br>P-type<br>(channel WxL) |

|----------------|----------------|-----------------|----------------------|----------------------------------------------------|----------------------------------------------------|

| CMOS<br>18µm   | ±0.3           | 1mA             | 12mW                 | 1.296 μm²                                          | 5.99904 μm <sup>2</sup>                            |

| CMOS<br>32nm   | ±0.3           | 400 μΑ          | 4.8mW                | 0,00132 μm²                                        | 0,00708 μm <sup>2</sup>                            |

| CNTFET<br>32nm | ±0.3           | 1μΑ             | 1.2 μW               | 0,00132 μm²                                        | 0,00708 μm <sup>2</sup>                            |

Comparison of CMOS 0.18um, CMOS 32nm node technology VDTA, and CNFET 32 nm technology VDTA is shown in Table 3. All three architecture is designed to meet the same frequency response ( $f_c \approx 3.5$  GHz). For the case of CMOS 32 nm VDTA, the DC characteristics degrade a little bit, the maximum output current does not reach the supplied ideal current source. Where CMOS 0.18 µm maximum current reaches and CNTFET VDTA maximum current reaches. Besides, even if the same dimensions (channel WxL) as for CNTFET VDTA are used for CMOS 32nm VDTA, the biasing current of 400µA is needed for CMOS 32nm technology to meet the same frequency response of CNTFET.

As we can see from graphs in DC simulations (Fig. 7-8) there is no much difference between CNT (7,0), (13,0), (19,0), and (34,0). However, the  $V_{\rm th}$  of (7,0) is much higher compared to (34,0).In AC simulations of VDTA (Fig. 9-10), we can observe a significant increase in gain with the change of CNT chirality from (7,0) to (19,0). Between (19,0) and (34,0) there is no much difference in gain but the diameter changes from 1.5 nm to 2.6 nm which will drastically increase the transistor dimension as well. Hence, we have selected CNT (19,0) for our further simulations. Another reason for selecting CNT (19,0) is to compare our simulation results with other references. Because all other works also used (19,0) CNT, including the authors of the original model from [24].

**Figure 9:** AC Characteristics of CNTFET VDTA. Step1  $V_{in} = V_p \text{ vs } I_y/V_p$ .

#### 5 Application example

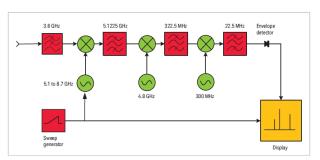

VDTA has a wide range of applications in the analog signal processing field. One of them is a spectrum analyzer shown in Fig. 11. This spectrum analyzer uses low pass filters, bandpass filters, local oscillators, and mixers to get the final intermediate frequency (IF).

**Figure 10:** AC Characteristics of CNTFET VDTA. Step2  $V_{in} = V_z \text{ vs } I_{x+}/V_z$ .

As an application example, this paper presents four filters and three local oscillators used in the spectrum analyzer.

Figure 11: Spectrum analyzers [16].

#### 5.1 Filters

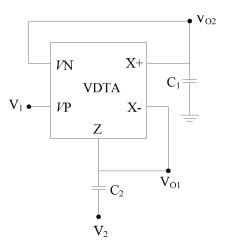

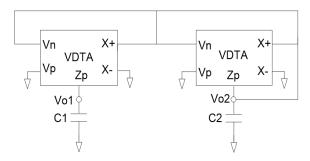

VDTA can be categorized as voltage mode and current mode. This paper presents voltage mode CNTFET VDTA. The realization of CNTFET voltage mode VDTA derived from ref [11] is shown in Fig. 6. Further, the universal filter topology of CNTFET VDTA is proposed as shown in Fig. 12. The presented CNTFET VDTA filter can operate as LP and BP filter.

The transfer function of the filter is as follow: If  $V_1 = V_{IN}$  then

$$BP \to \frac{V_{O1}}{V_{IN}} = \frac{sC_1g_{m1}}{s^2C_1C_2 + sC_1g_{m2} + g_{m1}g_{m2}}$$

(6)

$$LP \to \frac{V_{O2}}{V_{IN}} = \frac{g_{m1}g_{m2}}{s^2C_1C_2 + sC_1g_{m2} + g_{m1}g_{m2}} \tag{7}$$

And the expressions for Quality factor and natural frequency are given below:

Figure 12: Application of proposed CNTFET VDTA filter.

$$w = \sqrt{\frac{g_{m1}g_{m2}}{C_1C_2}} \tag{8}$$

$$Q = \sqrt{\frac{C_2 g_{m1}}{C_1 g_{m2}}} \tag{9}$$

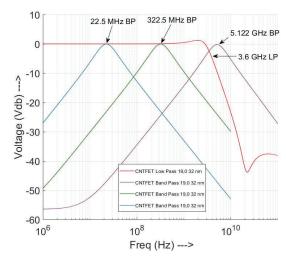

The filter blocks from Fig. 11 have been realized using proposed CNTFET VDTA from Fig.12 and the results are plotted in Fig. 13. The parameters of CNT transistors used for filter applications are shown in Table 2. The values of capacitors used for the filter application of CNTFET VDTA are shown in Table 4. The same supply voltage and bias currents as in the previous section were used. CNT (19,0) was selected for further applications of VDTA. There is no much difference between (7,0) and (19,0) CNT when the biasing current is set to  $1\mu$ A. As biasing current increases, the center frequency of filters also increases due to an increase in transconductance.

**Figure 13:** 3.6GHz LP, 5.122GHz BP, 22.5MHz BP and 322.5MHz BP filters.

**Table 4:** Capacitor values selected CNFET VDTA filters.

| Filters                     | C1                | C2                | Chirality n,m |

|-----------------------------|-------------------|-------------------|---------------|

| 3.6 GHz LP                  | 80.5fF            | 80.5fF            | 19,0          |

| 5.122 GHz BP                | 0.4334fF          | 0.4334fF          | 19,0          |

| 322.5 MHz BP<br>22.5 MHz BP | 74.5pF<br>10.72pF | 74.5pF<br>10.72pF | 19,0<br>19,0  |

#### 5.2 Oscillator

The oscillator is a DC to AC converter, which converts DC input signals to AC output signals such as sinusoidal waves. Local oscillators are used to change the frequency of the signal as in a spectrum analyzer from Fig. 11 and along with mixers, they improve the performance of receivers in electronic circuits. The circuit symbol of the CNTFET VDTA oscillator is shown in Fig. 14. The oscillator blocks from Fig. 11 have been realized using the proposed oscillator structure.

**Figure 14:** Application of proposed CNTFET VDTA quadrature oscillator.

The circuit analysis of the second-order characteristical equation can be represented as:

$$s^{2}C_{1}C_{2} + sC_{2}(g_{m3} - g_{m4}) + g_{m1}g_{m2} = 0$$

(10)

$$g_{m3} = g_{m4} \tag{11}$$

$$\omega_0 = \sqrt{\frac{g_{m1}g_{m2}}{C_1C_2}}$$

(12)

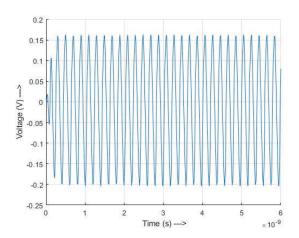

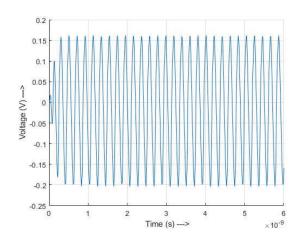

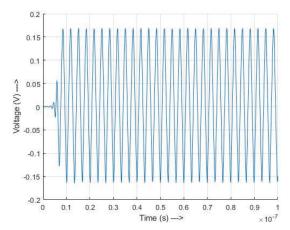

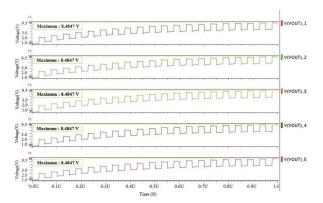

Where  $g_{\rm m3}=g_{\rm m4}$  is the condition for oscillation and wo is oscillation frequency. The parameters of CNT transistors used for oscillators applications are shown in Table 5. Supply voltages are fixed to  $V_{\rm DD}=-V_{\rm SS}=0.3{\rm V}$  and biasing currents are considered as  $I_{\rm B1}=I_{\rm B2}=I_{\rm B3}=1$  µA. The simulation results are plotted through Fig. 15-Fig. 17.

**Table 5:** Transistor dimension of proposed CNFET VDTA oscillator.

| Transistors | W(nm)  | L(nm) | Chirality | D <sub>CNT</sub> (nm) | Tubes |

|-------------|--------|-------|-----------|-----------------------|-------|

| M1,M2,M5,M6 | 221.5  | 32    | 19,0      | 1.5                   | 12    |

| M3,M4,M7,M8 | 1121.5 | 32    | 19,0      | 1.5                   | 57    |

**Figure 15:** 5.1 GHz VDTA Based Oscillator C1=C2 =0.068fF.

**Figure 16:** 4.8 GHz VDTA Based Oscillator C1=C2 =0.08fF.

#### 6 Conclusion

Ultra-low-power CNTFET based VDTA filters and oscillators were presented. As shown in Table 3. CNTFET 32 nm based VDTAs consume the power of 4000 times less than CMOS 32nm based VDTAs. Also, n-type CNTFETS occupy approximately 989 times less than space in the chip area (only considering effective channel WxL) compared to n-type MOSFET transistors while p-type CNTFETS occupy approximately 848 times less space(only considering effective channel WxL)

**Figure 17:** 300 MHz VDTA Based Oscillator C1=C2 = 3.9fF.

compared to p-type 0.18µm technology node MOSFETS used in typical VDTAs. Higher biasing current or capacitors may be adjusted to change the center frequency of CNTFET filters. CNTFET VDTA based filters and first-ever CNTFET VDTA based oscillators for spectrum analyzer are presented as an application example.

#### 7 Conflict of interest

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

#### 8 References

- A. Pacheco-Sanchez, F. Fuchs, S. Mothes, A. Zienert, J. Schuster, S. Gemming, and M.Claus, "Feasible Device Architectures for Ultrascaled CNTFETs", IEEE Transactions on Nanotechnology, vol. 17, no.1, 2018.

- https://doi.org/10.1109/TNANO.2017.2774605

- 2. V. Dokania, A. Islam, V. Dixit, and S. P. Tiwari, "Analytical Modeling of Wrap-Gate Carbon Nanotube FET With Parasitic Capacitances and Density of States", IEEE Transactions on Electron Devices, vol.63, no.8, 2016. https://doi.org/10.1109/TED.2016.2581119

- 3. Z. Ahmed, L. Zhang, and M. Chan, "Gate Capacitance Model for Aligned Carbon Nanotube FETs With Arbitrary CNT Spacing", IEEE Transactions on Electron Devices, vol.62, no.12, 2015. https://doi.org/10.1109/TED.2015.2484384

- 4. S. Farhana, A.H.M. Z. Alam, S. Khan, and S.M.A. Motakabber, "CNTFET SPICE Model: Design of a Carbon Nanotube Field Effect Transistor", 5th International Conference on Computer & Commu-

- nication Engineering, IEEE 2014. https://doi.org/10.1109/ICCCE.2014.81

- G. Gelao, R. Marani, R. Diana, and A. G. Perri, "A Semiempirical SPICE Model for n-Type Conventional CNTFETs", IEEE Transactions on Nanotechnology, vol. 10, no. 3, 2011. https://doi.org/10.1109/TNANO.2010.2049499

- A.Raychowdhury, S. Mukhopadhyay, and K. Roy, "A Circuit-Compatible Model of Ballistic Carbon Nanotube Field-Effect Transistors", IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol.23, no.10, 2004. <a href="https://doi.org/10.1109/TCAD.2004.835135">https://doi.org/10.1109/TCAD.2004.835135</a>

- M. Nizamuddin, S. A. Loan, S. A. Abbasi and A. R. M. Alamoud, "Design and Simulation of High Performance Carbon Nanotube based Three Stage Operational Amplifiers", AFM 2015. <a href="https://doi.org/10.1016/j.matpr.2016.01.041">https://doi.org/10.1016/j.matpr.2016.01.041</a>

- 8. J. Deng and H.-S. P. Wong, "A Compact SPICE Model for Carbon-Nanotube Field-Effect Transistors Including Nonidealities and Its Application—Part I: Model of the Intrinsic Channel Region", IEEE Transactions on Electron Devices, vol.54, no.12, 2007. <a href="https://doi.org/10.1109/TED.2007.909030">https://doi.org/10.1109/TED.2007.909030</a>

- J. Deng and H.-S. P. Wong, "A Compact SPICE Model for Carbon-Nanotube Field-Effect Transistors Including Nonidealities and Its Application— Part II: Full Device Model and Circuit Performance Benchmarking", IEEE Transactions on Electron Devices, vol.54, no.12, 2007. https://doi.org/10.1109/TED.2007.909043

- K. Roja, K. M. Santhoshini, S. Musala, and A.Srinivasulu, "Voltage Difference Transconductance Amplifier based Voltage Mode Band Pass Filter with constant Q-Factor", Electronics, Computers and Artificial Intelligence, 2018. https://doi.org/10.1109/ECAI.2018.8678979

- A.Yeşil, F. Kaçar, H. Kuntman, "New Simple CMOS Realization of Voltage Differencing Transconductance Amplifier and Its RF Filter Application", RadioEngineering, vol.20, no.3, 2011. https://www. radioeng.cz/fulltexts/2011/11\_03\_632\_637.pdf

- 12. J. Guo, "Carbon Nanotube Electronics: Modeling, Physics, And Applications", Purdue University, 2004.

- M. S. Dresselhaues, G. Dresselhaues, and R. Saito, "Physics of Carbon Nanotubes", Carbon, vol. 33, no.7, pp. 883-891, Elsevier Science Ltd, 1995 <a href="https://doi.org/10.1016/0008-6223(95)00017-8">https://doi.org/10.1016/0008-6223(95)00017-8</a>

- S. M. A. Zanjani, M. Dousti and M. Dolatshahi, "A CNTFET universal mixed-mode biquad active filter in subthreshold region", Int J. RF Microw. Comput. Aided Eng. 2018. https://doi.org/10.1002/mmce.21574

- W. Tangsrirat and S.Unhavanich, "Voltage differencing transconductance amplifier based floating simulators with a single grounden capacitor", Indian Journal of Pure & Applied Physics, 2014.

- 16. Keysight Technologies, "Spectrum analysis basics", application note 150, 2015.

- M. K. Q. Jooq, A. Mir, S. Mirzakuchaki, A. Farmani, "Design and performance analysis of wrap-gate CNTFET-based ring oscillators for IoT applications", Integration, the VLSI Journal 70, 2019. <a href="https://doi.org/10.1016/j.vlsi.2019.10.005">https://doi.org/10.1016/j.vlsi.2019.10.005</a>

- A. Taghavi, C. Carta, T. Meister, F. Ellinger, M. Claus and M. Schroter, "A CNTFET Oscillator at 461 MHz", IEEE Microwave and Wireless Components Letters, vol.27, no.6, 2017. https://doi.org/10.1109/LMWC.2017.2701312

- Z. D. Shalamzari, A.D. Zarandi and M. R. Reshadinezhad, "Newly multiplexer-based quaternary half-adder and multiplier using CNTFETs", Int. J. Electron. Commun., (AEÜ) 117 153128, 2020. https://doi.org/10.1016/j.aeue.2020.153128

- E. Shahrom and S. A. Hosseini "A new low power multiplexer based ternary multiplier using CNTFETs", Int.

J. Electron. Commun., (AEÜ) 93 191–207, (2018).

<a href="https://doi.org/10.1016/j.aeue.2018.06.011">https://doi.org/10.1016/j.aeue.2018.06.011</a>

- S. K. Sahoo, G. Akhilesh, R. Sahoo, and M. Muglikar, "High-Performance Ternary Adder Using CNTFET", IEEE Transactions on Nanotech., vol.16 no.3, 2017. <a href="https://doi.org/10.1109/TNANO.2017.2649548">https://doi.org/10.1109/TNANO.2017.2649548</a>

- M. D. Bishop, G. Hill, T. Srimani, C. Lau, D. Murphy, S. Fuller, J. Humes, A. Ratkovich, M. Nelson and M. M. Shulaker1, "Fabrication of carbon nanotube field-effect transistors in commercial silicon manufacturing facilities" Nature Electronics volume 3, pages 492–501 2020. https://doi.org/10.1038/s41928-020-0419-7

- R. Ho, C. Lau, G. Hills and M. M. Shulaker, "Carbon Nanotube CMOS Analog Circuitry", IEEE Transactions on nanotechnology, Vol. 18, 2019. https://doi.org/10.1109/TNANO.2019.2902739

- A Quick User Guide on Stanford University Carbon Nanotube Field Effect Transistors (CNFET) HSPICE Model V. 2.2.1.

- Lee C-S, Pop E, Franklin AD, Haensch W, Wong H-SP,"A compact virtual-source model for carbon nanotube FETs in the sub-10-nm regime—Part I: intrinsic elements", IEEE Trans Electron Devices,62(9):3061–9, 2015.

https://doi.org/10.1109/TED.2015.2457453

Copyright © 2020 by the Authors. This is an open access article distributed under the Creative Com-

mons Attribution (CC BY) License (https://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Arrived: 16. 07. 2020 Accepted: 13. 11. 2020

| 1 | 1 | 1 |

|---|---|---|

| / | 4 | / |

|   |   |   |

https://doi.org/10.33180/InfMIDEM2020.402

Vol. 50, No. 4(2020), 243 - 253

## Hardware Implementation of Chaotic Zigzag Map Based Bitwise Dynamical Pseudo Random Number Generator on Field-Programmable Gate Array

Ebubekir Erdem, Ali Murat Garipcan

Firat University, Computer Engineering Department, Elaziğ, Turkey

**Abstract:** In this study, successful real-time hardware implementation of discrete-time chaotic zigzag map as a random number generator (RNG) on field-programmable gate array (FPGA) environment is presented. For the hardware modelling of the application, ready-to-use modules defined on 32-bit floating-point numbers and hardware description language (VHDL) are used. In the study, the non-linear dynamic behaviour of the chaotic generator synthesized on the Altera Cyclone IV GX FPGA chip is examined in terms of critical cryptographic competences such as system reliability and statistical randomness quality. The random numbers with poor statistical quality in the system are obtained by passing 32-bit chaotic trajectory outputs through a simple comparison circuit. In order to improve the statistical sufficiency of these numbers, the H function post-processing technique is used. In addition, statistical verification and hardware performance analysis of the generator through NIST 800-22 tests and FPGA chip statistics are presented in the study. The obtained successful results show that the zigzag map can be used in different chaos-based engineering applications, including embedded cryptographic applications. In addition, the low area-energy requirement of PRNG in terms of modelling technique facilitates its practical applicability on resource-restricted applications and architectures.

**Keywords:** FPGA; pseudo-random number generator; chaotic zigzag map; H function

# Strojna implementacija bitnega dinamičnega psevdo-random generatorja števil v FPGA na osnovi kaotične zigzag karte

**Izvleček:** Članek predstavlja strojno implementacijo časovno disktretne kaotične zigzag karte kot generator naključnih števil v FPGA okolju. Za strojno modeliranje aplikacije je uporabljen VHDL skriptni jezik. V smislu kvalitete naključnosti in zanesljivost je raziskano nelinearno dinamično obnašanje kaotičnega generatorja na Altera Cyclone IV GX FPGA čipu. Naključna števila s slabo statistično kvaliteto so dobljena s posredovanjem 32-bitne kaotične trajektorije v enostavno primerjalno vezje. Za izboljšpanje njihove kvalitete je uporabljena tehnika post procesiranja s H funkcijo. Dodatno je statistična verifikacija preverjena z NIST 800-22 testi in statistiko FPGA čipa. Rezultati nakazujejo možnost uporabe zigzag kart v različnih kaotičnih aplikacijah vključno s kriptografijo.

Ključne besede: FPGA; pseudo naključen generator števil; kaotična zigzag karta; H funkcija

#### 1 Introduction

In addition to cryptography, randomness is a common statistical concept for many areas such as game theory, simulation, statistic, quantum mechanics, programming and entertainment. This common concept, unlike other fields, corresponds to randomly distributed bit-level random numbers acquired from a specific entropy source in cryptography are not reproducible and predictable. In cryptography, random numbers can be obtained from two different design classes, namely

<sup>\*</sup> Corresponding Author's e-mail: aberdem@firat.edu.tr

True Random Number Generators (TRNG) using physical noise sources and Pseudo Random Number Generators (PRNG) with deterministic structure. Although their output is unpredictable, TRNGs are susceptible to environmental changes and mostly offer hardware-dependent, slow and costly solutions [1-3].

Despite fulfilling an important cryptographic requirement such as unpredictability in terms of system security, statistical weakness is the most obvious deficiency of a physical TRNG. For PRNGs where random numbers with good statistical properties can be obtained at low cost, determinism and periodicity are the most important shortcomings of this design class. PRNGs are preferred due to their practical structure to obtain random numbers within cryptographic applications. However, due to the nature of determinism, the initial conditions and system parameters are decisive in the development of future states of PRNGs, unlike randomness. This case leading to predictability, limits the use of PRNGs for sensitive cryptographic applications. Furthermore, knowing the initial conditions (parameters) that contain all the entropy of the deterministic system, can completely remove the cryptographic confidentiality required for PRNGs [4-5].

Chaos theory is an important concept that has found application in many different disciplines such as biology, philosophy, meteorology, physics and sociology as well as different branches of engineering [4]. Chaos can be roughly defined as an irregular and unpredictable random behavior pattern observed in non-linear deterministic systems that are exponentially sensitive to initial conditions. The deterministic characteristic of chaotic systems is the most prominent feature distinguishing them from noise-based non-deterministic systems preferred for sensitive cryptographic applications. Due to their deterministic properties, the future states of chaotic systems can be predicted theoretically if the initial states are known exactly. However, in these systems characterized by a strong exponential dependence on the initial conditions, a very small error in the initial conditions due to the positive Lyapunov exponential can cause large deviations, also known as the butterfly effect, in the system trajectories evolving in time. Therefore, this divergent character can provide sufficient level of cryptographic secrecy by making the long-term estimation of dynamic system outputs in chaos state impossible [6-7].

Chaotic systems are divided into discrete and continuous time chaotic systems according to their mathematical modeling. In continuous chaotic systems, the evolution of the system is given by ordinary differential equations. It depends on the rate of change of the system's state variables. In discrete time, where

the evolution of the system depends on the values of state variables, chaotic systems are expressed by simple non-linear equations [3, 8]. For both chaotic system models, exponential sensitivity to the initial conditions and the ability to produce long-term non-periodic oscillations are the basic characteristics of these systems coinciding with the pattern of random behavior. These basic characteristics of chaos, which are similar to the confusion and diffusion properties, also known as Shannon principles, are used for different purposes in cryptography such as video [9], audio [10], image [11] encryption schemes, stream cipher [12], s-box design [13], post-processing techniques [14] and secure additional input [2]. Random number generation is another important use of chaos theory in cryptography. Chaotic systems can often be used as entropy source in hardware-based PRNG and TRNG designs, especially because they eliminate the need for difficult and complex processes, such as obtaining and processing noise signals based on physical randomness.

In practice, the prediction of the future state information of the chaotic system is limited by the measurement sensitivity of the initial state information. Whereas, the lack of infinite measurement sensitivity from the circuit nodes depending on the presence of electrical noise makes it almost impossible to accurately determine the initial conditions of the chaotic system for hardware implementations. Therefore, hardware modeled chaotic systems alone can provide the reliability (security) and unpredictability needed cryptographically, unlike a simple deterministic PRNG [8].

In the literature, there are different chaos-based PRNG and TRNG paradigms implemented with FPGA chips offering important facilities such as flexibility, ease of modelling, low power consumption, parallel processing and speed. Some of these studies can be summarized as follows: Özkaynak [7] proposed an easily applicable RNG model on FPGA chips, which could be an alternative to discrete time chaotic systems using the fractional order Chua system. Tuna et al. [15] modelled the autonomous Lü-Chen chaotic system on Xilinx Virtex-6 FPGA chip using the Heun numerical method and presented a high-speed chaotic oscillator design that can be used for embedded cryptographic applications. In another study, Tuna [16] presented a real-time implementation of a PRNG using an artificial neural network (ANN) based 2D chaotic oscillator on Xilinx Virtex 6 FPGA chip in four different scenarios. Koyuncu and Özcerit [17] modeled the continuous-time Sundarapandian - Pehlivan chaotic system using the Range-Kutta (RK4) numerical analysis method as RNG on the same FPGA chip. De la Fraga et al. [18] presented the hardware modeling of a PRNG based on four different discrete time chaotic system scenarios in their study

used Xilinx FPGA Spartan 3E FPGA chip. Koyuncu et al. [19] proposed the use of a new chaos-RO based dual entropy core TRNG architecture using the Xilinx Virtex-6 FPGA chip. A new three-dimensional continuous-time autonomous chaotic oscillator (P3DS) has been used as the deterministic component of TRNG. In another study, Meranza-Castillón et al. [20] provided the hardware implementation of a chaotic enhanced Hénon map (EHM) based PRNG that can be used for image and video ecryption systems on the Altera DE2-115 FPGA chip. Garcia Bosque et al. [21] presented a logistic map based PRNG implementation on Xilinx Virtex 7 chip in which chaotic system parameters change dynamically to prevent the system to fall into short period orbits as well as increasing the statistical randomness quality. Kanzadi et al. [22] proposed a double entropy sourced PRNG architecture on the Xilinx Spartan 3 FPGA chip, combining the tent and logistic map outputs with the exclusive-OR (XOR) gate. In [23], another logistic map based study Tuncer proposed physical unclonable functions based on ring oscillator (RO-PUF) and logistic map to generate pseudorandom numbers. The generator was implemented in Altera Cyclone II FPGA chip with VHDL language. Çiçek et al. [24] proposed a TRNG architecture using a discrete time double entropy resource to overcome the intrinsic limited entropy problem of conventional single entropy core architectures by using hardware redundancy.

In this study, hardware implementation and performance evaluation of an FPGA-based PRNG using chaotic zigzag map as entropy source is given. The statistical and spectral properties of the chaotic time series obtained from the implemented system are analyzed cryptographically. The NIST 800-22 randomness test is used for statistical verification of random numbers obtained from chaotic time series. The presented study is important in terms of demonstrating the applicability of the modeled chaotic system for different chaosbased cryptographic purposes such as secure communication, video and image encryption and s-box design in addition to random number generation. Furthermore, chaotic PRNG can be easily used in resourcerestricted architectures and cryptographic applications due to its low area-energy consumption.

The rest of the paper is organized as follows: In Chapter 2, theoretical details of the chaotic system are given. Details of the digital implementation of proposed PRNG on FPGA environment are presented in Chapter 3. In Chapters 4 the hardware performance and statistical success of chaos-based RNG have been analyzed cryptographically, respectively. The study is concluded by interpreting the results obtained in Chapter 5.

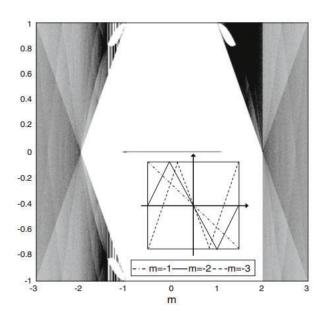

#### 2 Chaotic zigzag map

The discrete-time one-dimensional chaotic zigzag map whose mathematical definition is given in Eq. 1, is proposed by Nejati and Beirami in [5]. In Eq. 1, m is the state variable of the chaotic system and changes in the (- 3,3) closed interval. The zigzag map can display stable or chaotic behavior for different m values in the defined interval. The bifurcation diagram given in Fig. 1 can be used to identify the chaotic behavior of the system for these changes. In Fig. 1, for |m| < 1 values its behavior is stable, while for intervals  $m \in (2,1)$ , (1,2), [3,2) and (2,3] its behavior is chaotic. Especially for m  $\in$  [3,2) and (2,3] intervals, the  $x_n$  output values of the system in chaos state occur with a large irregularity in the [-1,1] interval. For the same intervals, the  $x_n$  output values of the chaotic system tend to infinity for large n values representing the iteration step. For |m| = 2, the map converges to 0 [5, 18].

$$x_{n+1} = \begin{cases} -m\left(x_n + \frac{2}{|m|}\right), & \text{for } x_n \in \left(-1, -\frac{1}{|m|}\right) \\ mx_n & \text{for } x_n \in \left(-\frac{1}{|m|}, \frac{1}{|m|}\right) \\ -m\left(x_n - \frac{2}{|m|}\right), & \text{for } x_n \in \left(\frac{1}{|m|}, 1\right) \end{cases}$$

(1)

In Eq. 1, the  $x_n$  output values oscillating in the [-1,1] interval for the zigzag map are 32-bit floating-point (real number) format. Eq. 2 is used to obtain one-bit random numbers from these 32-bit numbers in each iteration. In Eq. 2, the  $x_n$  output values normalized to the [0,1] interval, are compared with the threshold value and random bit sequences are attained.

$$b_{n+1} = \begin{cases} 1, & |x_n| > 0.5 \\ 0, & |x_n| < 0.5 \end{cases}$$

(2)

#### 3 Implementation details of FPGAbased real-time chaotic zigzag map

The chaotic system in accordance with the 32-bit IEEE 754 floating-point number standard is designed to be operated on FPGA chips. The Quartus Prime Lite Edition 17.1 design software and the Altera Cyclone IV EPC4GX150 FPGA chip are used together for synthesis and placement during the hardware implementation phase. In the chaotic system, Intel FPGA Intellectual Property (IP) cores library with ready-to-use circuit elements de-

Figure 1: Bifurcation diagram for zigzag map

fined on floating-point numbers is used for multiplication, division, addition, subtraction and comparison operations. In addition to this, all other definitions and circuit elements needed in the system are designed by VHDL dataflow and behavioral coding technique.

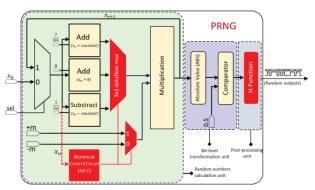

The top-level block representation of the PRNG created by schematic and dataflow design techniques is shown in Fig. 2. The operating logic of the system given in Fig. 2 can be briefly described as follows: In Fig. 2, 32-bit  $x_0$  and  $x_n$  values represent the seed and output values of the chaotic system, respectively. When the chaotic system starts to work, the seed value  $x_0$  is applied as input to the system and after a certain calculation time, the output value  $x_1$  is obtained. This case is the initial position for the chaotic system and the output of the system is constant at value  $x_1$ , in this position. In order to obtain random numbers from the chaotic system, starting from  $x_1$  value, the generated all  $x_n$  values should be applied as input to the system, respectively. This case is called the feedback position for the chaotic system.

**Figure 2:** Top-level schematic diagram of zigzag map based PRNG

The chaotic system generates random numbers dynamically, when in the feedback position, different

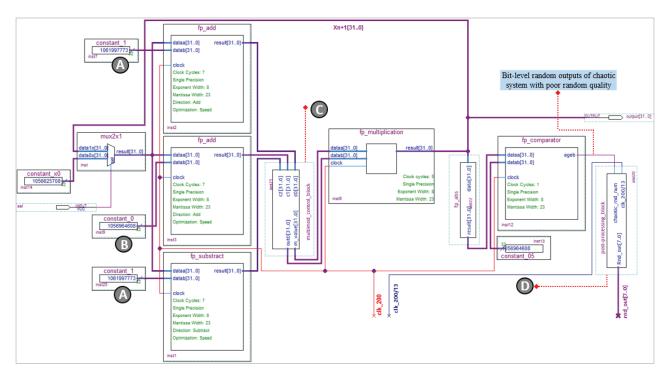

**Figure 3:** Hardware modeling of zigzag map in Quartus environment. In figure (A) is the common 2/|m| constant for Equation 1. (B) is the 0 (zero) constant used to ensure synchronization in the modeling phase. (C) and (D) are dataflow designed multi-mode control and post-processing circuit elements, respectively

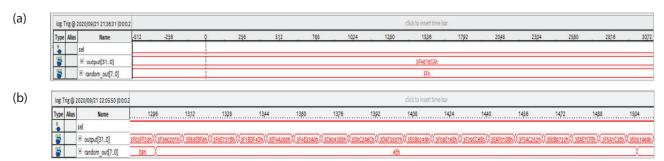

Figure 4: Real time simulation results of the zigzag map for (a) initial and (b) feedback positions

from the initial position. A triggering signal (sel) obtained from the physical ambiance is used as the selection pin of the mux at the input of the chaotic system to enable the transition between these positions. In order to obtain bit-level random oscillations (numbers) at the output of the PRNG, the 32-bit chaotic  $x_n$  random numbers are passed through the digitization and post-processing blocks, respectively. Quartus modeling of PRNG whose schematic structure is given in Fig. 2 as in Fig. 3. Real-time simulation of 32-bit hexadecimal random outputs representing the chaotic trajectory for the modeled zigzag map is as in Fig. 4.

For the mathematical operations, two addition (fp\_add), one subtraction (fp\_substract), one multiplication (fp\_multiplication), and one absolute value (fp\_abs), ready-to-use IP core modules which are able to do calculations with floating-point numbers are used in Fig. 3. In addition to these ready-to-use circuit modules, two dataflow designed block circuit elements (multimod\_control\_block & post\_processing\_block) are used in Fig. 3 (C) and (D).

In the initial position, the input values of the chaotic system  $x_0$  and m are 0.4898 and 2.5, respectively. The parameter is the common factor of the three different equalities in Eq. 1. For this reason, instead of calculating the common (2/|m|) expression for the first and third equalities in Eq. 1 in each iteration, the mathematical equivalent of this expression is defined as constant (constant\_1) as in Figure 3 (A). Therefore, the hardware equivalent of the equalities in Eq. 1 is  $(-m(x_n + con$ stant)),  $(m(x_n + 0))$  and  $(m(x_n - constant))$  respectively in Fig. 3. In the system, it is important that the calculation time is the same for all three equalities in terms of synchronization. For this purpose, for the second equality consisting of only multiplication, the addition with 0 (zero) constant is made as in Fig. 3 (B). Thus, the calculation times of the parallel connected  $(x_n + constant)$ ,  $(x_n + constant)$ + 0) and  $(x_n$  - constant) expressions were equalized in 7 clock pulses. The calculated results at each 7 clock pulses are simultaneously applied to  $c_1$ ,  $c_2$  and  $c_3$  inputs of the multimode control circuit in Fig. 3 (C), respectively.

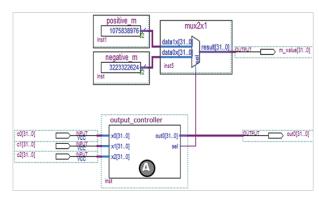

The outputs of the control circuit whose hardware modelling details are given in Fig. 5 are connected to the inputs of the multiplication circuit. The mathematical definition of the zigzag map consists of three different equations. Which equality will be used in the system is decided by looking at interval of the  $x_n$  values. The main task of the multimode control circuit in Fig. 5 is to determine which equality result should be used by checking the  $x_a$  interval and whether the common factor is positive or negative. For this, the dataflow designed circuit element (output\_controller) in Figure 5 (A) is used. The task of this component is to determine the interval of  $x_a$  by checking the c1 input to which the  $(x_a + 0)$  addition result is connected. The multimode control circuit in Fig. 5 has two 32-bit vectorial outputs, out0 and m\_value. The out0 output is switched to one of the input values  $c_1$ ,  $c_2$  and  $c_3$  in accordance with the  $x_n$ interval. When *out*0 output is switched to  $c_1$  input,  $m_{\perp}$ *value* output takes +m, in other cases  $(c_0, c_2)$  -m values.

**Figure 5:** Hardware modelling of the multimode control block

The calculation time required for multiplication in the system takes 5 clock pulses. With the addition, the calculation time required to obtain a 32-bit  $x_n$  random number in any iteration from the chaotic system is 12 clock pulses in total. The 32-bit random numbers whose absolute value is taken after the multiplication are applied as an input to the comparison circuit (fp\_comparator) in Fig.3. The calculation time of the comparison circuit is 1 clock pulse and performs bit-level transformations according to Eq. 2. However, the sta-

tistical randomness quality of the random numbers obtained for the threshold value, selected as 0.5 in Eq. 2, is cryptographically insufficient. Random numbers obtained from the chaotic system are applied to the input of the post processing block in Fig. 3 (D) to remove this shortcoming. The hardware modeling details of this block circuit, in which H function [25] post-processing technique is used, are as in Fig. 6.

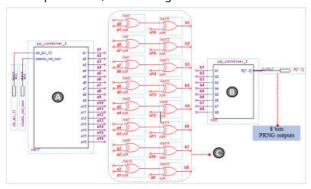

Figure 6: Hardware modelling of post-processing block

The post-processing technique in Fig. 6. consists of two combiner circuits (pp\_combiner1 & pp\_combiner\_2), used to obtain the desired bit-level logic vectorial inputs and outputs, in (A) and (B) and the H function in (C). The H function post-processing technique based on Quasigroup transformation needs 16-bit vectorial input obtained from chaotic system trajectory to produce 8-bit vectorial random output in each iteration. The task of the first combiner circuit (pp\_combiner\_1) in Fig. 6 (A) is to combine one-bit random numbers generated in every 13 clock pulses and to obtain 16bit logic vector inputs needed for the post-processing technique. Then, the random numbers passed through the XOR based H function block in Fig. 6 (C) are finally applied as an input to the other combiner circuit (pp\_ combiner\_2) in Fig. 6 (B). The 8-bit combined outputs of this circuit are also the hexadecimal outputs of PRNG.

The frequency of the clock signal applied to the input of the chaotic system is 200 MHz. The time to generate a 1-bit random sign / number for PRNG is 13 clock pulses depending on the calculation time of the chaotic system. In other words, for a 200 MHz clock sign with a period of 5 ns, the chaotic system produces a one-bit random number every 65 (13x5) ns. Hence, the output bit rate of PRNG is 200/13 = 15.4 Mbit/s without post-processing technique. However, the post-processing technique reduces the output bit rate of the chaos-based generator by 1/2. For this reason, the final output bit rate of chaotic PRNG drops to 15.4/2 = 7.7 Mbit/s after the post-processing technique is applied.

The time to obtain 16 bit-length random number sequences for the post-processing technique in the

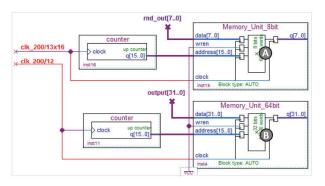

system is 208 (13x16) clock pulses. The 8-bit random numbers generated by PRNG every 208 clock pulses, and the 32-bit outputs of the zigzag map are recorded in two different memory architectures for testing purposes, as in Fig. 7 (A) and (B). Column widths of these memory architectures consisting of 65.536 rows are 8 and 32 bits, respectively. In both memory architectures, 16-bit counters are used for addressing. The memory architecture in Fig. 7 (A) is used for statistical analysis, while the memory architecture in (B) is used to verify the existence of chaos in the system for time series derived from the zigzag map. The frequencies of the clock signal applied to the input of the counter and memory architectures are 960 KHz (200/208) and 16.7 (200/12) MHz, respectively.

**Figure 7:** Memory architectures used for testing in the system

#### 4 Experimental validation

Experimental analysis of the study is carried out in three stages. In the first stage, the existence of chaos in the system for zigzag map and exponential sensitivity of PRNG to initial conditions are analysed. In the second stage, statistical analysis of bit-level numbers obtained from chaotic time series is performed. In the last stage, the hardware design criteria of the proposed PRNG are examined and its performance based on these criteria is compared with other studies in the literature.

#### 4.1 Lyapunov exponent analysis

The most distinctive feature distinguishing chaotic systems from other nonlinear systems is the exponential sensitivity to initial conditions, also known as the Butterfly Effect. The Lyapunov exponent is one of the frequently used method for analysing chaos in nonlinear systems and demonstrating the sensitive dependence of the system on initial conditions. The  $\lambda$  can be defined as the quantitative measurement of the amount of divergence and convergence in the phase space of two trajectories starting at very close points to each other. The existence of chaos in a nonlinear deterministic sys-

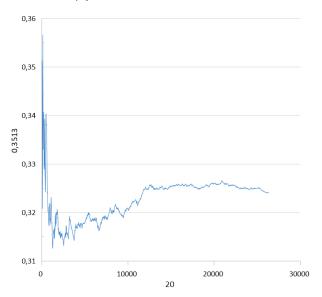

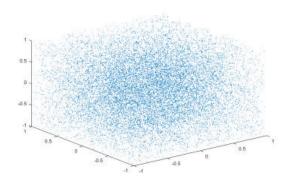

tem can be determined by looking at the sign of the  $\lambda$  value calculated as in the Eq. 3 of at least one trajectory. For at least one Lyapunov exponent greater than zero, the behaviour of the analysed system is defined as chaotic [18, 26]. The Lyapunov spectrum of the time series of the zigzag map obtained from the memory component in Fig. 7 (B) and the distributions of these series for the range [-1, 1] are as in Fig. 8 and 9 respectively.

$$\lambda = \lim_{n \to \infty} \frac{1}{n} \sum_{i=0}^{n-1} \ln |f'(x_i)| \tag{3}$$

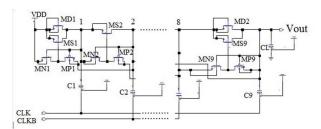

Figure 8: Lyapunov spectrum of the zigzag map

**Figure 9:** Distribution of time series obtained from chaotic system

The positive Lyapunov exponent in Fig. 8 confirms that the zigzag map for  $x_0$  and m input values is in chaos and the system display a random-like behaviour. This case also shows that the chaotic system exhibits nonperiodic behaviour and that orbital outputs are unpredictable in long-term. This also shows that the orbital outputs of the chaotic system exhibiting non-periodic behaviour are unpredictable in the long-term and in

this case, cryptographically reliable random numbers can be obtained from PRNG.

#### 4.2 Statistical randomness analysis

In the presented study, NIST SP 800-22 statistical randomness test suite [27] is used to verify the statistical sufficiency of PRNG. The test technique consists of 15 separate subtest criteria and calculates the α and pvalue parameters for each test criterion. The p-value parameter, which is the probability random numbers are generated from an ideal RNG, varies in the range [0-1]. If p-value equals 1 for a test criterion, the sequence of numbers for the relevant test criterion is considered to be perfectly random. Otherwise, there is no randomness for the relevant test criterion. The  $\alpha$  parameter, corresponding to the typical significance level, is in the [0.001–0.01]. range. For  $\alpha$  = 0.01, TRNG is considered to correctly produce 99 out of every 100 random number sequences. For the numbers testing, the p-value parameter for each test criterion must be greater than the α parameter [3, 28]. The sample length of each random number sequence tested is equivalent to the memory capacity in Fig. 7 (A). In other words, a random number sequence obtained from the PRNG for testing purposes at once time, consists of 524.288 (65.536x8) bits. The measured NIST 800-22 test results for PRNG are given in Table 1.

Table 1: NIST 800-22 test results

| Test Name                                   | p-value        | Result  |

|---------------------------------------------|----------------|---------|

| Frequency test                              | 0.703          | Success |

| Frequency test within a block               | 0.728          | Success |

| Run test                                    | 0.594          | Success |

| Test for the longest run of ones in a block | 0.512          | Success |

| Binary matrix rank                          | 0.679          | Success |

| Discrete Fourier transform                  | 0.912          | Success |

| Non-Overlapping template matching           | 0.500          | Success |

| The overlapping template matching test      | 0.490          | Success |

| Maurer's universal statistical test         | 0.338          | Success |

| Linear complexity test                      | 0.697<br>0.415 | Success |

| Serial test                                 | 0.793          | Success |

| Approximate entropy test                    | 0.654          | Success |

| Cumulative sums                             | 0.871          | Success |

In order for the outputs of any PRNG or TRNG to be used directly in cryptography, the randomness quality of the generator must be verified by statistical testing tools. In Table 1, the p-value  $> \alpha$  condition has been fulfilled in all of the test criteria for the post-processed random

numbers. In this case, where the test criteria are considered successful, it can be said that the proposed zigzag map-based generator fulfils cryptographic requirements in terms of statistical randomness. The obtained results are important in terms of showing that the zigzag map can be used for different cryptographic purposes, especially random number generation methods.

#### 4.3 Hardware performance analysis

The area-energy requirement of any cryptographic RNG is important in terms of evaluating the applicability of the generator on today's cryptographic applications and devices, where area-energy consumption is a major problem [3, 14]. Despite having statistically impressive results, solutions with high structural complexity applied for security requirement can often make an RNG dysfunctional. Therefore, hardware cost analysis of any RNG is important in respect to evaluating the practical usefulness of the generator. For this reason, it is important for an RNG to fulfil the security-related statistical requirements with minimum hardware cost in terms of the efficiency of the cryptographic applications they are used.

Although based on simple mathematical definitions, the fact that chaotic orbital outputs consist of three different equalities increases the complexity of the zigzag map in terms of hardware implementation. However, besides the ready IP modules, the dataflow designed circuit elements in Fig. 3 (C) and (D) reduce this complexity as much as possible in terms of hardware. Especially since the  $(m \cdot x_n)$  factor is common in all three equalities, only one multiplication circuit is used with the help of the control circuit in Fig. 3 (C) instead of three different multiplication circuits. In addition, in Eq.1, 2/|m| expression is common for the first and third equalities. For any initial value of the system parameter m, the value of this expression will not change during the running time of the PRNG. Therefore, instead of using extra division and absolute value circuits to calculate the value of this expression in the implementation phase, the mathematical equivalent of this expression is defined as constant circuit element as in Fig. 3 (A). This also simplifies the implementation of the chaotic generator as well as reducing the area-energy demand. The area-energy consumption parameters of the proposed zigzag map-based generator after the place-routing process is performed on FPGA chip are shown in Table 2.

**Table 3:** Comparison of the main characteristics of different chaos-based RNG proposals in the literature

| Ref.       | Chaotic System                                        | Hardware<br>Characteristic | Test Tool                 | Frequency<br>(MHz) | Post-<br>Processing | Throughput<br>(Mbps) |

|------------|-------------------------------------------------------|----------------------------|---------------------------|--------------------|---------------------|----------------------|

| [8]        | Logistic, Bernoulli and Tent Map                      | CMOS (0.25<br>μm)          | NIST 800-22               | -                  | -                   | -                    |

| [20]       | Enhanced Henon Map                                    | FPGA                       | NIST 800-22               | 50                 |                     | 3.9                  |

| [21]       | Logistic map                                          | FPGA                       | NIST 800-22               | -                  | -                   | 1.0                  |

| [24]       | Bernoulli Map                                         | FPGA                       | NIST 800-22               | 50                 | -                   | 1.5                  |

| [29]       | Chua circuit                                          | CMOS (0.18<br>μm)          | FIPS 140-1                | -                  | 6-bit LFSR          | 2.02                 |

| [30]       | Coupled chaotic oscillator                            | CMOS (0.35<br>μm)          | FIPS 140-1<br>NIST 800-22 | 1.24               | Von<br>Neumann      | 2.0                  |

| [31]       | 3D chaotic system                                     | FPGA                       | FIPS 140-1<br>NIST 800-22 | 373                | XOR                 | 4.59                 |

| [32]       | Tent Map                                              | CMOS (0.18<br>μm)          | NIST 800-22               | 250 (KHz)          | 8-bit LFSR          | 0.25                 |

| [33]       | Sprott 94 G chaotic system                            | FPGA                       | NIST 800-22               | 339                | -                   | -                    |

| [34]       | Logistic and Henon map                                | FPGA                       | -                         | 190                | -                   | 1.0                  |

| [35]       | Piecewise-Affine Markov maps                          | FPGA                       | FIPS 140-1                | 24                 | XOR                 | 60 (Kpbs)            |

| [36]       | Lorenz and Lü chaotic systems                         | FPGA                       | NIST 800-22               | 78                 | -                   | -                    |

| [37]       | Memristive Canonical Chua oscillator and logistic map | FPGA                       | NIST 800-22               | 59                 | XOR                 | 0,1.25               |

| [38]       | Time-delay chaotic system                             | FPGA                       | NIST 800-2<br>FIPS 140-2  | 120                | -                   | 4.0                  |

| [39]       | Sinusoidal iterator                                   | FPGA                       | NIST 800-22               | 200                | -                   | 4.77                 |

| This study | Zigzag map                                            | FPGA                       | NIST 800-22               | 200                | H function          | 7.7                  |

Table 2: The FPGA chip statistics of the Zigzag map RNG

| Parameters<br>(Altera Cyclone IV GX<br>EP4CGX150DF31C8) | Total<br>FPGA Unit | % Used for<br>Zigzag Map<br>PRNG |

|---------------------------------------------------------|--------------------|----------------------------------|

| Total Logic Elements                                    | 149.760            | 2.160 (1 % )                     |

| Total combinational functions                           | 149.760            | 2.093 (<1 %)                     |

| Total dedicated registers                               | 149.760            | 1.100 (1 % )                     |

| Total memory bits                                       | 6.635.520          | 93 (< 1 % )                      |

| Embedded Multipliers<br>9-bit                           | 720                | 7 (1 %)                          |

| Total pins                                              | 508                | 10 (2 % )                        |

| Total PLLs                                              | 8                  | 1 (13 %)                         |

| Power Dissipation (mW)                                  |                    |                                  |

| Dynamic                                                 | -                  | 10.84                            |

| Static                                                  | -                  | 105.17                           |

| Ю                                                       | -                  | 11.01                            |

| Total                                                   | -                  | 127.02                           |

The results given in Table 2 show that besides its good statistical properties, PRNG can be used easily in resource-restricted embedded cryptographic applications. PRNG architecture, based on general principles in terms of modelling technique, is a device independent generator model with low area-energy consumption, so it can be easily applied on resource restricted architectures. In addition, the generator's being based on digital design techniques and easy re-configurability feature are other important advantages in terms of hardware implementation.

The output bit rate performance of the proposed zigzag map based PRNG has been compared with other hardware based chaotic RNGs in the literature. Comparison results are as in Table 3. When the results in Table 3 are examined, it can be seen that PRNG offers a higher output bit rate compared to other studies, although the output bitrate decreases by 1/2 due to the post processing technique.

#### 5 Conclusion

In this study, the hardware implementation of a new PRNG using the chaotic Zigzag map as entropy source on FPGA environment is presented. The bit-level random outputs of PRNG are obtained from the trajectory produced by the chaotic zigzag map for the initial value of  $x_0$ . The outputs representing the 32-bit chaotic orbit in the system are transformed into bit-level random numbers / signs with the help of a simple comparison circuit and subjected to post-processing technique. While the Zigzag map is in chaos state, PRNG's post-processed outputs successfully pass the NIST 800-22 tests. Statistical randomness results confirm

that the chaotic system modelled can be used for different cryptographic purposes as well as random number generation methods. In addition, the low hardware resource requirement makes PRNG easily applicable in resource-constrained hardware architectures and applications. In another aspect, the study is important in terms of showing the usability of the zigzag map in different chaos-based engineering applications and being a source for these studies.

#### 6 Conflict of interest

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

#### 7 References

- Ergun, S., Ozoguz, S., "A chaos-modulated dual oscillator-based truly random number generator," In 2007 IEEE International Symposium on Circuits and Systems, pp. 2482-2485, IEEE, 2007. https://doi.org/10.1109/iscas.2007.378742

- 2. Özkaynak, F., "Cryptographically secure random number generator with chaotic additional input", Nonlinear Dynamics, vol.78(3), pp.2015-2020, https://doi.org/10.1007/s11071-014-1591-y

- Garipcan, A. M., Erdem, E. "Implementation and Performance Analysis of True Random Number Generator on FPGA Environment by Using Nonperiodic Chaotic Signals Obtained from Chaotic Maps," Arabian Journal for Science and Engineering, 2019. https://doi.org/10.1007/s13369-019-04027-x

- 4. Lambić, D., Nikolić, M., "Pseudo-random number generator based on discrete-space chaotic map," Nonlinear Dynamics, vol. 90(1), pp. 223-232, 2017. https://doi.org/10.1007/s11071-017-3656-1

- Nejati, H., Beirami, A., Ali, W. H., "Discrete-time chaotic-map truly random number generators: design, implementation, and variability analysis of the zigzag map," Analog Integrated Circuits and Signal Processing, vol. 73(1), pp. 363-374, 2012. https://doi.org/10.1007/s10470-012-9893-9

- Cicek, I., Pusane, A. E., Dundar, G., "Random number generation using field programmable analog array implementation of logistic map" In 2013 21st Signal Processing and Communications Applications Conference (SIU) (pp. 1-4). IEEE, 2013. https://doi.org/10.1109/siu.2013.6531560

- 7. Ozkaynak, F., "A Novel Random Number Generator Based on Fractional Order Chaotic Chua Sys-

- tem", Elektronika ir Elektrotechnika, vol. 26(1), pp. 52-57, 2020.

- https://doi.org/10.5755/j01.eie.26.1.25310

- 8. Cicek, I., Pusane, A. E., Dundar, G., "A novel design method for discrete time chaos based true random number generators" Integration the VLSI Journal, vol. 47(1), pp. 38-47, 2014. https://doi.org/10.1016/j.vlsi.2013.06.003

- Li, X., Yu, H., Zhang, H., Jin, X., Sun, H., Liu, J., "Video encryption based on hyperchaotic system," Multimedia Tools and Applications, vol. 79(33), pp. 23995-24011, 2020.

- https://doi.org/10.1007/s11042-020-09200-1

- Tang, K. W., Tang, W. K., Man, K. F., "A chaos-based pseudo-random number generator and its application in voice communications," International Journal of Bifurcation and Chaos, vol. 17(03), pp. 923-933, 2007.

- https://doi.org/10.1142/s021812740701763x

- Ge, R., Yang, G., Wu, J., Chen, Y., Coatrieux, G., Luo, L., "A novel chaos-based symmetric image encryption using bit-pair level process," IEEE Access, vol. 7, pp. 99470-99480, 2019.

- https://doi.org/10.1109/access.2019.2927415

- Garcia-Bosque, M., Pérez, A., Sánchez-Azqueta, C., Celma, S., "Application of a MEMS-based TRNG in a chaotic stream cipher" Sensors, vol. 17(3), 646, 2007.

- https://doi.org/10.3390/s17030646

- 13. Tanyildizi, E., Özkaynak, F., "A new chaotic S-box generation method using parameter optimization of one dimensional chaotic maps," IEEE Access, vol. 7, pp. 117829-117838.

- https://doi.org/10.1109/access.2019.2936447

- Garipcan, A. M., Erdem, E., "A TRNG using chaotic entropy pool as a post-processing technique: analysis, design and FPGA implementation", Analog Integrated Circuits and Signal Processing, pp. 1-20, 2020.

- https://doi.org/10.1007/s10470-020-01605-0

- 15. Tuna, M., Alçın, M., Koyuncu, İ., Fidan, C. B., Pehlivan, İ., "High speed FPGA-based chaotic oscillator design", Microprocessors and Microsystems, vol. 66, pp. 72-80,2019.

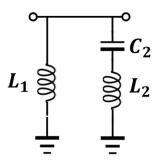

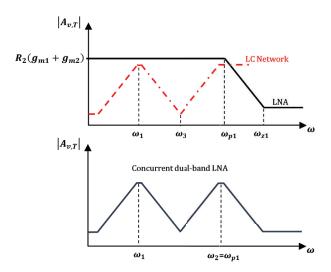

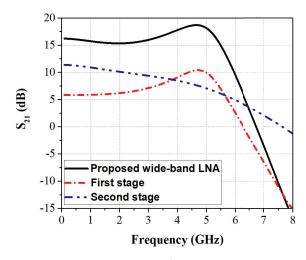

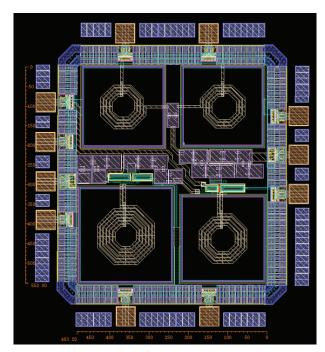

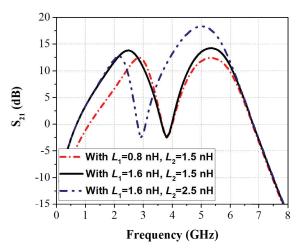

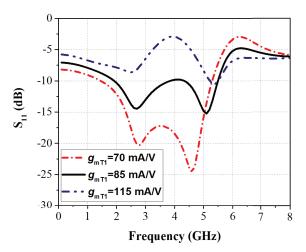

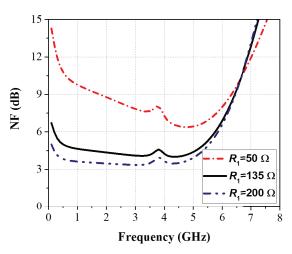

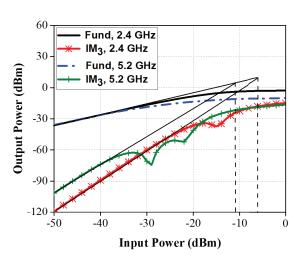

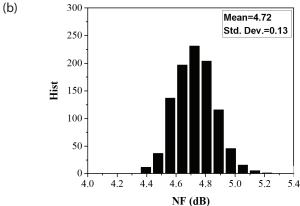

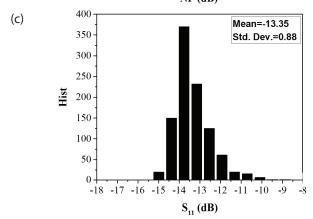

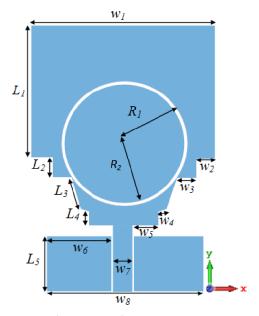

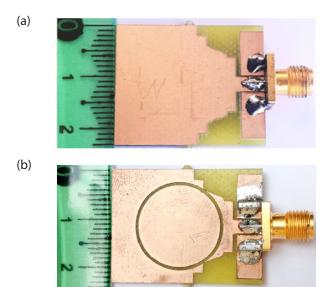

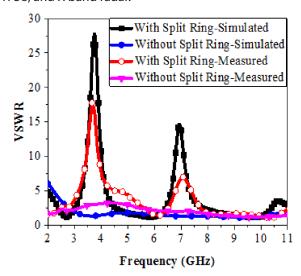

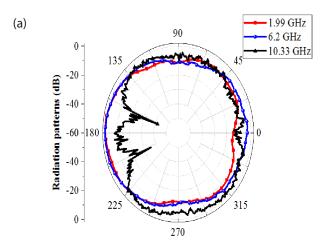

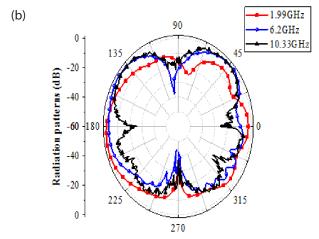

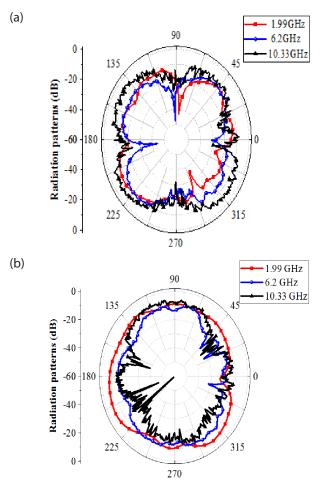

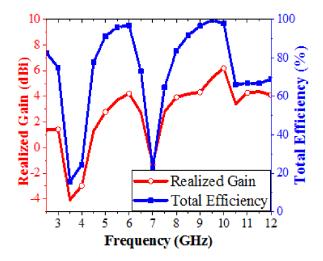

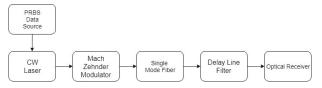

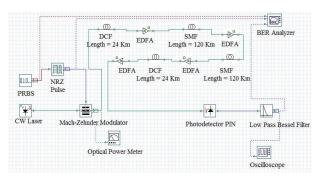

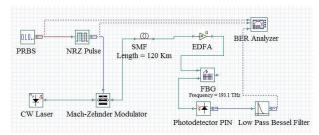

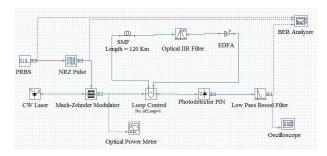

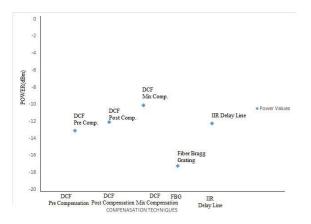

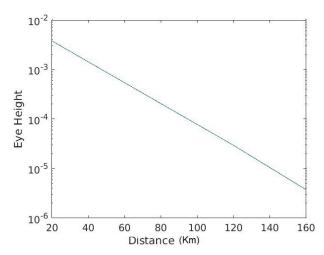

- https://doi.org/10.1016/j.micpro.2019.02.012