Strokovno društvo za mikroelektroniko elektronske sestavne dele in materiale

3.2006

Strokovna revija za mikroelektroniko, elektronske sestavne dele in materiale Journal of Microelectronics, Electronic Components and Materials

INFORMACIJE MIDEM, LETNIK 36, ŠT. 3(119), LJUBLJANA, september 2006

#### **INFORMACIJE**

### **MIDEM**

**3** • 2006

INFORMACIJE MIDEM

LETNIK 36, ŠT. 3(119), LJUBLJANA,

SEPTEMBER 2006

INFORMACIJE MIDEM

VOLUME 36, NO. 3(119), LJUBLJANA,

SEPTEMBER 2006

Revija izhaja trimesečno (marec, junij, september, december). Izdaja strokovno društvo za mikroelektroniko, elektronske sestavne dele in materiale - MIDEM. Published guarterly (march, june, september, december) by Society for Microelectronics, Electronic Components and Materials - MIDEM.

Glavni in odgovorni urednik

**Editor in Chief**

Dr. Iztok Šorli, univ. dipl.ing.fiz., MIKROIKS d.o.o., Ljubljana

Tehnični urednik Executive Editor Dr. Iztok Šorli, univ. dipl.ing.fiz., MIKROIKS d.o.o., Ljubljana

Uredniški odbor Editorial Board Dr. Barbara Malič, univ. dipl.ing. kem., Institut Jožef Stefan, Ljubljana Prof. dr. Slavko Amon, univ. dipl.ing. el., Fakulteta za elektrotehniko, Ljubljana Prof. dr. Marko Topič, univ. dipl.ing. el., Fakulteta za elektrotehniko, Ljubljana

Prof. dr. Rudi Babič, univ. dipl.ing. el., Fakulteta za elektrotehniko, računalništvo in informatiko

Maribor

Dr. Marko Hrovat, univ. dipl.ing. kem., Institut Jožef Stefan, Ljubljana Dr. Wolfgang Pribyl, Austria Mikro Systeme Intl. AG, Unterpremstaetten

Časopisni svet International Advisory Board Prof. dr. Janez Trontelj, univ. dipl.ing. el., Fakulteta za elektrotehniko, Ljubljana,

PREDSEDNIK - PRESIDENT

Prof. dr. Cor Claeys, IMEC, Leuven

Dr. Jean-Marie Haussonne, EIC-LUSAC, Octeville

Darko Belavič, univ. dipl.ing. el., Institut Jožef Stefan, Ljubljana

Prof. dr. Zvonko Fazarinc, univ. dipl.ing., CIS, Stanford University, Stanford

Prof. dr. Giorgio Pignatel, University of Padova

Prof. dr. Stane Pejovnik, univ. dipl.ing., Fakulteta za kemijo in kemijsko tehnologijo, Ljubljana

Dr. Giovanni Soncini, University of Trento, Trento

Prof. dr. Anton Zalar, univ. dipl.ing.met., Institut Jožef Stefan, Ljubljana Dr. Peter Weissglas, Swedish Institute of Microelectronics, Stockholm

Prof. dr. Leszek J. Golonka, Technical University Wroclaw

Naslov uredništva Headquarters Uredništvo Informacije MIDEM

MIDEM pri MIKROIKS

Stegne 11, 1521 Ljubljana, Slovenija tel.: + 386 (0)1 51 33 768 fax: + 386 (0)1 51 33 771 e-mail: lztok.Sorli@guest.arnes.si http://www.midem-drustvo.si/

Letna naročnina znaša 12.000,00 SIT, cena posamezne številke je 3000,00 SIT. Člani in sponzorji MIDEM prejemajo Informacije MIDEM brezplačno. Annual subscription rate is EUR 100, separate issue is EUR 25. MIDEM members and Society sponsors receive Informacije MIDEM for free.

Znanstveni svet za tehnične vede I je podal pozitivno mnenje o reviji kot znanstveno strokovni reviji za mikroelektroniko, elektronske sestavne dele in materiale. Izdajo revije sofinancirajo ARRS in sponzorji društva.

Scientific Council for Technical Sciences of Slovene Research Agency has recognized Informacije MIDEM as scientific Journal for microelectronics, electronic components and materials.

Publishing of the Journal is financed by Slovene Research Agency and by Society sponsors.

Znanstveno strokovne prispevke objavljene v Informacijah MIDEM zajemamo v podatkovne baze COBISS in INSPEC.

Prispevke iz revije zajema ISI® v naslednje svoje produkte: Sci Search®, Research Alert® in Materials Science Citation Index™

Scientific and professional papers published in Informacije MIDEM are assessed into COBISS and INSPEC databases.

The Journal is indexed by ISI® for Sci Search®, Research Alert® and Material Science Citation Index™

Po mnenju Ministrstva za informiranje št.23/300-92 šteje glasilo Informacije MIDEM med proizvode informativnega značaja.

Grafična priprava in tisk

Printed by

BIRO M, Ljubljana

Naklada Circulation

1000 izvodov 1000 issues

Poštnina plačana pri pošti 1102 Ljubljana

Slovenia Taxe Percue

| UDK621.3:(53+54+621+66).     | ISSN0352-9045  |

|------------------------------|----------------|

| - UDNOZ 1.3.(33T34TOZ 1TOO). | 133110332"9043 |

#### Informacije MIDEM 36(2006)3, Ljubljana

| NO21.3.(33+34+021+00), 133N0332-3043 |                                                                                                                                                                   |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      | PROFESSIONAL SCIENTIFIC PAPERS                                                                                                                                    |

| 123                                  | J.Zarębski, J.Dąbrowski:<br>D.C. Characteristics of SiC Power Schottky Diodes -<br>Modelling In Spice                                                             |

| 127                                  | R. Babič, D. Osebik<br>The Comparison of Audio Preamplifier Circuits with<br>Solid State Transistors and Vacuum Tube                                              |

| 134                                  | M.Prelovšek, G.Bizjak:<br>Variations of Color Correlated Temperature of White<br>LED Light                                                                        |

| 140                                  | B.Wagner, Á.Bűrmen, J.Puhan, S.Tomažič, T.Tuma:<br>Application of Extrapolation Algorithms in Nonlinear<br>Circuit Simulation and Optimization with SPICE<br>OPUS |

| 148                                  | S.Seemi, M.Shahiman Sulaiman,<br>A.Suhail Farooqui, M.B.I. Reaz:<br>New Interpolation Technique for Highly<br>Linear CMOS ADC                                     |

| 151                                  | J.Dedič, M.Finc, A.Trost:<br>A Framework for High-Level System Design<br>Exploration                                                                              |

| 161                                  | M. Možek, D. Vrtačnik, D. Resnik, U. Aljančič, S. Penič, S. Amon: Calibration System for Smart Pressure Sensors                                                   |

|                                      | CONFERENCE REPORTS                                                                                                                                                |

| 166                                  | Ist Slovene Photovoltaic Conference                                                                                                                               |

| 167                                  | 21st European Photovoltaic Solar Energy Conference<br>and Exhibition - Slovene Researchers Were<br>Awarded the Best Session Poster Award                          |

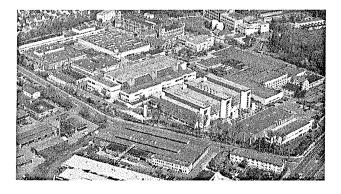

| 169                                  | In 2006 muRata Celebrates 25 <sup>th</sup> Anniversary of its<br>Presence in Europe                                                                               |

| 171                                  | NEWS                                                                                                                                                              |

| 173                                  | MIDEM Registration Form                                                                                                                                           |

|                                      | Front page:<br>V letu 2006 muRata proslavlja 25.obletnico<br>prisotnosti v Evropi                                                                                 |

|                                      | 127 134 140 148 151 161 166 167 169 171                                                                                                                           |

### Obnovitev članstva v strokovnem društvu MIDEM in iz tega izhajajoče ugodnosti in obveznosti

Spoštovani,

V svojem več desetletij dolgem obstoju in delovanju smo si prizadevali narediti društvo privlačno in koristno vsem članom. Z delovanjem društva ste se srečali tudi vi in se odločili, da se v društvo včlanite. Življenske poti, zaposlitev in strokovno zanimanje pa se z leti spreminjajo, najrazličnejši dogodki, izzivi in odločitve so vas morda usmerili v povsem druga področja in vaš interes za delovanje ali članstvo v društvu se je z leti močno spremenil, morda izginil. Morda pa vas aktivnosti društva kljub temu še vedno zanimajo, če ne drugače, kot spomin na prijetne čase, ki smo jih skupaj preživeli. Spremenili so se tudi naslovi in način komuniciranja.

Ker je seznam članstva postal dolg, očitno pa je, da mnogi nekdanji člani nimajo več interesa za sodelovanje v društvu, se je Izvršilni odbor društva odločil, da stanje članstva uredi in vas zato prosi, da izpolnite in nam pošljete obrazec priložen na koncu revije.

Naj vas ponovno spomnimo na ugodnosti, ki izhajajo iz vašega članstva. Kot član strokovnega društva prejemate revijo »Informacije MIDEM«, povabljeni ste na strokovne konference, kjer lahko predstavite svoje raziskovalne in razvojne dosežke ali srečate stare znance in nove, povabljene predavatelje s področja, ki vas zanima. O svojih dosežkih in problemih lahko poročate v strokovni reviji, ki ima ugleden IMPACT faktor. S svojimi predlogi lahko usmerjate delovanje društva.

Vaša obveza je plačilo članarine 25 EUR na leto. Članarino lahko plačate na transakcijski račun društva pri A-banki : 051008010631192. Pri nakazilu ne pozabite navesti svojega imena!

Upamo, da vas delovanje društva še vedno zanima in da boste članstvo obnovili. Žal pa bomo morali dosedanje člane, ki članstva ne boste obnovili do konca leta 2006, brisati iz seznama članstva.

Prijavnice pošljite na naslov:

MIDEM pri MIKROIKS

Stegne 11

1521 Ljubljana

Ljubljana, september 2006

Izvršilni odbor društva

# D.C. CHARACTERISTICS OF SIC POWER SCHOTTKY DIODES MODELLING IN SPICE

Janusz Zarębski, Jacek Dąbrowski

Gdynia Maritime University, Department of Marine Electronics

Key words: Silicon Carbide (SiC), Schottky Barrier Diodes (SBDs), modelling, self-heating, electrothermal macromodel, SPICE

Abstract: In this paper the problem of SPICE modelling of the class of silicon-carbide (SiC) Schottky diodes with thermal effects (self-heating) taken into account is considered. Since April 2001 the SiC Schottky diodes made by Infineon Technologies have been commercially attainable. In the paper the SPICE electrothermal (including self-heating) macromodel of Infineon Technologies SiC Schottky diode is presented and in detail investigated. The considered macromodel has been verified experimentally. The silicon-carbide SDP04S60 rectifier has been tested. The nonisothermal characteristics obtained from measurements and SPICE calculations of SDP04S60 diode are compared. Due to the unacceptably large differences between measurements and calculations, some modifications of the macromodel have been proposed.

# DC karakteristike močnostnih SiC Schottky diod – modeliranje s programom SPICE

Kjučne besede: Silicijev karbid ( SiC ), Schottky diode, modeliranje, pregrevanje, elektrotermični model, SPICE

Izvleček: V prispevku obravnavamo probleme pri modeliranju SiC Schottkyjevih diod s programom SPICE z upoštevanjem termičnih efektov. Od aprila leta 2001 so SiC Schottky diode izdelane pri podjetju Infineon Technologies tudi komercialno dosegljive. Tako v prispevku predstavimo in natančno obravnavamo SPICE elektrotermični model prav teh diod. Predastavljeni model smo preverili tudi eksperimentalno in sicer smo testirali SiC diodo z oznako SDP04S60. Primerjali smo izmerjene in izračunane neizotermične karakteristike. Zaradi velikih razlik med meritvami in napovedmi, predlagamo določene spremembe pri parametrih makromodela.

#### 1. Introduction

The silicon carbide (SiC) is a great promising semiconductor material for manufacturing of power devices. It occurs in over 170 polytypes, the most common of which are cubic 3C, hexagonal 4H and 6H structures. A number of most important physical aspects of SiC compared to other semiconductors one can find in the literature, e.g. /1,2,3/. As results from the cited papers, silicon carbide has an order of magnitude higher breakdown electric field and an electron mobility only about 20% lower (for 4H-SiC) than silicon. A high breakdown electric field allows to design the SiC power devices with 10-times thinner and about 100-times higher dopend voltage blocking layers. Smaller dimensions of SiC material result in higher device switching frequency.

Nowadays, a lot of SiC devices, as transistors, diodes, thyristors, LED's, thermistors etc. are manufactured and investigated in laboratories /4,5/. In the case of the power SiC devices a high breakdown voltage is needed. So far, the SiC power diodes, have been the class of semiconductor devices having the greatest values of the breakdown voltage equal to 10 kV for Schottky diodes /6/ and 19 kV for PiN diodes /7/. Since 2001 SiC Schottky diodes made by Infineon Technologies have been available in the market /8/.

A very important feature of all semiconductor devices, including SiC SBDs, is a strong influence of the temperature on their characteristics. Due to the self-heating resulting

from the change of the device dissipated power into the heat in the case of nonideal cooling conditions, the junction temperature (often much greater than the ambient one) affects the device characteristics, called the nonisothermal ones. In order to take into account the self-heating, the models of the special kind, called the electrothermal models (ETM) have to be used for the device simulations.

Infineon Technologies, on their web-side /9/, offers the SiC Schottky's electrothermal macromodel for SPICE, indicated as Level 3.

In the paper the Level 3 Infineon's SPICE macromodel is presented, in detail discussed and experimentally verified. The SDP04S60 diode: 4A/600V, has been chosen for investigations, instead of 6A/600V SiC Schottky diode (SDP06S60) considered in /10/. Due to the fact, that obtained results between measurements and calculations differ from each other significantly, therefore some modifications of the macromodel were introduced.

### 2. The Macromodel Form of The SiC Schottky Diode

To derive the electrothermal macromodel of the considered device, the following dependencies have to be used /11/:

the current-voltage-temperature dependence (isothermal model), the dependence of the inside (junction) temperature

T<sub>i</sub> on the electrical power dissipated in the device,

along with the dependence of this electrical power

on the device terminal currents and voltages (thermal

model).

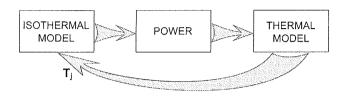

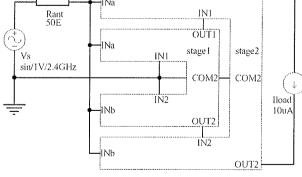

The structure of such a macromodel is shown in Fig. 1.

Fig. 1. The structure of the electrothermal macromodel of the SiC Schottky diode

Next, the detailed form of the isothermal model and the thermal model, forming the considered electrothermal macromodel are presented and discussed.

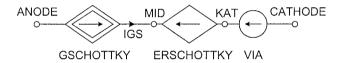

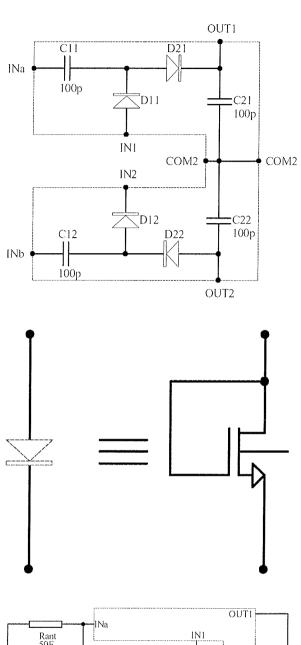

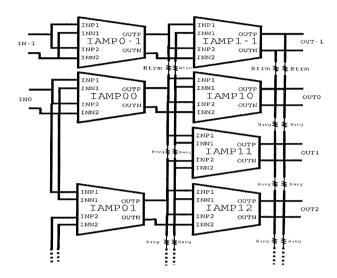

The network form of the isothermal model of the SiC Schottky diodes is presented in Fig. 2. /9/.

Fig. 2. The network form of the isothermal model of the SiC Schottky diode

As seen, the model is composed of three elements: the controlled current GSCHOTTKY source, the controlled voltage ERSCHOTTKY source and the independent source VIA of the efficiency equal to zero. Due to the d.c. dependencies considered here, the wire inductance and junction capacitance are not taken into account in further considerations.

The control current source GSCHOTTKY is of the efficiency

$$I_{GS}(T,V) = I_{bw} \cdot \left[ \exp\left(\frac{V \cdot q}{k \cdot (T_0 + T)}\right) - 1 \right]$$

(1)

where T – the analysis temperature ( $T \equiv TEMP$ ) in Celsius degrees, V – voltage between ANODE and MID nodes,  $I_{bw}$  – reverse (saturation) current, q – electron charge, k – Boltzmann's constant,  $T_0$  – the reference temperature.

The saturation current is expressed by the formula

$$I_{bw} = AREA \cdot A_0 \cdot (T_0 + T)^2 \cdot \exp\left(\frac{-q \cdot \phi_{SiC}}{k \cdot (T_0 + T)}\right) \cdot K \quad (2)$$

where AREA – relative device area,  $A_0$  – Richardson's constant,  $\phi_{SiC}$  – metal-semiconductor barrier height.

In Eq.(2) the factor K models the lowering effect existing in the reverse range of the Schottky diode operation which is

given by the following expression

$$K = \exp\left(\frac{q \cdot \sqrt{\beta \cdot EFLD_{(v)}}}{k \cdot (T_0 + T)}\right).$$

$$\frac{1}{2} \cdot \left(1 + \exp\left(AA + AB \cdot (T - 127) + AC \cdot (T - 127)^2 + \frac{\alpha_1 \cdot EFLD_{(v)}}{EFLD_{\left(\frac{-VPT}{5}\right)}}\right)\right)$$

(3)

where b, AA, AB, AC,  $\alpha_1$  and VPT are the model parameters.

The description of the electric field (*EFLD*) dependent on the junction reverse voltage is divided into three ranges according to the value of the anode-cathode voltage, up to the pattern (4), where *V* denotes the voltage on the diode, *EPT* denotes the critical electrical field, whereas *x* and *g* are the model parameters. *LIMIT* denotes the SPICE standard function.

$$EFLD = \begin{cases} 0 & if \quad V > 0 \\ \sqrt{\xi \cdot \text{LIMIT}(-V, 0, VPT)} & if \quad -V < VPT \\ \text{EPT} - \gamma \cdot \left(\frac{V}{VPT} + 1\right) & if \quad -V \ge VPT \end{cases} \tag{4}$$

In turn, the voltage source ERSCHOTTKY controlled by the current of VIA source models the influence of the diode series resistance on the i(u) characteristics. Thus

$$U_{ERS} = I_{(VIA)} \cdot R_{S(T)} = \frac{I_{(VIA)} \cdot R_{0SQ}}{AREA \cdot V_j^2} \cdot \left(\frac{T_0 + T}{T_0}\right)^{\chi}$$

(5)

where  $R_{S(T)}$  is the series resistance dependent on the temperature,  $R_{OSQ}$  is the specific series resistance at the reference temperature  $T_0$ , whereas  $I_{(V|A)}$  is the zero voltage source current and  $\chi$ ,  $V_j$  are the model parameters. The isothermal model parameter values of the diode are collected in Table 1 /9/.

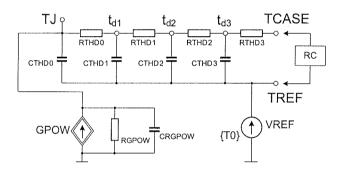

The thermal model of the considered diode has been presented in the network form (Cauer leader) consisting of four resistors (RTHD) and capacitances (CTHD), representing the junction-to-case thermal impedance of the diode (Fig. 3.) /9/. The values of those elements are given in Table 2. The nodes TJ and TCASE represent the junction and the case temperatures respectively, whereas the potential value of the node TREF representing the ambient temperature, can be fixed by the efficiency of the voltage source VREF. This form of the thermal model is not acceptable by SPICE due to the fact, that the TREF node has not d.c. connection with the other one. Therefore, in the case of the ideal conditions of the case cooling, the nodes TREF and TCASE have to be shorted. Otherwise, between the nodes TCASE and TREF, the RC network of the Cauer leader, representing the phenomena of heat removing from the case to the ambient (e.g. by means of a heat-sink), has to be added.

Table 1 The parameters values of the isothermal model of the SDP04S60 diode

| Parameter                                     | Value                                                |  |  |

|-----------------------------------------------|------------------------------------------------------|--|--|

| <i>q</i> [C]                                  | $1.602 \cdot 10^{-19}$                               |  |  |

| k [J/K]                                       | $1.38 \cdot 10^{-23}$                                |  |  |

| $T_0[K]$                                      | 273                                                  |  |  |

| $A_0 [A \cdot cm^{-2} \cdot K^{-2}]$          | 110                                                  |  |  |

| $\phi_{SiC}[eV]$                              | 1.3                                                  |  |  |

| AA, AB, AC                                    | $-1.5$ , $-12.95 \cdot 10^{-3}$ , $91 \cdot 10^{-6}$ |  |  |

| $\alpha_1$                                    | 3.8                                                  |  |  |

| $R_{0SQ}[\mathrm{m}\Omega\cdot\mathrm{cm}^2]$ | 0.9                                                  |  |  |

| VPT [V]                                       | 400                                                  |  |  |

| EPT [V/cm]                                    | $1.05 \cdot 10^6$                                    |  |  |

| β                                             | 1.49 · 10 <sup>-8</sup>                              |  |  |

| ٤                                             | $2.811 \cdot 10^9$                                   |  |  |

| γ                                             | 5.33 · 10 <sup>5</sup>                               |  |  |

| χ                                             | 1.5                                                  |  |  |

| AREA                                          | 0.0116                                               |  |  |

| $V_{j}$                                       | 0.75                                                 |  |  |

Fig. 3. The general form of the thermal model of the SiC SDP04S60 Schottky diode

Table 2 The parameter values of the thermal model of the SDP04S60 diode

| Parameter | Unit       | Value                  |

|-----------|------------|------------------------|

| RTHD0     |            | 1.756                  |

| RTHD1     | F1Z /1373  | 1.717                  |

| RTHD2     | [K/W]      | 0.545                  |

| RTHD3     |            | 0.094                  |

| CTHD0     |            | $5.243 \cdot 10^{-4}$  |

| CTHD1     | [J/K]      | $1.076 \cdot 10^{-3}$  |

| CTHD2     | ] [3/18]   | 0.044                  |

| CTHD3     |            | 2.025                  |

| RGPOW     | $[\Omega]$ | $100 \cdot 10^6$       |

| CRGPOW    | [F]        | 10 · 10 <sup>-12</sup> |

The controlled current source GPOW represents the real power dissipated in the diode. Its efficiency is described by

$$I_{GPOW} = \begin{cases} ABS \left( I_{(VIA)} \cdot V_{(ANODE,CATHODE)} \right) & \text{if } t > 25ns \\ 0 & \text{if } t \leq 25ns \end{cases}$$

(6)

where  $I_{(VIA)}$  is the total current flowing through the diode,  $V_{(ANODE,CATHODE)}$  is the voltage on the diode, whereas ABS is the standard SPICE function denoting the absolute value of any function.

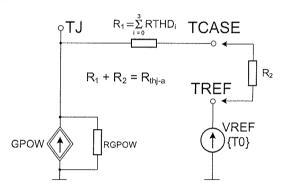

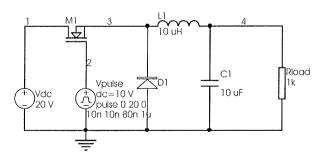

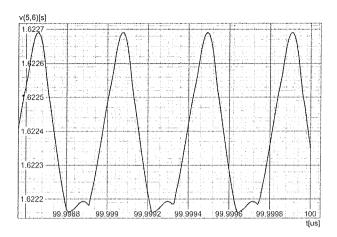

In the case of the analysis at the steady-state the simplified, shown in Fig. 4, thermal network is used. In this figure the resistance  $R_1$  denotes the junction–to–case thermal resistance represented by the sum of  $RTHD_i$  (i = 0÷3) and equal to 4.112 K/W, whereas the resistance  $R_2$  represents the case–to–ambient resistance of the value depending on the case cooling conditions. Note, that the thermal model can be used in d.c. analysis, if the time limitations in Eq.(6) are eliminated.

Fig. 4. The thermal model of the SiC Schottky diode for d.c. analysis

#### 3. The Macromodel Verification

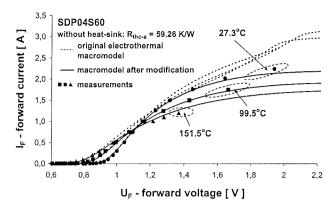

To estimate the correctness of the macromodel described in the early chapter, SPICE simulations of the forward and reverse characteristics of the diode SDP04S60 have been compared to the measurements. The diode has been operated without the heat-sink. The value of the measured thermal resistances  $R_{thc-a}$  is equal to 59.26 K/W.

The results of measurements (points) and SPICE simulations (lines) in the wide temperatures range are shown in Fig. 5 (the forward range) and Fig. 6 (the reverse range), respectively. As seen in Fig. 5, the simulation results based on the original macromodel (the broken lines) differ from the measurements even more than 60 %.

To improve the agreement between simulations and measurements the following modification of the parameter  $\chi$  (existing in Eq.(5)) has been proposed /10/

$$\chi = 1.58 + (35 \cdot 10^{-5} \cdot T^{1}) + (32 \cdot 10^{-7} \cdot T^{2})$$

(7)

After these modifications the considered characteristics obtained both from measurements and SPICE calculations fit well and the error of the current estimation at the given voltage is not greater than a few per cent.

Fig. 5. The forward characteristics of the SDP04S60 diode without the heat-sink

### U<sub>R</sub> - reverse voltage [V]

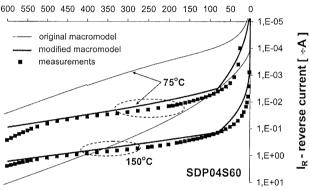

Fig. 6. The reverse characteristics of the SDP04S60 diode

The considered macromodel along with the author's additional modifications presented in Table 3, has also been used for modelling the diode characteristics operating in the reverse range /10,12/. Note, that for the considered two ambient temperature values, different values of the selected parameters are required.

As seen, also in this case a very good agreement between the results of measurements (points) and electrothermal calculations has been obtained. One can notice, that in the considered voltage range the dissipated power in the diode can be omitted. Thus, the obtained characteristics can be treated as the isothermal ones.

Table 3 The macromodel modifications for the SDP04S60 diode operating in the reverse range

|             |                         | Value                                   |                                                             |                             |

|-------------|-------------------------|-----------------------------------------|-------------------------------------------------------------|-----------------------------|

| Pa          | rameter                 | Original                                | 75°C                                                        | 150°C                       |

|             | $\alpha_1$              | 3.8                                     | 2                                                           | 1.75                        |

|             | β                       | 1.49·10 <sup>-8</sup>                   | 2.24.10 <sup>-7</sup>                                       | 1.60·10 <sup>-7</sup>       |

| $\Phi_{LS}$ | <i>V</i> ≤ <i>VPT/5</i> | $q \cdot \sqrt{\beta \cdot EFLD_{(V)}}$ |                                                             | $\frac{EFLD_{(V)}}{(+T_0)}$ |

| 1 20        | V ><br>VPT/5            | $k\cdot (T+T_0)$                        | $\begin{vmatrix} \phi_{LS(VPT/5)} \\ = 10.87 \end{vmatrix}$ | $\phi_{LS(VPT/5)} = 7.55$   |

#### 4. Conclusions

In the paper the electrothermal macromodel of the SiC Schottky diode has been investigated and verified experimentally. As was proved, the original macromodel is of poor accuracy, whereas after the author's modifications the characteristics obtained from measurements and calculations fit very well. Note, that to perform the simulations the value of the thermal resistance from the case to the sourrounding had to be additionally measured.

#### Acknowledgments

This work is supported by the Polish State Committee for Scientific Research in 2005-2006, as a research project No. 3T11B08229.

#### References

- /1/ J.B. Casady, and R.W. Johnson, "Status of Silicon Carbide (SiC) as a Wide-Bandgap Semiconductor for High-Temperature Applications: a Review", Solid-State Electronics, Vol. 39, No. 10, pp. 1409-1422, 1996.

- /2/ http://www.grc.nasa.gov/www.sic/sicreview.html: P.G. Neudeck, "Recent Progress in Silicon Carbide Semiconductor Electronics", 1995.

- /3/ A. Elasser, and T.P. Chow, "Silicon Carbide Benefits and Advantages for Power Electronics Circuits and Systems", Proceedings of the IEEE, Vol. 90, No 6, June 2002.

- /4/ C.M. Johnson, "Recent Progress and Current Issues in SiC Semiconductor Devices for Power Applications", *IEE Proc.-Circ. Dev. Syst.*, Vol. 148, No 2, pp. 101-108, April 2001.

- /5/ J. A. Cooper, and A. Agarwal, "SiC Power-Switching Devices the Second Electronics Revolution?", Proc. of the IEEE, Vol. 90, No 6, pp. 956-968, June 2002.

- /6/ www.ecn.purdue.edu/WBG/DataBank, "Best Reported WBG Power Device Performance", February 2003.

- /7/ Y. Sugawara, D. Takayama, K. Asano, R. Singh, J. Palmour, and T. Hayashi, "12-19kV 4H-SiC Pin Diodes with Low Power Loss", International Symposium on Power Semiconductor Devices & ICs, Osaka 2001.

- /8/ I. Zverev, M. Treu, H. Kapels, O. Hellmund, and R. Rupp, "SiC Schottky Rectifiers: Performance, Reliability and Key Applications", EPE 2001 Conf. Proc., Graz, August 2001.

- /9/ http://www.infineon.com: Psice\_SiC\_L3\_2.zip.

- /10/ J. Zarębski, and J. Dąbrowski, "Simulations of Nonisothermal D.C. Characteristics of the SiC Schottky Diode with the Use of SPICE", Mixed Design of Integrated Circuits and Systems MIXDES, Szczecin, June 2004, pp. 441-444.

- /11/ J. Zarębski, "Modelling, Simulations and Measurements of Electrothermal Course, in Semiconductor Devices and Electronic Circuits" (in Polish), Maritime Academy in Gdynia, 1996.

- /12/ J. Zarębski, and J. Dąbrowski, "Calculations and Measurements of the SiC Schottky Diode", IC-SPETO'04 (in Polish), Nidzica, May 2004, pp. 363-366.

Prof. Janusz Zarębski; M.Sc. Jacek Dąbrowski Gdynia Maritime University, Department of Marine Electronics Morska 83, 81-225 Gdynia, POLAND, Tel. ++48 58 6901599, ++48 58 6901609, fax ++48 58 6217353

E-mail: zarebski@am.gdynia.pl, oakjack@am.gdynia.pl

Prispelo (Arrived): 08. 08. 2006; Sprejeto (Accepted): 08. 09. 2006

### PRIMERJAVA TONSKIH PREDOJAČEVALNIH STOPENJ S POLPREVODNIŠKIMA TRANZISTORJEMA IN ELEKTRONKO

Rudolf Babič, Davorin Osebik

Univerza v Mariboru, Fakulteta za elektrotehniko računalništvo in informatiko, Maribor, Slovenija

Kjučne besede: ojačevalniki, tonski predojačevalniki, frekvenčni spekter, harmonska popačenja, bipolarni tranzistor, tranzistor na poljski učinek, vakuumska elektronka

Izvleček: V tem članku bomo skušali pojasniti dileme, ki se pri glasbenikih, predvsem kitaristih, pojavljajo v zvezi z izbiro ojačevalnikov oziroma ojačevalnih elementov za tonske predojačevalne stopnje. Predvsem je zanimiva primerjava med aktualnimi polprevodniškimi tranzistorji, bipolarnimi in tranzistorji na poljski učinek ter še vedno prisotno elektronko. Osvetlili jo bomo s stališča izmerjenih frekvenčnih spektrov in harmonskih popačenj posameznih ojačevalnih stopenj, da bi s tem nekako potrdili slišne razlike med posameznimi skupinami ojačevalnih elementov. Z merilno opremo, ki smo jo aparaturno sestavili na osnovi osebnega računalnika z zvočno kartico, programsko pa nadgradili s programskim paketom MATLAB, smo potrdili, da se razlike v slišnih lastnostih signala na izhodu posameznih ojačevalnih elementov pokažejo predvsem pri prekrmiljenem delovanju ojačevalne stopnje. Od majhnih, vendar že lepo opaznih razlik v obliki izhodnega frekvenčnega spektra, ki smo jih zasledili že pri majhnih vrednostih skupnih harmonskih popačenj, ki so bila glede na uporabljen ojačevalni element različna z vrednostmi od 1 do 5 odstotkov pri istem vhodnem signalu 50 mV, je postala vsebnost višjih harmonskih komponent v izhodnem signalu ojačevalne stopnje pri 20 odstotni vrednosti skupnih harmonskih popačenj pri elektronki bistveno drugačna od tiste pri vezju z bipolarnim oziroma vezju s tranzistorjem na poljski učinek. Vsebina višjih harmonskih komponent pa skupaj z osnovno harmonsko komponento določa sonorne lastnosti signala in s tem tudi slišne razlike. S tem lahko tudi potrdimo, da je prisotna tesna povezava med električnimi popačenji in zvočno barvitostjo.

# The Comparison of Audio Preamplifier Circuits with Solid State Transistors and Vacuum Tube

Key words: amplifiers, audio preamplifiers, frequency spectrum, harmonic distortions, bipolar junction transistor, field effect transistor, vacuum tube

Abstract: In this article the answer for dilemma which appear, especially between musicians, about the questions what amplifying device is appropriate for audio preamplifier circuits is presented. For this purpose the comparison is made between actual solid state transistors, bipolar junction transistor and field effect transistor versus vacuum tube. The tested preamplifier circuits with component specifications are shown on fig. 4. Although solid state technology overwhelmingly dominates today's world of electronics, vacuum tubes are holding out the small but vibrant area in the creation and reproduction of music. The music is played to be heard by human beings, whose nonlinear ear-brain hearing system are far from fully understood. Since no one knows exactly how to model the human auditory system, no one knows exactly what engineering measurements are appropriate to evaluate the performance of audio equipment. We know that some number of people prefer the sound produced by tube equipments which are found in musical instrument amplifiers (mainly guitar amplifiers), some processing devices used in recording studios and in high-fidelity audio equipments.

Some of the differences in the audio qualities between tubes and transistors have to do with the inherent physical properties of the devices and with the circuit topologies and what components are used with each type of the device. We know already that vacuum tubes have lower total harmonic distortions than bipolar transistor or field effect transistors. The clipping characteristic of tubes are softer, but not too much softer than those of transistors. The feedback is one more thing which tends to make square wave form of the output signal. Thus, the heavy feedback in most solid state designs gives them also worse overload performance.

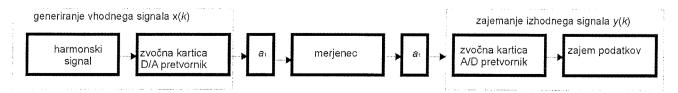

The differences between transistor sound and vacuum tube sound are highlighted thru the frequency spectrum and total harmonic distortion (THD) measurements. We can confirm that differences exist. We made the personal computer based hardware measurement system with MATLAB package for software support. In fig. 1 the block diagram of proposed measurement system is shown. At the input the first block is source of the corresponding input signal, with white noise data base with 1024 samples for calibration and with harmonic signal data base with frequency of 440 Hz. The second block is PC sound card with D/A conversion. The tested amplifier circuit is connected to the measurement system with input and output attenuation circuit. At the output two blocks with PC sound card with A/D data conversion serve as data acquisition structure. The results of frequency spectrum and their graphs are obtained with MATLAB software tool. With our investigations we can confirm, that there is a close parallel here between electronic distortion and musical tone coloration. The frequency of 440 Hz is chosen, because it is typical guitar signal. We observed that the visible differences between both transistors and the tube are present only at severely overloaded signals. At 50 mV typical guitar transducer output signal total harmonic distortion of 1 % for tube amplifier, 1,8% for field effect transistor amplifier and 4,9% for bipolar transistor amplifier are obtained. The differences of the output frequency spectrum are small but noticeable, these graphs are shown in fig. 5, 6 nad 7 and the amplitude values of higher harmonic components are summarized in the table 2. When the higher harmonic distortions, for example THD=20% for crunch sound is applied, the content of higher harmonic components and their amplitudes significantly differ for our preamplifiers. These results are shown in the fig. 9, 10, 11 and are summarized in the table 4. We can see, that the tube has at the same THD the least possible amplitude values of higher harmonic components. This means especially for third harmonic component, which gives to semiconductor preamplifiers a metallic quality of sound. With comparison to all high harmonic components, the main emhasis of tube amplifier is on the second harmonic component. This is also one of the main reasons for sonorous sound of vacuum tube.

#### 1 Uvod

Razprave o kvaliteti reprodukcije zvoka so že od nekdaj vroča tema inženirjev, uporabnikov ter kritikov /1/. Ocene uporabnikov temeljijo zgolj na osebnih izkušnjah in so subjektivne narave. Razmere na trgu pa dejansko kažejo, da je priljubljenost in prodaja ojačevalnikov na elektronke, posebej za kitare, velika, saj se s tem ukvarja kar nekaj podjetij. Zakaj torej polprevodniška tehnologija, ki sicer prevladuje v svetu elektronike, na tem segmentu ni izpodrinila elektronke in ali je mogoče med subjektivnimi ocenami uporabnikov in tehničnimi lastnostmi najti soglasje, sta vprašanji na kateri smo skušali poiskati odgovor. Ker se glasba ustvarja in predvaja za poslušalce in ker še vedno ne poznamo do potankosti modela človekovega slušnega sistema, tudi ne vemo natančno, katere inženirske meritve bi omogočale določitev lastnosti takšnih naprav. Vemo pa, da določena skupina poslušalcev raje posluša zvok tonskih naprav z elektronkami, naj gre za glasbene ojačevalnike, najpogosteje so to spet ojačevalniki za kitaro, studijske snemalne naprave ali preprosto kvalitetne splošne tonske naprave. Razlogi so subjektivne in objektivne narave. Nekatere razlike v kvaliteti zvoka so prav gotovo v fizikalnih razlikah med polprevodniškimi tranzistorji in elektronko ter topologijo ojačevalnega vezja. V splošnem vemo, da imajo polprevodniški ojačevalni elementi številne prednosti, zaradi katerih so v preteklosti v kratkem času na večini področjih izpodrinili elektronke. Prednosti so nesporno v manjših dimenzijah, nižjih delovnih napetostih, cenenosti, dolgi življenjski dobi, višji zgornji frekvenčni meji, skoraj neomejenih možnostih integracije in izdelavi mikroelektronskih vezij. Ostajajo pa še vedno nekatere prednosti elektronk, ki so prisotne prav na tistih področjih kjer so znane slabosti tranzistorjev: temperaturna stabilnost, toplotna obremenitev, odpornost na preobremenitve, manjše tolerance električnih karakteristik, večje dinamično področje, doseganje večjih moči. preprostejša vezja in manjša popačenja. Kako se nekatere od teh prednosti odražajo na slušnih lastnostih, bomo skušali v nadaljevanju ugotoviti s podrobnejšo analizo harmonskih popačenj pri ojačevalnem vezju z bipolarnim tranzistorjem, s tranzistorjem na poljski učinek in z elektronko.

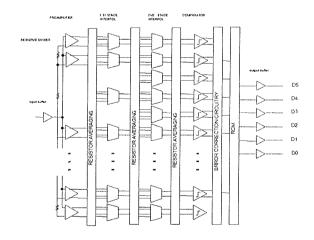

#### 2 Merilni sistem

Za izvajanje meritev harmonskih popačenj in analize frekvenčnih spektrov, s katerimi bi zasledili razlike med posameznimi ojačevalnimi elementi, smo zasnovali in izdelali računalniško podprti merilni sistem /2/, ki smo ga

nadgradili s programskim paketom MATLAB. Blokovno shemo aparaturnega dela merilnega sistema prikazuje slika 1.

Analogni vhodni signal smo z D/A pretvornikom na zvočni kartici osebnega računalnika generirali na osnovi vnaprej pripravljene datoteke vhodnega signala. Na izhodni strani pa smo z A/D pretvornikom na zvočni kartici poskrbeli za zajemanje signala za končno obdelavo s programskim paketom MATLAB. Uporaba zasnovanega sistema je omogočila enostavno računalniško podprto meritev in izračun frekvenčnih spektrov posameznih ojačevalnih vezij. Dosegli smo tudi visoko stopnjo ponovljivosti in primerljivosti rezultatov, saj so bili generirani vzbujevalni signali enaki pri vseh meritvah. Zaradi merjenja frekvenčnih spektrov ojačevalnih vezij z elektronko, tranzistorjem na poljski učinek in bipolarnim tranzistorjem, ki so med seboj zelo različna, smo v merilno progo vključili še dve slabilni vezji  $a_1$  in  $a_2$ , ki služita za prilagoditev posameznega ojačevalnega vezja in za poenotenie merilnih rezultatov.

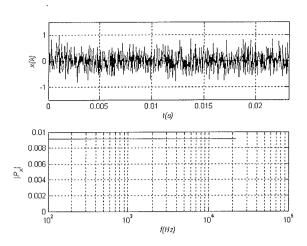

Pred izvedbo meritev ojačevalnih vezij smo merilni sistem umerili z neharmoničnim signalom belega šuma /3/. Signal belega šuma smo generirali na osnovi predhodno pripravljenih vzorcev, ki smo jih izračunali s programskim paketom MATLAB. Beli šum ima konstantno gostoto spektra moči  $P_{\rm X}$ , ki omogoča enostavno meritev amplitudne in fazne karakteristike vezij s pomočjo hitre Fourierjeve transformacije izhodnega signala. Osnovne statistične podatke belega šuma za 1024 vzorcev v periodi podaja tabela 1.

Tabela 1: Osnovni statistični podatki signala belega šuma s 1024 vzorci

Table 1: Basic statistical data for 1024 samples white noise

| Število vzorcev          | 1024                      |

|--------------------------|---------------------------|

| $\overline{\mathcal{X}}$ | 6.1096·10 <sup>-14</sup>  |

| σ                        | 2.9127·10 <sup>-01</sup>  |

| $X_{max}$                | 1.0000                    |

| X <sub>min</sub>         | -8.1697·10 <sup>-01</sup> |

| $P_{\rm x}$              | $9.099010^{-03}$          |

Srednja vrednost  $\bar{x}$  belega šuma gre proti vrednosti nič, amplitudne vrednosti pa so enakomerno razporejene med minimalno  $x_{min}$  in maksimalno  $x_{max}$  vrednost. Časovni potek x(k) in spekter moči  $|P_X(j\omega)|$  prikazuje slika 2.

Slika 1: Blokovna shema merilnega sistema za določitev frekvenčnega spektra

Fig. 1: Block diagram of the frequency spectrum measurement system

Slika 2: Časovni potek signala belega šuma x(k) in spekter moči [P<sub>x</sub>(jω)]

Fig. 2: The time response of white noise signal x(k) and his power spectrum  $|P_X(j\omega)|$

Pri umerjanju smo izhod zvočne kartice osebnega računalnika neposredno povezali z vhodom zvočne kartice in za vhodni signal uporabili vnaprej pripravljeno datoteko 1024 vzorcev belega šuma v eni periodi. Analogno obliko signala belega šuma na vhodu smo najprej generirali z D/A pretvornikom zvočne kartice, potem pa smo ga na izhodu zajemali in vzorčili z A/D pretvornikom iste vzorčne kartice, ga pretvorili v digitalno obliko in ga shranili v izhodno datoteko tipa 'vaw'. V skriptnem jeziku programskega paketa MATLAB smo s pomočjo hitre Fourierjeve transformacije napisali program za izračun frekvenčnega odziva in s tem za analizo ustreznosti odziva merilnega sistema. Rezultate amplitudnega in faznega frekvenčnega odziva merilne sistema na beli šum prikazuje slika 3.

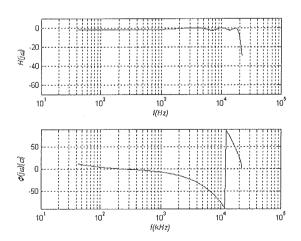

Slika 3: Amplitudni in fazni frekvenčni odziv merilnega sistema

Fig. 3: The amplitude and phase frequency response of measurement system

Iz prikazanega amplitudnega in faznega frekvenčnega odziva merilne proge vidimo, da je amplitudna frekvenčna odvisnost praktično konstantna v področju od 40Hz do 20kHz, zato pa je fazna frekvenčna odvisnost v tem področju precej

nelinearna. Ker pa smo meritve izvajali v frekvenčnem območju od 400 Hz do 3500 Hz, omenjena nelinearnost ni bistveno vplivala na naše merilne rezultate.

#### 3 Rezultati

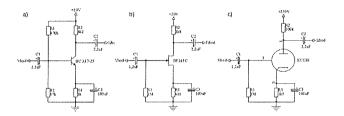

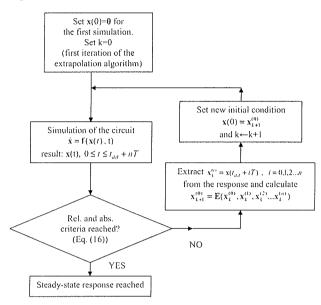

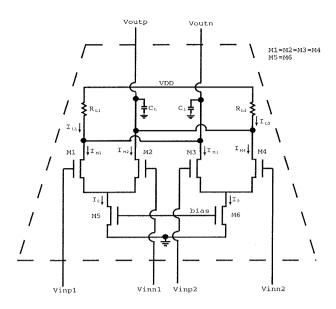

Za analizo popačenj smo izdelali posamezne ojačevalne stopnje, ki so prikazane na sliki 4: predojačevalno vezje z bipolarnim tranzistorjem BC 337 je na sliki 4a, vezje s tranzistorjem na poljski učinek BF 245C na sliki 4b in vezje z elektronko ECC 83 na sliki 4c. Prikazane so tipične konfiguracije vezij z delovanjem ojačevalnega elementa v A razredu, brez negativne povratne vezave in z vrednostmi elementov, ki jih najpogosteje zasledimo pri proizvajalčevih aplikacijah za predojačevalnike. Pri bipolarnem tranzistorju smo uporabili orientacijo s skupnim emitorjem, pri FET tranzistorju orientacijo s skupnim virom in pri predojačevalniku z elektronko orientacijo s skupno katodo. Za gretje triode smo uporabili 12V enosmerno napetost.

Slika 4: Vezja predojačevalnikov: z bipolarnim tranzistorjem (a), s tranzistorjem na poljski učinek (b) in z elektronko (c)

Fig. 4: Preamplifier circuits with: bipolar junction transistor (a), field effect transistor (b) and vacuum tube (c)

Ker so ojačenja posameznih ojačevalnih stopenj med seboj različna, smo za lažjo primerjavo frekvenčnih spektrov s prilagodilno stopnjo  $a_2$  nastavili izhodni nivo signala na OdB.

#### 3.1 Meritve v linearnem režimu delovanja

Pri meritvi frekvenčnega spektra izhodnega signala smo za testni signal uporabili harmonski signal s frekvenco 440 Hz. Uporabljena frekvenca predstavlja reprezentativen ton električne kitare. Amplituda vhodnega signala je znašala 50mV, kar ustreza običajni vrednosti enojnega tonskega odjemnika pri električni kitari. S takšnim krmilnim signalom smo predpostavili delovanje ojačevalnih stopenj v linearnem režimu delovanja.

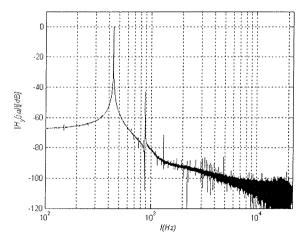

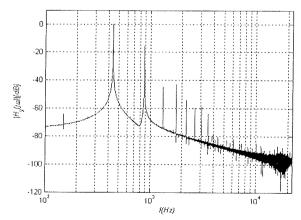

V postopku meritve smo najprej izmerili odzive ojačevalnih stopenj na harmonski vhodni signal in izračunali ter izrisali grafe frekvenčnih spektrov, potem pa še izmerili in izračunali skupna harmonska popačenja. Frekvenčne spektre  $|H_y(j\omega)|$  smo iz zajetih merilnih podatkov izhodnega signala izračunali s pomočjo hitre Fourierjeve transformacije v  $2^{17}$  vzorcih s programskim paketom MATLAB. Dobljeni frekvenčni spektri so prikazani na slikah 5, 6 in 7.

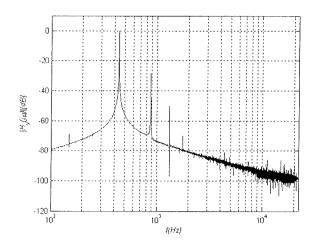

Slika 5: Frekvenčni spekter predojačevalnika z bipolarnim tranzistorjem

Fig. 5: Frequency spectrum of bipolar transistor preamplifier

Slika 6: Frekvenčni spekter predojačevalnika s tranzistorjem na poljski učinek

Fig. 6: Frequency spectrum of field effect transistor preamplifier

Slika 7: Frekvenčni spekter predojačevalnika z elektronko

Fig. 7: Frequency spectrum of vacuum tube preamplifier

S primerjavo posameznih grafov že zasledimo opazne razlike v vsebnosti višjih harmonskih komponent, v njihovem številu in v njihovih amplitudnih vrednostih. Predvsem zasledimo veliko manjši delež tretje harmonske komponente pri elektronki. Z zmanjševanjem vhodnega signala se skupna harmonska popačenja sicer zmanjšujejo, klub temu pa se ohranjajo značilni vzorci frekvenčnih spektrov. Amplitudne vrednosti posameznih višjih harmonskih komponent nam v primerjavi z osnovno harmonsko komponento, ki je postavljena na OdB, prikazuje tabela2.

Tabela 2: Amplitudne vrednosti osnovne in višjih harmonskih komponent pri ojačevalnih stopnjah v linearnem področju delovanja

Table 2: The amplitude values for first and higher harmonic components in preamplifiers in linear region

|                 | harmonska komponenta dB<br>f <sub>e</sub> (kHz) |       |       |       |       |

|-----------------|-------------------------------------------------|-------|-------|-------|-------|

| ojačevalni      | 1.                                              | 2.    | 3.    | 4.    | 5.    |

| element v vezju | 0,440                                           | 0,881 | 1,321 | 1,760 | 2,200 |

| BJT             | 0                                               | -28   | -50,  | -70   | -79   |

| FET             | 0                                               | -38   | -50   | -77   | -80   |

| elektronka      | 0                                               | -43   | -72   | -     | -     |

Skupna harmonska popačenja (THD) smo najprej izmerili s klasičnim merilnikom harmonskih popačenj HM8027 nato pa še izračunali po izvorni definiciji na osnovi izmerjenih višji harmonskih komponent, z izrazom,

$$THD = \frac{\sqrt{\sum_{k=2}^{N} U_{2k}^{2}}}{U_{1}} \cdot 100\%$$

V izrazu za THD je N število upoštevanih višjih harmonskih komponent v izhodnem signalu  $U_{2\mathrm{n}}$  in  $U_{1}$  osnovna harmonska komponenta. Izvorna definicija je natančnejša pri večjih popačenjih, pri popačenjih do 10 % pa ni večjih razlik glede na meritev, kot je prikazano v tabeli 3.

Tabela 3: Skupna harmonska popačenja posameznih predojačevalnih vezij

Table 3: Total harmonic distortion for preamplifier circuits

| ojačevalni<br>element v vezju | meritev | Izračun |

|-------------------------------|---------|---------|

| BJT                           | 4,90%   | 4,99%   |

| FET                           | 1,85%   | 1,78%   |

| elektronka                    | 1%      | 0,90%   |

Zlahka lahko ugotovimo, da so pri bipolarnem tranzistorju prisotna največja skupna harmonska popačenja. Pogojena so z različnimi ojačenji, nelinearnostjo karakteristik, različnim dinamičnim območjem delovanja in posledično z različno vsebnostjo višjih harmonskih komponent.

### 3.2 Meritve v prekrmiljenem režimu delovanja

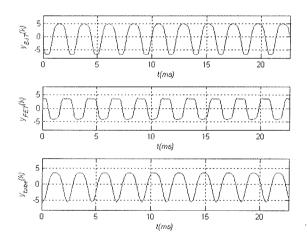

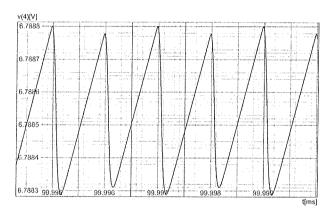

Pri meritvah v prekrmiljenih razmerah smo na vhod posameznih predojačevalnih vezij ponovno pripeljali harmonski signal frekvence 440Hz. S prilagodilno stopnjo  $a_1$  smo na vhodu nastavili nivo signala na takšno vrednost, da je znašala izmerjena vrednost skupnih harmonskih popačenj 20%. To je izkustvena vrednost skupnih harmonskih popačenj /2/ za hreščeč zvočni učinek. Spet smo za poenoten prikaz dobljenih grafov frekvenčnih spektrov s pomočjo prilagodilne stopnjo  $a_2$  nastavili nivo izhodnega signala tako, da je znašala amplituda prve harmonske komponente OdB. Slika 8 prikazuje časovne poteke izhodnih signalov vseh treh predojačevalnikov v prekrmiljenem stanju pri istih skupnih harmonskih popačenjih.

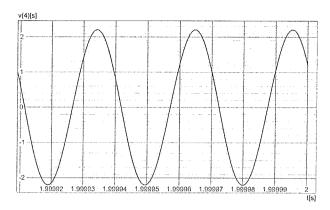

Slika 8: Časovni poteki izhodnih signalov predojačevalnikov z bipolarnim tranzistorjem, y<sub>BJT</sub>, tranzistorjem na poljski učinek, y<sub>FET</sub> in elektronko, y<sub>tube</sub>

Fig. 8: The output waveforms for preamplifiers with BJT,  $y_{BJT}$ , FET,  $y_{FET}$  and tube,  $y_{tube}$

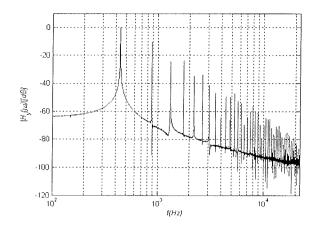

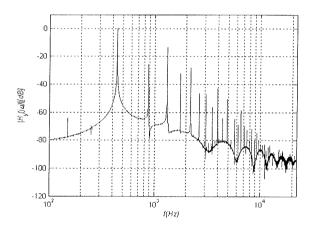

S slike 8 vidimo, da se časovni poteki izhodnih signalov predojačevalnikov pri isti stopnji prekrmiljenja (THD=0,2) med seboj precej razlikujejo. Do razlik pride zaradi različnih vsebnosti višjih harmonskih komponent. To je prikazano na slikah 9, 10 in 11, kjer podajamo frekvenčne spektre vseh treh vezij.

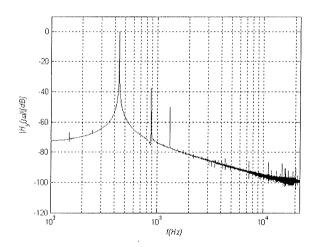

Slika 9: Frekvenčni spekter predojačevalnika z bipolarnim tranzistorjem pri 20% harmonskih popačenjih

Fig. 9: The frequency spectrum of preamplifier with bipolar junction transistor at 20% total harmonic distortion

Slika 10:Frekvenčni spekter predojačevalnika s tranzistorjem na poljski učinek pri 20% skupnih harmonskih popačenjih

Fig. 10: The frequency spectrum of preamplifier with field effect transistor at 20% total harmonic distortion

Slika 11:Frekvenčni spekter predojačevalnika z elektronko pri 20% harmonskih popačenjih

Fig. 11: The frequency spectrum of preamplifier with vacuum tube at 20% harmonic distorsions

Amplitudne vrednosti posameznih višjih harmonskih komponent frekvenčnih spektrov posameznih predojačevalnikov nam v primerjavi z osnovno harmonsko komponento, ki je postavljena na OdB, prikazuje tabela 4.

Tabela 4: Amplitudne vrednosti osnovne in višjih harmonskih komponent pri ojačevalnih stopnjah pri 20% skupnih harmonskih popačenjih

Table 4: The amplitude values for first and higher harmonic components at preamplifiers at THD= 20%

|                               | harmonska komponenta dB<br>f <sub>n</sub> (kHz) |             |             |             |             |             |             |             |

|-------------------------------|-------------------------------------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| ojačevalni<br>element v vezju | 1.<br>0,440                                     | 2.<br>0,881 | 3.<br>1,321 | 4.<br>1,760 | 5.<br>2,200 | 6.<br>2,640 | 7.<br>3,080 | 8.<br>3,520 |

| BJT                           | 0                                               | -10         | -24         | -24         | -35         | -34         | -41         | -47         |

| FET                           | 0                                               | -26         | -14         | -32         | -28         | -47         | -47         | -43         |

| elektronka                    | 0                                               | -16         | -45         | -43         | -54         | -60         | -59         | -64         |

Šele pri prekrmiljenem delovanju posameznih ojačevalnih stopenj pridejo do izraza razlike med bipolarnim tranzistorjem, tranzistorjem na poljski učinek in posebej elektronko. Na zaznavanje zvoka pri človeku v največji meri vpliva uho. Karakteristiko ušesa podaja Fletcher-Munson-ov graf /4/ ki pa kaže le frekvenčno odvisnost ušesa od nivoja glasnosti. Dobljen je na osnovi zaznavanja glasnosti čistih tonov. Povsem drugače je pri signalih, ki so popačeni in polni višjih harmonskih komponent. Med harmonskimi popačenji signala, gledano iz tehničnega vidika in barvitostjo tona, gledano iz glasbenega vidika, lahko po mnenju nekaterih avtorjev potegnemo nekakšne paralele /5/. Osnovna barvna karakteristika tona se skriva v moči višjih harmonskih komponent. Vsaka harmonska komponenta daje svoj karakteristični učinek, če je dominantna. V primeru, da je harmonska komponenta izrazita, spreminja vpliv ostalih komponent. Primer takšnega vpliva je t.i. učinek čebelice, ko zaradi karakteristike ušesa postane neka višja harmonska komponenta zaznavnejša od osnovne in se s tem karakteristični pomen posameznih harmonskih komponent spremeni. S tem se spremeni tudi obarvanost tona.

Višje harmonske komponente lahko razdelimo v dve skupini /5, 6/. Lihe harmonske komponente (tretja in peta), dajeta zamašen in zaprt zvok, medtem ko sode komponente (druga, četrta in šesta) dajejo zborovski in pojoč zvok. Višje harmonske komponente (nad sedmo) dajejo zvoku ostrino. Z glasbenega stališča sode harmonske komponente predstavljajo oktavo, ki jo je težje razločiti od osnovnega tona, vendar pa daje zvoku polnejši karakter. Tretja harmonska komponenta predstavlja kvinto in daje kovinski prizvok, če je njena amplituda dovolj velika. Harmonske komponente, ki dajejo ostrino so z glasbenega vidika nesorodne z osnovnim tonom in kadar so preveč izrazite vnašajo razglašen prizvok.

#### 4 Zaključek

Analiza popačenj ojačevalnih vezij z bipolarnim tranzistorjem, tranzistorjem na poljski učinek in vakuumsko elektronko potrjuje nekatere ugotovitve glasbenikov in njihovih somišljenikov, da so pri posameznih ojačevalnih elementih prisotne slišne razlike.

Z meritvami frekvenčnih spektrov in skupnih harmonskih popačenj smo potrdili razlike v vsebnosti višjih harmonskih komponent pri ojačevalnih stopnjah z različnimi ojačevalnimi elementi in s tem tudi sonorne razlike v izhodnem signalu posameznih ojačevalnikov. Zlahka lahko ugotovimo, da so pri bipolarnem tranzistorju prisotna največja skupna harmonska popačenja v primerjavi s tranzistorjem na poljski učinek in posebej v primerjavi z elektronko. Pogojena so z različnimi ojačenji ojačevalnih elementov, nelinearnostjo karakteristik, različnim dinamičnim območjem in posledično z različno vsebnostjo višjih harmonskih komponent, v njihovem številu in v njihovih amplitudnih vrednostih. Predvsem zasledimo veliko manjši delež tretje harmonske komponente pri elektronki.

Razlike med posameznimi ojačevalnimi elementi pridejo do izraza šele pri prekrmiljenem delovanju ojačevalnih stopenj. Pri 20 odstotni vrednosti skupnih harmonskih popačenj je postala vsebnost višjih harmonskih komponent v izhodnem signalu elektronke bistveno drugačna od tiste pri bipolarnem oziroma tiste pri tranzistorju na poljski učinek. Z glasbenega stališča dajejo sode harmonske komponente polni karakter. Tretja harmonska komponenta daje kovinski prizvok, če je njena amplituda dovolj velika. Harmonske komponente, ki dajejo ostrino so z glasbenega vidika nesorodne z osnovnim tonom in v primeru izrazitih amplitud vnašajo prizvok razglašenosti. Glede na vsebnost višjih harmonskih komponent ima elektronka najbolj poudarjeno drugo harmonsko komponento. Ker ima vse ostale, posebej velja to za tretjo harmonsko komponento, tudi do sto krat manjše, ima z glasbenega vidika najprijetnejši zvok.

Predstavljene in opisane meritve in merilni rezultati običajnemu poslušalcu ne povedo veliko, za strokovnjaka s tehniškega področja pa so praktično edina povratna informacija o tem, kaj se dejansko dogaja v ojačevalniku. Klasični merilnik harmonskih popačenj nam daje le oceno prisotnosti popačenj, ne pa nudi vpogleda v strukturo signala. Z relativno preprostim merilnim sistemom pa nam je uspelo dobiti poleg skupnih harmonskih popačenj tudi vpogled v frekvenčni spekter signala, v vsebnost višjih harmonskih komponent in s tem v razširjeno sliko o signalu, iz katere lahko poiščemo sonorne lastnostih signala. Kako dolgo bo elektronka še uspela zadržati svoje mesto na področju ojačevalnikov za kitaro in profesionalne tonske opreme, je vprašanje časa. Hiter napredek vseh vrst signalnih procesorjev, tudi takšnih posebnih za simulacijo zvočnih lastnosti elektronk, jih bo v bližnji prihodnosti zanesljivo nadomestil in izpodrinil.

#### 5 Literatura

- /1/ E. Barbour, The cool sound of tubes, IEEE Spectrum, aug 1998, 35 (8), page 24-35.

- /2/ F: Širovnik, Predojačevalnik za električno kitaro na elektronke z načrtom oglaševanja preko interneta, Diplomsko delo, Fakulteta za elektrotehniko, računalništvo in informatiko, 2003, 133 strani.

- /3/ Osebik, R. Babič, Adaptivna digitalna sita v strukturi porazdeljene aritmetike, inf MIDEM, sep. 2001, letnik 31, št 3, str. 160-168.

- /4/ Tony Moscal, Sound Check, Hal Leonard, Aug 1, 1994.

- /5/ W. Fearn, Douglas. Why Tubes ? Pro Audio Review, Jan/Feb 1996.

- /6/ Russell O. Hamm, Tubes vs transistors: Is there an audible difference, Journal of the Audio Engineering Society, May 1973.

izr. prof. dr. Rudolf Babič, tel.: (02) 220-7230, e-mail:

rudolf.babic@uni-mb.si

dr. Davorin Osebik, tel (02) 220-7238, e-mail:

davorin.osebik@uni-mb.si

Univerza v Mariboru

Fakulteta za elektrotehniko, računalništvo in

informatiko, Smetanova 17, 2000 Maribor

Tel.: (02) 220 7000, Fax (02) 220 7272

Prispelo (Arrived): 20. 12. 2005; Sprejeto (Accepted): 08. 09. 2006

# VARIATIONS OF COLOR CORRELATED TEMPERATURE OF WHITE LED LIGHT

Mitja Prelovšek, Grega Bizjak

Univerza v Ljubljani, Fakulteta za elektrotehniko, Ljubljana, Slovenia

Key words: Light-emitting diodes, white LED, correlated color temperature CCT, CCT consistency, color rendering index, illumination, solid state lighting sources

Abstract: Correlated color temperature (CCT) variations and low color rendering index (CRI) present many reasons for not using white light-emitting diodes (LEDs) in lighting. In this research color characteristics of light emitted by LEDs were measured on 29 (In)GaN LEDs of 6 different kinds. We found that color characteristics, notably CCT, are significantly dependent on distance from geometrical axis of the LED, of which the ones that do not use light-diffusion layer were more susceptible to CCT variations. Furthermore, variations of color characteristics of LEDs belonging to the same type were significantly higher than the minimum color difference that human eye can notice. The obtained data suggest, that in order to achieve sufficient light quality and color consistency between different white LEDs, diffusion layer use is highly recommended, due to its smoothing effect.

# Razlike v najpodobnejši barvni temperaturi svetlobe belih LED

Kjučne besede: svetleče diode, bele LED, najpodobnejša barvna temperatura CCT, konsistentnost CCT, indeks barvnega videza, razsvetljava, polprevodniški svetlobni viri

Izvleček: Razlike v najpodobnejši barvni temperaturi in indeksu barvnega videza predstavljajo danes glavno oviro pri uporabi belih svetlečih diod (LED) v razsvetljavi. V opisani raziskavi smo izmerili osnovne značilnosti barve svetlobe pri skupaj 29 (In)GaN belih svetlečih diodah šestih različnih tipov. Ugotovili smo, da je najpodobnejša barvna temperatura (CCT) svetlobe LED zelo odvisna od kota opazovanja glede na geometrično os LED. Pojav je najbolj izražen pri LED, ki nimajo nanesenega difuzijskega sloja za razprševanje svetlobe. Ugotovili smo tudi, da so razlike v najpodobnejši barvni temperaturi svetlobe pri LED istega tipa večje, kot je meja zaznavnosti pri človeku. Pridobljeni podatki kažejo, da je za uporabo v razsvetljavi priporočljiva edino uporaba belih LED z difuzijskim slojem, če želimo doseči ustrezno kakovost barve svetlobe.

#### 1 Introduction

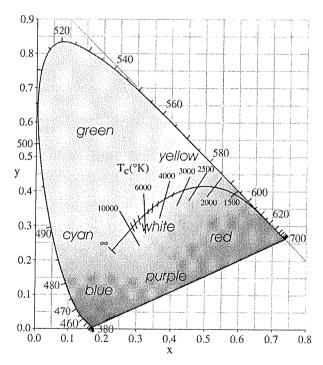

Color temperature is a way of describing the hue of white light. The term color temperature originates from the correlation between temperature of planckian black body and its emission spectrum. For example, planckian body heated to 3000 K radiates white light with reddish hue, while at 6000 K the light adopts a bluish hue. The hues and corresponding temperatures are shown on Fig 1, which presents a CIExy color space, while the Table 1 presents the exact CCT values with corresponding x,y coordinates.

The term correlated color temperature (CCT) is used with light sources, that do not function as black body radiators and therefore, the color of the emitted light does not follow the planckian curve plotted on Fig 1. CCT can be obtained by an algorythm, which moves the color of light source on the planckian curve with a minimum visual change in hue. Obviously this procedure can lead to significant mistakes in color representation, especially if there exists a significant offset of the color of the emitted light from the planckian curve.

The CIExy color space, which is shown on Fig 1, is a much more accurate way of specifying color of light. This method of color representation is therefore the prefered one

Fig 1: CIExy diagram with planckian curve

Table 1: CCT and CIExy coordinates equivalents

| T/K   | x       | y       |

|-------|---------|---------|

| 2000  | 0,52669 | 0,41331 |

| 2353  | 0,49059 | 0,41498 |

| 2500  | 0,47701 | 0,41368 |

| 3077  | 0,43156 | 0,40216 |

| 3333  | 0,41502 | 0,39535 |

| 3636  | 0,39792 | 0,3869  |

| 4000  | 0,38045 | 0,37676 |

| 4444  | 0,36276 | 0,36496 |

| 5000  | 0,3451  | 0,35162 |

| 5714  | 0,32775 | 0,3369  |

| 6667  | 0,31101 | 0,32116 |

| 8000  | 0,29518 | 0,30477 |

| 10000 | 0,28063 | 0,28828 |

| 12500 | 0,27011 | 0,27547 |

| 14286 | 0,26526 | 0,2693  |

| 16667 | 0,2607  | 0,26333 |

| 20000 | 0,25645 | 0,25763 |

| 25000 | 0,25251 | 0,25222 |

when measuring LEDs. The biggest advantage of CIExy color space, however, is accurate representation of the perceived color of light containing various distinct peaks in its spectrum. For example, if there are only red and blue components in the spectrum of incident light, then the perceived color of light will be on the line connecting the red point and blue point in CIExy space. Similarly, when there are three or more components in the spectrum, then the perceived color of light is somewhere inside the geometrical shape, which connects all the points in CIExy space.

The CIExy space has 2 coordinates, which allow representation of every color detectable by human eyes. Coordinate x is roughly proportionate to the amount of red color, while y represents the amount of green.

#### 2 White LEDs

There are three different technologies of producing white light by using LEDs. First and perhaps the most known way of achieving white light is by mixing light of red, green and blue LEDs with appropriate luminances. This mixture of wavelengths is interpreted as white light by our visual system. The advantage of this principle is, that any color in the triangle in CIExy color space, which connects those three primary colors, can be achieved. However, the costs of the installation are often too high, especially when dynamic color changes are not required.

The second principle is based on luminiscence of red, green and blue phosphor coatings, which are placed over near-UV LED chip. The UV light excites the phosphors, which consequently down-shift UV light into three broad peaks in red, green and blue interval of the spectrum. The n-UV LED chip + RGB phosphors is a technology which is still in its infancy, where the efficiency of such n-UV LED chip and wavelength conversion is too low for illumination applications.

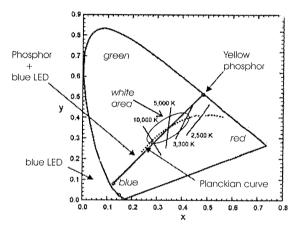

The most widely used white LED technology uses blue LED GaN chips coated with yellow phosphor, which down-shifts part of emitted blue light to yellow wavelengths. The right mixture of yellow and blue spectral components is perceived as white light, which can be seen from Fig 2.

Fig 2: CIExy diagram with line connecting color coordinates of blue LED and yellow phosphor

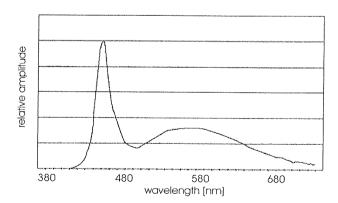

This kind of white LED has only 2 peaks in its spectrum, as shown on Fig 3, and consequently very low color rendering index (CRI).

Fig 3: Spectrum of GaN white LED

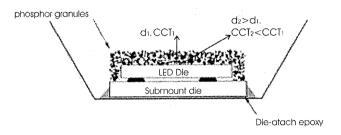

However, low CRI is not the only weakness of this type of white LEDs. The other major disadvantage originates from the fact, that the amount of yellow, which is represented in the spectrum, is directly proportionate to the distance through yellow phosphor, that has to be traversed by the emitted light. Furthermore, since that distance is bigger at larger angles of observation, CCT depends not only on

the thickness of the phosphor coating, but also on the angle of observation as shown on the following figure. Here  $d_1$  and  $d_2$  label distances through phosphor at an arbitrary angle and on the geometrical axis.

Fig 4: GaN white LED structure

CCT variations and dependancies of GaN white LEDs, that are mentioned above, were measured on 3 types of through-hole LEDs, 2 types of high-output LEDs with diffusion layer and 1 type of high-output LED without diffusion layer. The corresponding viewing angles or maximum radiation angles are presented in Table 2, where diodes have been labeled according to their type with TH, HOD or HO, meaning through-hole, high-output diffusion and high-output respectively.

Table 2: measured LEDs

| Label | Viewing angle | Number of LEDs |

|-------|---------------|----------------|

| TH1   | 10°           | 5              |

| TH2   | 15°           | 5              |

| TH3   | 15°           | 5              |

| HOD1  | 110°          | 5              |

| HOD2  | 110°          | 4              |

| НО    | >90°          | 5              |

A typical through-hole, high-output diffusion and high-output LED can be seen on Fig 5, Fig 6 and Fig 7 respectively.

Fig 5: through hole LED

Fig 6: high output LED with diffusion layer positioned on the measurement holder

Fig 7: high output LED

#### 3 Experimental procedures

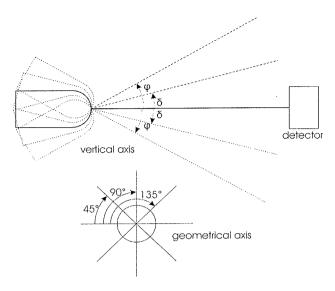

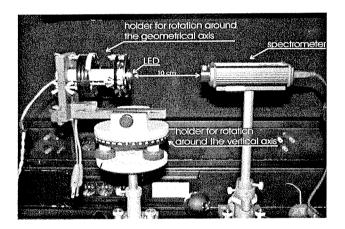

CCT was measured by rotating the LEDs around their vertical and geometrical axis as shown on Fig 8.

LEDs were rotated on two custom-made holders, while the CCT data were measured by a spectrometer, which was positioned 10cm from the LED. Position of the instruments is shown on the following figure.

The rotation around vertical axis was in our experiment limited to 70 degrees, because 70 degrees present the angle where luminous flux is usually cut off in normal white LED applications. That is achieved either by a reflector of some sort or the LED itself includes lenses that limit the viewing angle, which is a standard practice with indicator LEDs. Therefore, we have set the angle  $\phi$  either to the

Fig 8: rotation around geometrical and vertical axes

Fig 9: position of the instruments

viewing angle of the LED or to 70 degrees, if the viewing angle of the LED exceeded 70 degrees. Measurement angle  $\delta$  was approximately one half of  $\phi.$  Measurement angles for corresponding LEDs are shown in Table 3.

Table 3: Measurement angles

| Label | δ   | φ   |

|-------|-----|-----|

| TH1   | 5°  | 10° |

| TH2   | 7°  | 15° |

| TH3   | 7°  | 15° |

| HOD1  | 35° | 70° |

| HOD2  | 35° | 70° |

| НО    | 35° | 70° |

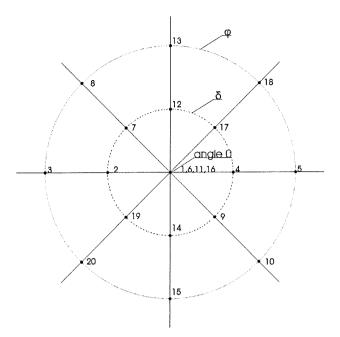

With this procedure we obtained 17 different measurement points, which are shown as black dots in the following figure:

Fig 10: Measurement points

Since all of the measured LEDs showed significant CCT dependance on the measurement angle, it was decided, that we will calculate 3 CCT averages for every type of LED – one for every measurement angle (0,  $\delta$ ,  $\phi$ ). Thus we could evaluate the dependance of CCT on the angle of observation.

As for CCT variance calculations, we wanted to be able to evaluate CCT variations, which can be noticed, when an observer looks at a luminaire which employs a cluster of LEDs. The observer is in this very typical LED application able to notice the maximum and minimum CCT variations of separate LEDs compared to an average CCT of the whole cluster at that specific angle of observation. Therefore we calculated the variances separately for every measurement point (Fig 10). The average used for variance calculation was the average of measurements of the same measurement angle, that the measurement point belonged to. For example: to calculate a variance in point 4 (Fig 10), we used 5 CCT measurements of the point 4 (one for every LED in the group) along with the average of 40 CCT measurements (5-times 8, for 5 LEDs in a group and 8 measurement points at the measurement angle  $\delta$ ).

#### 4 Results and discussion

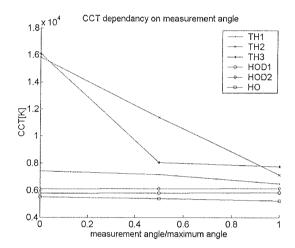

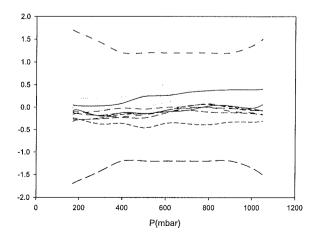

As mentioned above, CCT data of all of the measured LEDs have shown significant dependance on the measurement angle, that is whether the measurement point belonged to 0,  $\delta$  or  $\phi$ . All of the LEDs without light diffusion layer have shown significant decrease in CCT with increasing measurement angle, while the CCT of LEDs with diffusion layer was slightly higher at angle  $\phi$  compared to values at angles 0 or  $\delta$ , as can be seen from Table 4 and Fig 11

Table 4: dependance of CCT from measurement angle

| CCT[K] | angle 0 | angle δ | angle φ |

|--------|---------|---------|---------|

| TH1    | 7427    | 7174    | 6487    |

| TH2    | 15840   | 11358   | 7137    |

| TH3    | 16100   | 8062    | 7756    |

| HOD1   | 5787    | 5805    | 5850    |

| HOD2   | 6118    | 6132    | 6140    |

| НО     | 5509    | 5408    | 5226    |

Fig 11: CCT variation

These data suggest that unevenly spread diffusion layer on LEDs HOD1 and HOD2 caused the reverse dependance of CCT, which can be seen in Fig 11

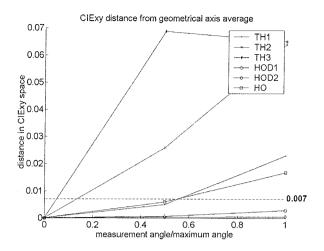

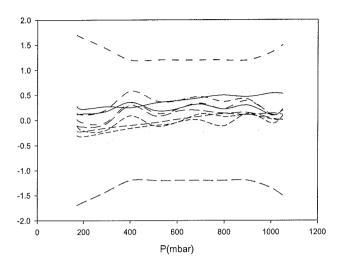

To better evaluate the perceived differences in color of light, however, it is more precise to use the distance between two points in CIExy space as a representation. Table 5 and Fig 12 show distances of CCT averages at  $\delta$  and  $\phi$  to CCT average on geometrical axis. Minimum difference in color, that human visual system can detect, is approximately 50K to 100K [2] in range of daylight variations, which span from 2000K to 6000K. 100K equals approximately 0.007, which is also shown on Fig 12. For an observer it presents a boundary, when he/she notices the change of color of the emitted light.

Table 5: Distances from central average in CIExy space

| Distance in CIExy space | angle δ              | angle φ              |

|-------------------------|----------------------|----------------------|

| TH1                     | $4.98 \cdot 10^{-3}$ | $2.3 \cdot 10^{-2}$  |

| TH2                     | $2.59 \cdot 10^{-2}$ | $6.38 \cdot 10^{-2}$ |

| TH3                     | $6.87 \cdot 10^{-2}$ | $6.5 \cdot 10^{-2}$  |

| HOD1                    | $6.13 \cdot 10^{-4}$ | $2.79 \cdot 10^{-3}$ |

| HOD2                    | $2.95 \cdot 10^{-4}$ | $4.75 \cdot 10^{-4}$ |

| НО                      | $5.96 \cdot 10^{-3}$ | $1.68 \cdot 10^{-2}$ |

Fig 12: CCT variation shown as distance in CIExy space

It can be observed, that LEDs, which use diffusion layer show the best performance in terms of angular stability of CCT. Furthermore, these types of LEDs are the only ones, that remain below the minimum noticeable distance in CIExy space, regardless of the measurement angle. It is thought, that use of diffusion layer with GaN+yellow phosphor white LEDs has positive effect on angular stability of CCT.

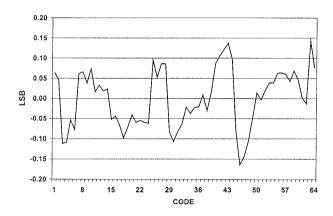

There is, however, another obstacle, which must be dealt with, when using white LEDs and these are differences in light color between different LEDs. We calculated 17 variances, one for every measurement point, for each type of LEDs, as explained in chapter 3. The maximum variances at each angle are shown in Table 6 and Fig 13.

Table 6: Maximum variances at measurement angles

| Maximum variances | angle 0                 | angle δ                | angle φ               |

|-------------------|-------------------------|------------------------|-----------------------|

| THI               | 9.5·10 <sup>-3</sup>    | 1.26·10 <sup>-2</sup>  | 1.99·10 <sup>-2</sup> |

| TH2               | 2.35 · 10 <sup>-2</sup> | 2.7 · 10 <sup>-2</sup> | 1.10-2                |

| TH3               | 1.73 · 10               | 2.8 · 10 <sup>-2</sup> | 2.28 · 10 - 2         |

| HOD1              | 4.9·10 <sup>-3</sup>    | 5.10-3                 | 5.8 · 10 - 3          |

| HOD2              | 2.4 · 10 <sup>-3</sup>  | 2.99 · 10 - 3          | 9.10-3                |

| НО                | 7.98·10 <sup>-3</sup>   | 7.9·10 <sup>-3</sup>   | 8.18 · 10 - 3         |

Again it can be seen, that HOD1 and HOD2 show the best performance, as they are in general always below the noticeable distance in CIExy space. This can be explained with luminance distribution of GaN white LEDs. The point of the highest luminance, which is called the optical axis of the LED, corresponds with the point of the highest CCT. This is because yellow phosphor can down-shift only a limited amount of light. However, optical axis does not, in general, correspond with geometrical axis of the LED and therefore the point of highest CCT is very rarely positioned on the geometrical axis of the LED itself. As the positioning of the LEDs in our experiment did not reflect the direc-

Fig 13: Maximum variances shown as distance in CIExy space

tion of the optical axes in any way, it is suggested, that these position variations of the optical axes are the origin of the variances of LEDs without diffusion layer shown in Fig 13. The advantage of using diffusion layers regarding the optical axes problem mentioned above is, that it smooths out the CCT gradient of the LED and consequently makes position variations of the optical axes less noticeable.

#### 5 Conclusion

Considering the fact, that LEDs without diffusion layer showed poor performance in terms of CCT variations, it is thought, that the prevailent technology of manufacturing white LEDs today is not capable of enabling a widespread use of white LEDs in illumination. However, use of diffusion layers on LEDs can greatly improve their characteristics, especially in terms of angular stability of CCT.

#### 6 References

- /1./ M. Prelovšek, Barvne značilnosti svetlobe belih svetlečih diod, FERLJ, 2006

- /2./ D. A. Steigerwald, Illumination with solid state lighting technology, IEEE, Vol. 8, No. 2, str. 310-320, Marec/April 2002

- /3./ D. A. Kerr, Color temperature, PE, Vol. 4, November 2005

- /4./ http://www.fho-emden.de/~hoffmann/coltemp18102003.pdf

- /5./ J. Furlan, Osnove polprevodniških elementov, Tehniška založba Slovenije, 2002

- /6./ F. Smole, Fotonski polprevodniški elementi, Založba FE in FRI, 2001

- /7./ E. F. Schubert, Light-emitting diodes, Cambridge, 2003

- /8./ J.K.Sheu, White-light emission from near UV InGaN-GaN LED chip precoated with blue/green/red phosphors, IEEE Photonics technology letters, Vol. 15, No. 1, str 18-20, januar 2003

- /9./ CIE technical report 127-1997, Measurement of LEDs, 1997

Mitja Prelovšek u.d.i.e. Zarnikova 11, 1000 Ljubljana Tel: 040298550

doc dr Grega Bizjak u.d.i.e. Univerza v LjubljaniFakulteta za elektrotehniko Tržaška 25, 1000 Ljubljana Tel: 014768446 Email: grega.bizjak@fe.uni-lj.si

Prispelo (Arrived): 21. 08. 2006; Sprejeto (Accepted): 08. 09. 2006

# APPLICATION OF EXTRAPOLATION ALGORITHMS IN NONLINEAR CIRCUIT SIMULATION AND OPTIMIZATION WITH SPICE OPUS

Borut Wagner, Árpád Bűrmen, Janez Puhan, Sašo Tomažič, Tadej Tuma University of Ljubljana, Faculty of Electrical Engineering, Ljubljana, Slovenia

Key words: extrapolation algorithms, circuit simulation, circuit optimization, integrated circuit design, SPICE.

Abstract: In this paper the extrapolation algorithms for vector sequence acceleration are presented. Four extrapolation algorithms are described and their application to circuit simulation is discussed. Steady state evaluation times are compared for the presented extrapolation algorithms and the direct method on real-world test circuits. Results show that the most appropriate extrapolation algorithm for evaluating the steady state of a circuit is the epsilon algorithm. The epsilon algorithm was implemented in SPICE OPUS circuit simulator. The implemented epsilon algorithm was used for optimizing the steady-state response of a test circuit. The accelerated evaluation makes the optimization of steady-state response possible.

# Uporaba ekstrapolacijskih postopkov pri simulaciji in optimizaciji nelinearnih vezij s programskim paketom SPICE OPUS

Kjučne besede: ekstrapolacijski postopki, simulacija električnih vezij, optimizacija električnih vezij, načrtovanje integriranih vezij, SPICE.

Izvleček: V članku so predstavljeni ekstrapolacijski postopki, ki se uporabljajo za pospeševanje konvergence zaporedij. Opisani so štirje postopki in njihov način uporabe pri simulaciji električnih vezij. Podana je primerjava časov za računanje stacionarnega stanja testnih električnih vezij brez in z uporabo ekstrapolacijskih postopkov. Za implementacijo v programski paket SPICE OPUS je bil izbran epsilon algoritem, ki se je izkazal za najbolj primernega. Postopek je bil uporabljen tudi pri optimizaciji testnega vezja. Zaradi hitrejšega izračuna samega stacionarnega stanja se je pohitril tudi celoten postopek optimizacije stacionarnega stanja in postal primeren za praktično uporabo.

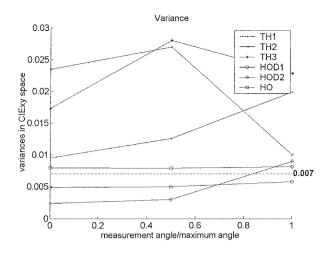

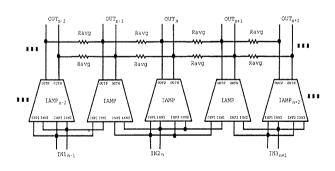

#### 1 Introduction

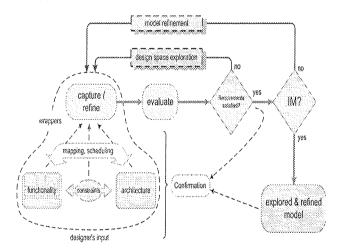

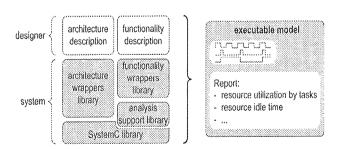

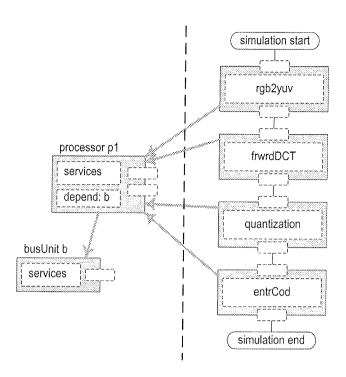

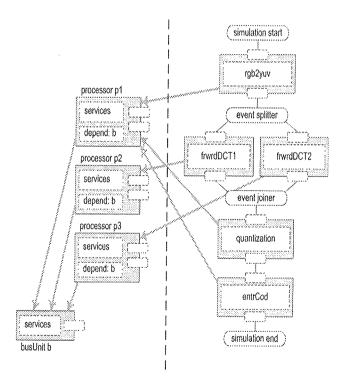

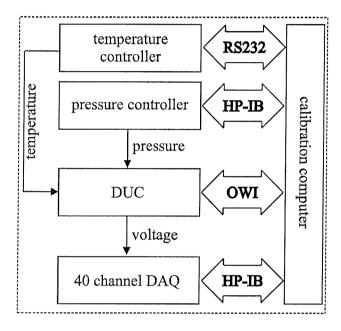

Extrapolation algorithms for vector sequences /1,2,3,4/ are used for accelerating sequences that converge slow-ly. The limit of a sequence can be calculated efficiently by evaluating only a few terms of the sequence without the explicit knowledge of the sequence generator. Using an extrapolation algorithm and only few terms of the sequence, a new initial term of the sequence can be calculated. With the new initial term, further terms of the sequence are evaluated by the sequence generator. The procedure is iterated until the differences between consequent terms of the sequence are small enough to assume that we are close to the limit of the sequence.