# Informacije MIDEM

Journal of Microelectronics, **Electronic Components and Materials** Vol. 50, No. 2(2020), June 2020

Revija za mikroelektroniko, elektronske sestavne dele in materiale letnik 50, številka 2(2020), Junij 2020

# Informacije MIDEM 2-2020 Journal of Microelectronics, Electronic Components and Materials

#### VOLUME 50, NO. 2(174), LJUBLJANA, JUNE 2020 | LETNIK 50, NO. 2(174), LJUBLJANA, JUNIJ 2020

Published quarterly (March, June, September, December) by Society for Microelectronics, Electronic Components and Materials - MIDEM. Copyright © 2020. All rights reserved. | Revija izhaja trimesečno (marec, junij, september, december). Izdaja Strokovno društvo za mikroelektroniko, elektronske sestavne dele in materiale – Društvo MIDEM. Copyright © 2020. Vse pravice pridržane.

#### Editor in Chief | Glavni in odgovorni urednik

Marko Topič, University of Ljubljana (UL), Faculty of Electrical Engineering, Slovenia

#### Editor of Electronic Edition | Urednik elektronske izdaje

Kristijan Brecl, UL, Faculty of Electrical Engineering, Slovenia

#### Associate Editors | Odgovorni področni uredniki

Vanja Ambrožič, UL, Faculty of Electrical Engineering, Slovenia Arpad Bürmen, UL, Faculty of Electrical Engineering, Slovenia Danjela Kuščer Hrovatin, Jožef Stefan Institute, Slovenia Franc Smole, UL, Faculty of Electrical Engineering, Slovenia Matjaž Vidmar, UL, Faculty of Electrical Engineering, Slovenia

#### Editorial Board | Uredniški odbor

Mohamed Akil, ESIEE PARIS, France Giuseppe Buja, University of Padova, Italy Gian-Franco Dalla Betta, University of Trento, Italy Martyn Fice, University College London, United Kingdom Ciprian Iliescu, Institute of Bioengineering and Nanotechnology, A\*STAR, Singapore Marc Lethiecq, University of Tours, France Teresa Orlowska-Kowalska, Wroclaw University of Technology, Poland Luca Palmieri, University of Padova, Italy Goran Stojanović, University of Novi Sad, Serbia

#### International Advisory Board | Časopisni svet

Janez Trontelj, UL, Faculty of Electrical Engineering, Slovenia - Chairman Cor Claeys, IMEC, Leuven, Belgium Denis Đonlagić, University of Maribor, Faculty of Elec. Eng. and Computer Science, Slovenia Zvonko Fazarinc, CIS, Stanford University, Stanford, USA Leszek J. Golonka, Technical University Wroclaw, Wroclaw, Poland Jean-Marie Haussonne, EIC-LUŚAC, Octeville, France Barbara Malič, Jožef Stefan Institute, Slovenia Miran Mozetič, Jožef Stefan Institute, Slovenia Stane Pejovnik, UL, Faculty of Chemistry and Chemical Technology, Slovenia Giorgio Pignatel, University of Perugia, Italy Giovanni Soncini, University of Trento, Trento, Italy Iztok Šorli, MIKROIKS d.o.o., Ljubljana, Slovenia Hong Wang, Xi´an Jiaotong University, China

#### Headquarters | Naslov uredništva

Uredništvo Informacije MIDEM MIDEM pri MIKROIKS Stegne 11, 1521 Ljubljana, Slovenia T. +386 (0)1 513 37 68 F. + 386 (0)1 513 37 71 E. info@midem-drustvo.si www.midem-drustvo.si

Annual subscription rate is 160 EUR, separate issue is 40 EUR. MIDEM members and Society sponsors receive current issues for free. Scientific Council for Technical Sciences of Slovenian Research Agency has recognized Informacije MIDEM as scientific Journal for microelectronics, electronic components and materials. Publishing of the Journal is cofinanced by Slovenian Research Agency and by Society sponsors. Scientific and professional papers published in the journal are indexed and abstracted in COBISS and INSPEC databases. The Journal is indexed by ISI® for Sci Search®, Research Alert® and Material Science Citation Index™. |

Letna naročnina je 160 EUR, cena posamezne številke pa 40 EUR. Člani in sponzorji MIDEM prejemajo posamezne številke brezplačno. Znanstveni svet za tehnične vede je podal pozitivno mnenje o reviji kot znanstveno-strokovni reviji za mikroelektroniko, elektronske sestavne dele in materiale. Izdajo revije sofinancirajo ARRS in sponzorji društva. Znanstveno-strokovne prispevke objavljene v Informacijah MIDEM zajemamo v podatkovne baze COBISS in INSPEC. Prispevke iz revije zajema ISI® v naslednje svoje produkte: Sci Search®, Research Alert® in Materials Science Citation Index™.

## Content | Vsebina

|                                                                                                                                                                                                                                                                     |     | T + + × × 1 1 +                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Original scientific papers                                                                                                                                                                                                                                          |     | Izvirni znanstveni članki                                                                                                                                                                                                                                           |

| E. Sekar, S. Palaniswami:<br>Hardware Implementation of Residue Multipliers<br>based Signed RNS Processor for Cryptosystems                                                                                                                                         | 71  | E. Sekar, S. Palaniswami:<br>Strojna implementacija množilnikov ostankov na<br>osnovi predznačenega RNS procesorja za sisteme<br>kriptiranja                                                                                                                        |

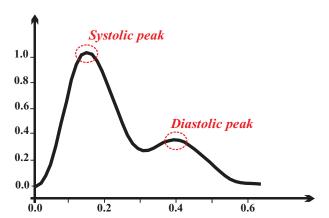

| A. Abolhasani, M. Mousazadeh, A. Khoei:<br>Real-time, Cuff-less and Non-invasive<br>Blood Pressure Monitoring                                                                                                                                                       | 87  | A. Abolhasani, M. Mousazadeh, A. Khoei:<br>Neinvazivno merjenje krvnega tlaka v realnem<br>času brez uporabe manšete                                                                                                                                                |

| M. A. S. Bhuiyan, Z. Fan, Y. J. Leem, L. Y. Lee, M. B. I. Reaz, T. I. Badal, K. N. B. Minhad: CMOS series-shunt single-pole double-throw transmit/receive switch and low noise amplifier design for internet of things based radio frequency identification devices | 105 | M. A. S. Bhuiyan, Z. Fan, Y. J. Leem, L. Y. Lee,<br>M. B. I. Reaz, T. I. Badal, K. N. B. Minhad:<br>Enopolno menjalno oddajno/sprejemno CMOS<br>uporovno stikalo in nizkošumen ojačevalnik za<br>internet stvari identifikacijske elemente na radijski<br>frekvenci |

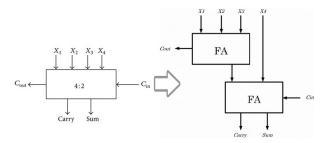

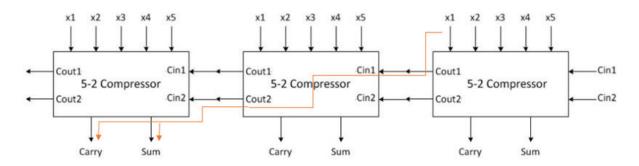

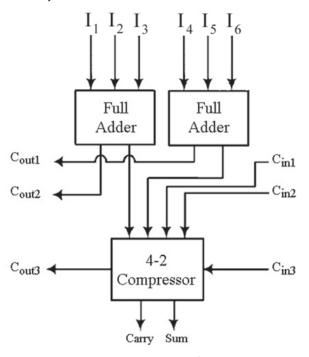

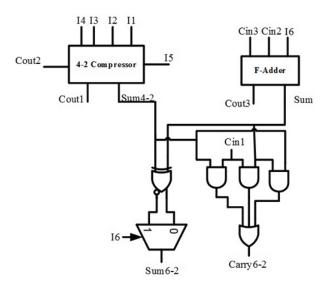

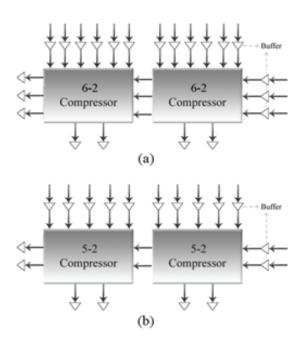

| A. Rahnamaei:<br>CMOS High-Performance 5-2 and 6-2 Compressors<br>for High-Speed Parallel Multipliers                                                                                                                                                               | 115 | A. Rahnamaei:<br>Visoko učinkovit CMOS 5-2 in 6-2 kodirnik za<br>vzporedne množilnike velikih hitrosti                                                                                                                                                              |

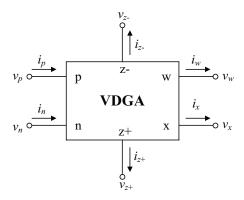

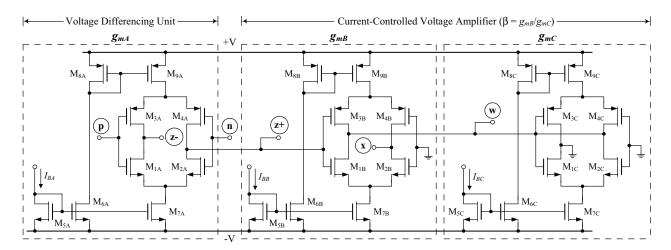

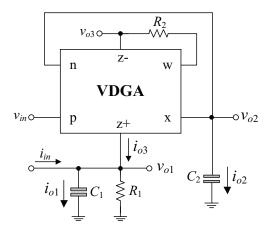

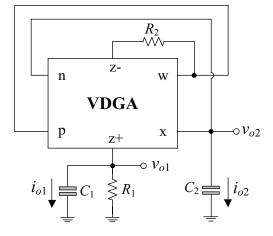

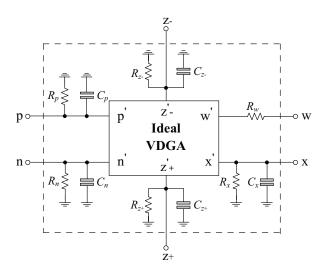

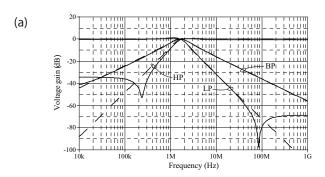

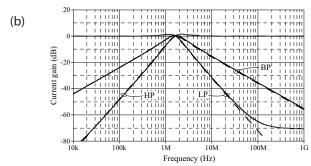

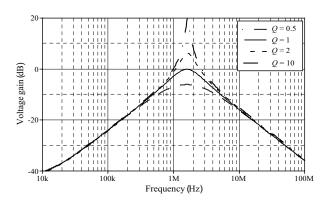

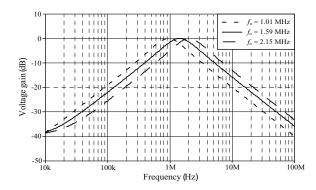

| W. Tangsrirat, T. Pukkalanun, O. Channumsin:<br>Single VDGA-Based Dual-Mode Multifunction<br>Biquadratic Filter and Quadrature<br>Sinusoidal Oscillator                                                                                                             | 125 | W. Tangsrirat, T. Pukkalanun, O. Channumsin:<br>Enojen multifunkcijski bi-kvadratičen filter na<br>osnovi VDGA in sinusni kvadrantni oscilator                                                                                                                      |

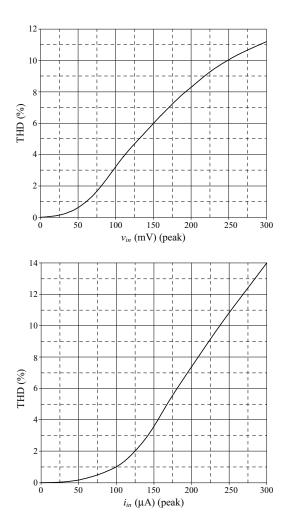

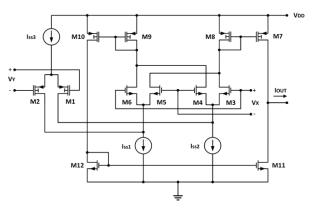

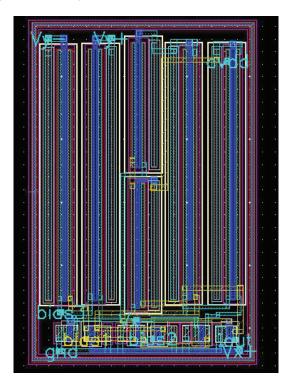

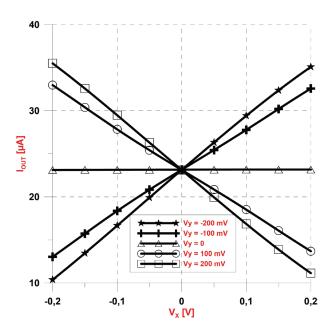

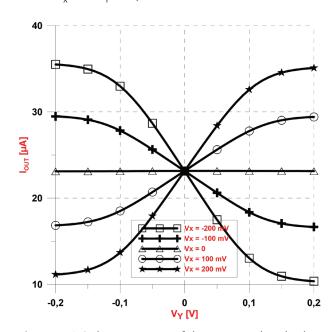

| M. E. Başak, E. Özer, F. Kaçar, D. Özenli:<br>DTMOS Based High Bandwidth Four-Quadrant<br>Analog Multiplier                                                                                                                                                         | 137 | M. E. Başak, E. Özer, F. Kaçar, D. Özenli:<br>Štiri-kvadranten širokopasovni množilnik na osnovi<br>DTMOS                                                                                                                                                           |

| In memoriam<br>Emeritus Prof. Dr. Jože Furlan                                                                                                                                                                                                                       | 147 | In memoriam<br>Zaslužnemu profesorju dr. Jožetu Furlanu                                                                                                                                                                                                             |

| Front page:<br>Magnetic image sensor ASIC (RLS d.o.o.)                                                                                                                                                                                                              |     | Naslovnica:<br>Magnetni slikovni sensor ASIC (RLS d.o.o.)                                                                                                                                                                                                           |

https://doi.org/10.33180/InfMIDEM2020.201

### Hardware Implementation of Residue Multipliers based Signed RNS Processor for Cryptosystems

Elango Sekar, Sampath Palaniswami

Department of Electronics and Communication Engineering, Bannari Amman Institute of Technology, Erode, Tamil Nadu, India

**Abstract:** The Residue Number System (RNS) characterize large integer numbers into smaller residues using moduli sets to enhance the performance of digital cryptosystems. A parallel Signed Residue Multiplication (SRM) algorithm, VLSI parallel array architecture for balanced (2<sup>n</sup>-1, 2<sup>n</sup>, 2<sup>n</sup>+1) and unbalanced (2<sup>k</sup>-1, 2<sup>k</sup>, 2<sup>k</sup>+1) word-length moduli are proposed which in turn are capable of handling signed input numbers. Balanced 2<sup>n</sup>-1 SRM is used as a reference to design an unbalanced 2<sup>k</sup>-1 and 2<sup>k</sup>+1. The synthesized results show that the proposed 2<sup>n</sup>-1 SRM architecture achieves 17% of the area, 26% of speed, and 24% of Power Delay Product (PDP) improvement compared to the Modified Booth Encoded (MBE) architectures discussed in the review of the literature. The proposed 2<sup>n</sup>+1 SRM architecture achieves 23% of the area, 20% of speed, and 22% of PDP improvement compared to recent counterparts. There is a significant improvement in the results due to the fully parallel coarsely grained approach adopted for the design, which is hardly attempted for signed numbers using array architectures. Finally, the proposed SRM modules are used to design {2<sup>n</sup>-1, 2<sup>n</sup>, 2<sup>n</sup>+1} special moduli set based RNS processor, and the real-time verification is performed on Zynq (XC7Z020CLG484-1) Field Programmable Gate Array (FPGA).

Keywords: signed modulo multiplication; Very Large Scale Integration (VLSI); FPGA; computer arithmetic; RNS

# Strojna implementacija množilnikov ostankov na osnovi predznačenega RNS procesorja za sisteme kriptiranja

**Izvleček:** Številski sistem ostankov velike celoštevilske cifre v manjše ostanke na osnovi setov modulov za povečanje učinkovitosti sistemov kriptiranja. Predlagan je algoritem vzporednega množenja predznačenih ostankov (SRM) v VLSI paralelni arhitekturi za uravnotežen (2<sup>n</sup>-1, 2<sup>n</sup>, 2<sup>n</sup>+1) in neuravnotežen (2<sup>k</sup>-1, 2<sup>k</sup>, 2<sup>k</sup>+1) modul dolžine besede. Uravnotežen SRM je uporabljen kot referenca za načrtovanje neuravnoteženega algoritma. Rezultati kažejo, da predlagana arhitektura zajema 17% prostora, 26% hitrosti in 22% izboljšanost PDP glede na trenutne arhitekture. Izboljšava je dosežena na osnovi paralelnega načrtovanja. Verifikacija v realnem času je izvedena na Zynq FPGA.

Ključne besede: predznačeno množenjem odulov; VLSI; FPGA; računalniška arithmetika; RNS

#### 1 Introduction

In cloud computing and the Internet of Things (IoT), data security is one of the major concerns for service providers. Therefore a dedicated hardware cryptography support is needed for modern electronic devices [1],[2],[3][4][5]. In recent years, Elliptic Curve Cryptography (ECC) [6] has received scientific interest as it

ensures more security through hard underlying mathematical problems. It leads to an increase in the length of the key, and as a result, performing faster arithmetic operations on larger integers have become the bottleneck problem. RNS based arithmetic operation [7,8] is a solution through which residue multiplication has become the heart of computation architecture. The natu-

$<sup>* \</sup>textit{Corresponding Author's e-mail: elangos@bitsathy.ac.in}\\$

ral defense offered by RNS against attacks is another reason for the selection of residue arithmetic as the prime candidate in cryptosystems [9,10].

Similarly to the above operation, modular exponentiation [11] is a time-critical operation that is widely used in cryptographic algorithms like RSA. The modular exponentiation operation is performed in the form of residue multiplication. Therefore, the employment of efficient high-speed residue multiplication is vital in public-key encryption and decryption.

Typical hardware implementation of the RNS based application is dependent on the chosen moduli set. The selection of RNS Moduli [12] and the width of the residue decide the efficiency and performance of the cryptosystems. A {2<sup>n</sup>-1,2<sup>n</sup>,2<sup>n</sup>+1} special moduli set representation is a pairwise relatively co-prime standard RNS. These moduli set has a unique advantage in which two or more numbers do not have the same representation. Special moduli set shows better representational efficiency [12] compared to that of other moduli set and also maintains a good balance between the different moduli in a given moduli-set. Based on the number of bits used to represent the input, moduli and residue output are classified into balanced and unbalanced word-length moduli multiplication [13] [14].

Modified Booth Encoded (MBE) modulo multiplication scheme is relatively faster and can handle both signed, and unsigned numbers, the researcher's attention turned towards it, and many modifications of the same are reported in recent years [15,16,17,18,19,20]. The residue multipliers based on diminished-1 input representation in array and bit pair recoding booth algorithm are seen in [16,17,21]. Based on the conducted survey, it is evident that there is no work based on a signed array modulo multiplication scheme reported in the literature. The reasons for the above could be based on the complexity in handling the Partial Product (PP) and poor speed performance. This is one of the reasons that have highly motivated us to attempt a proposal on an array-based high-speed area-efficient parallel SRM module for RNS. In this work, the high-speed performance is achieved by a new multiplication methodology incorporating parallelism in PP generation and addition process.

Six significant contributions for this work include (i) an SRM algorithm for 2<sup>n</sup>-1, 2<sup>n</sup>+1 and 2<sup>n</sup> balanced word-length moduli (ii) an SRM for 2<sup>k</sup>-1, 2<sup>k</sup>+1 and 2<sup>k</sup> unbalanced word – length moduli (iii) Mathematical modeling of SRM algorithm for each moduli (iv) VLSI characterization of proposed SRM algorithm in terms of high-speed area-efficient Carry Save Adder (CSA) architecture and very high-speed Han Carlson parallel

prefix-based SRM array architecture (v) Functional verification of the proposed modules in FPGA and synthesis in ASIC (vi) Design of RNS Processor to demonstrate the effectiveness of the proposed algorithm.

The paper is structured as follows: In Section 2, the related works connected to residue multipliers with various moduli sets performance are analyzed. In Section 3, characteristic equation, algorithm, and VLSI architecture are presented for both balanced (2<sup>n</sup>-1, 2<sup>n</sup>, 2<sup>n</sup>+1) and unbalanced (2<sup>k</sup>-1, 2<sup>k</sup>, 2<sup>k</sup>+1) word-length moduli. The design of the RNS processor is given in section 4. In section 5, Synthesis results, performance analysis, and RNS processor implementation are presented. The conclusion for the proposed work is drawn in section 6.

#### 2 Review of Existing Work

An MBE based 2<sup>n</sup>-1 multiplication module to reduce the number of PPs is presented in [22]. The results show a significant improvement in area and delay. However, they fail to address power consumption. A radix-8 booth encoded RNS 2<sup>n</sup>-1 multiplier [14] using unbalanced word length of moduli supporting sizeable dynamic range with adaptable delay to achieve less area and power consumption is presented. The same authors have designed a radix-8 2<sup>n</sup>-1 & 2<sup>n</sup>+1 multiplier with a balanced word length of moduli in [18] using various modulo properties. The author claims that less area and power are achieved by using CSA in [14] and parallel prefix adders in [18] for efficient addition operations with a slight increase in delay for lower bit width. Improved booth selector and encoder architecture consist of MUX, and the EXOR gate for the 2<sup>n</sup>-1 MBE multiplication algorithm is presented in [23]. The architecture improves the speed performance and efficiency, but the introduction of MUX in selector architecture leads to a slight increase in area requirement, and also power consumption is not discussed.

A compact ordinary array structure [15] based 2<sup>n</sup>+1 multiplication scheme by grouping the PPs and modify the correction bit are presented. The PP is reduced by the CSA tree, and the final carry propagation addition is carried out by prefix structure in order to achieve better area and delay performance in which the power consumption is not discussed. By introducing a new PP formation scheme, a binary-weighted representation based modulo 2<sup>n</sup>+1 multiplier is presented in [19] and is extended to implement a multiply-add unit. The authors have achieved less area and power consumption with similar delay performance compared to [15]. A radix-4 MBE architecture with a diminished-1 input representation and dadda tree reduction scheme, which

can handle zero operands with better speed and area, is discussed in [16]. A compressor structure is introduced in [24] for PP reduction. This work achieves less power, delay, and consumes less area compared to [15].

A hybrid input representation approach with a radix-4 booth encoding scheme utilizing one binary-weighted operand and diminished-1 input representation for the other operand is explained in [17]. The architecture supports both odd and even value of n. The authors have achieved a compact area with an enhanced speed compared to the existing multipliers. The radix-8 booth encoded 2n+1 multiplier for balanced word length moduli is designed in [18] using hard multiple generators, bias, and adders. The authors claim that the area and power reduction is accomplished compared to radix-4 and array type multiplier. However, there is an increase in operation time. In [20], the authors have improved the hard multiple generator method with a minimum number of bias terms compared to [18]. Two novel methods to increase the performance and to improve the efficiency of the radix-8 modulo 2n+1 multiplier are explained in [20]. The first method significantly reduces the amount of bias, and the second one is new hard multiple generators based on a parallel-prefix structure computes carry only for odd positions. These schemes result in a lightweight parallel-prefix adder for the computation of triple the number with significant area-saving and improved fan-out. It achieves less area and power compared to the radix-8 booth multiplier [18]. There is an increase in HMG delay compared to [18] and almost maintains the same delay performance for multiplier operation compared to [18].

The problem in MBE based architecture is that it requires an efficient booth selector and encoder compared to the array-based architectures. The former scheme reduces the number of PPs and improves speed performance. However, it invites additional hardware costs during implementation. Our proposed work is an entirely different approach compared to [18], [20] designed to address the above issues. In the proposed approach, split array type architecture is considered for implementing the 2n+1 operation, which occupies less area compared to the MBE scheme. Array architecture is a non-encoded architecture compared to the booth, so it does not require hard multiples for processing the PPs. The problem of an increased number of PPs in an array is addressed in the proposed scheme by splitting array structure into four segments, and full parallelism is maintained in PP additions also. The parallelism in the architecture ensures improved speed by maintaining the area advantage of the general array structure. The handling of signed numbers in array architecture is another reason for which the array scheme is less explored for data processing applications. The representation of signed numbers is addressed in the proposed architecture using appropriate constants.

#### 3 Proposed Work

#### 3.1 Proposed balanced word-length SRM

In balanced word-length modulo multiplication, the number of bits required representing the input, moduli, and output bits are summarized in Table 1. The type mentioned above of multiplication called balanced residue multiplication as it maintains a balanced bit-width between input, output, and moduli representation, as given in Table 1. In literature, the design problem of 2<sup>n</sup>-1 and 2n+1 residue multiplication is achieved through MBE schemes, whereas the possibilities of addressing this problem using array architecture are hardly considered, especially for signed numbers. The hierarchical approach for signed array multiplication presented in [25]. The motivation behind this work is the regularity in VLSI implementation and the reduced area budget offered by the array architectures compared to MBE architecture. The delay problem usually found in array architecture compared to the MBE scheme is addressed here using hierarchy based processing of the input bits and parallel addition structure. For comparative analysis, the adder structure is realized using CSA and Han Carlson parallel prefix [26] based schemes. The mathematical background, algorithm, and architecture of proposed residue 2<sup>n</sup>-1, 2<sup>n</sup>+1, and 2<sup>n</sup> multiplications are presented in the following subsections.

Table 1: Balanced word-length moduli representation

| Moduli                     | 2 <sup>n</sup> -1 | 2 <sup>n</sup> | 2 <sup>n</sup> +1 |

|----------------------------|-------------------|----------------|-------------------|

| Number of input bits A & B |                   | n              |                   |

| Moduli representation bits | n                 | n              | n+1               |

| Number of output bits - P  | n                 | n              | n+1               |

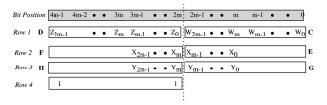

Figure 1: Intermediate PPs arrangement (nxn) [25]

#### 3.1.1 Proposed 2<sup>n</sup>-1 SRM

The 2<sup>n</sup>-1 modulo multiplication module is one of the essential operations in the RNS independent arithmetic channel. The mathematical background, algorithm,

and the proposed architectures for the signed 2<sup>n</sup>-1 residue multiplier are given below.

#### Mathematical modeling

Consider the 2's complement signed number representation of two binary numbers A and B as given in Eq. (1) & (2)

$$A = -a_{n-1} 2^{n-1} + \sum_{i=0}^{n-2} a_i 2^i$$

(1)

$$B = -b_{n-1} 2^{n-1} + \sum_{i=0}^{n-2} b_i 2^i$$

(2)

The 2<sup>n</sup>-1 residue product representation is given in Eq. (3)

$$P = |A \times B|_{2^{n}-1} = \left| \left( -a_{n-1} 2^{n-1} + \sum_{i=0}^{n-2} a_{i} 2^{i} \right) \times \left( -b_{n-1} 2^{n-1} + \sum_{i=0}^{n-2} b_{i} 2^{i} \right) \right|_{2^{n}-1}$$

(3)

Step 1. Partitioning of Input bits and Generation of intermediate PPs W, X, Y, Z using hierarchical partitioning multiplier [25]

#### **Step 2. PP arrangement:**

The generated PPs are arranged [25], and a constant is added, as shown in Fig. 1 where m=n/2.

#### **Step 3. Rearrangement of Intermediate PPs:**

Fig. 2 shows the rearrangement of PPs, and the addition process flow carried out for the  $2^n$ -1 residue multiplication, and the corresponding mathematical operations are given in Eq. (4) – (6). The notations and operators used in this mathematical modeling are summarized in Table 2 and Table 3 respectively.

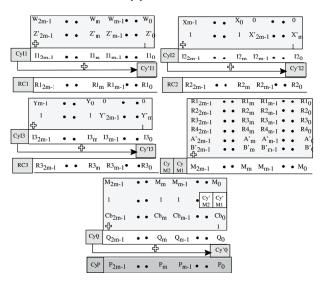

**Figure 2:** PP Rearrangement and addition process 2<sup>n</sup>-1 (nxn)

Table 2: Notations used in mathematical modeling

| Notations                                                                | Description                                                                                               |

|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| A <sub>H</sub> , A <sub>L</sub> , B <sub>H</sub> ,<br>and B <sub>L</sub> | Higher and Lower bits of A & B inputs.                                                                    |

| C <sub>b</sub>                                                           | Compensation Bits                                                                                         |

| $M_{i+1 \parallel} M_i$                                                  | Overflow bits of M <sub>i-1</sub> addition process                                                        |

| Cy <sub>I1</sub>                                                         | One bit Carry of I <sub>1</sub> addition process<br>that has to be IEAC (Inverted End<br>around Carry)    |

| Cy <sub>12</sub>                                                         | One bit Carry of I <sub>2</sub> addition process that has to be IEAC                                      |

| Cy <sub>13</sub>                                                         | One bit Carry of I <sub>3</sub> addition process that has to be IEAC                                      |

| R <sub>1c</sub>                                                          | Carry Bit of R <sub>1</sub> (or) Overflow bit of R <sub>1</sub>                                           |

| R <sub>2c</sub>                                                          | Carry Bit of R <sub>2</sub> (or) Overflow bit of R <sub>2</sub>                                           |

| R <sub>3c</sub>                                                          | Carry Bit of R <sub>3</sub> (or) Overflow bit of R <sub>3</sub>                                           |

| Сумі                                                                     | n/2 Overflow carry bits of Mi addition<br>process. If No overflow occurred n/2<br>bit zeros is considered |

| Cy <sub>Qi</sub>                                                         | One bit Carry of Qi addition process that has to be IEAC                                                  |

**Table 3:** Operators used in mathematical modeling

| Bi           |                               | at: a=12; b=8; n=4<br>1100; b=1000; n=0                 | 100                 |

|--------------|-------------------------------|---------------------------------------------------------|---------------------|

| Operator     | Description/<br>Functionality | Example                                                 | Result              |

|              | AND                           | $(a_i . b_i)$                                           | (1000) <sub>2</sub> |

| -            | OR                            | $(a_i   b_i)$                                           | (1100) <sub>2</sub> |

| ā            | NOT                           | ā                                                       | (0011) <sub>2</sub> |

| <del>-</del> | NAND                          | $\left(\overline{a_i \cdot b_i}\right)$                 | (0111) <sub>2</sub> |

| 0            | EXOR                          | $(a_i \oplus b_i)$                                      | (0111) <sub>2</sub> |

| <b>⊕</b>     | EXNOR                         | $\left(\overline{a_i \oplus b_i}\right)$                | (1000) <sub>2</sub> |

| +            | Addition                      | $\left(a_{i}+b_{i}\right)$                              | (20) <sub>10</sub>  |

|              | Modulus                       | $\left a\times b\right _{2^{n}-1}$                      | (6) <sub>10</sub>   |

| Σ            | Summation                     | $\sum_{i=0}^{3} a_{i}$                                  | (12) <sub>10</sub>  |

| ΣΣ           | Double<br>Summation           | $\sum_{j=0}^{3} \sum_{i=0}^{3} (a_i \cdot b_i) 2^{i+j}$ | (96) <sub>10</sub>  |

| -            | Subtraction                   | (a - b)                                                 | (4) <sub>10</sub>   |

| a b                                                 | Multiplication            | a b                                                                   | (96)10                  |

|-----------------------------------------------------|---------------------------|-----------------------------------------------------------------------|-------------------------|

| Х                                                   | Multiplication            | $(a \times b)$                                                        | (96) <sub>10</sub>      |

| /                                                   | Division                  | $\binom{n}{2}+1$                                                      | (3) <sub>10</sub>       |

| $\left\ \left(\times\right)^{-1}\right\ _{2^{n}+1}$ | Multiplicative<br>Inverse | $\left \left(\mathbf{a}\times\mathbf{b}\right)^{-1}\right _{2^{n}+1}$ | (14) <sub>10</sub>      |

| II                                                  | Concatenation             | (a    b)                                                              | (11001000) <sub>2</sub> |

$$\begin{split} M_{i\text{-}l} = & \sum_{i=1}^{n} \left( W_{i\text{-}l} + Z_{li\text{-}l} \right) 2^{i\text{-}l} + \sum_{i=\frac{n}{2}+1}^{n} \left( X_{li\text{-}l} + Y_{li\text{-}l} \right) 2^{i\text{-}l} \\ + & \sum_{i=1}^{\frac{n}{2}} \left( X_{li\text{-}l} + Y_{li\text{-}l} \right) 2^{i\text{-}l} + 2^{0} + 2^{n\text{-}l} \end{split} \tag{4}$$

The final product is

$$P_{i-1} = |A \times B|_{2^{n}-1} = \sum_{i=1}^{n} (M_{i-1} + C_{bi-1}) 2^{i-1}$$

(5)

The compensation bits are expressed as

$$C_{bi-1} = \left(\sum_{i=1}^{n} (Sub) 2^{i-1}\right) + \left(\sum_{i=1}^{2} (Add_{i-1}) 2^{i-1}\right)$$

(6)

Where

$$Ad_0 = M_{i+1} \cdot \overline{M_i}$$

;  $Ad_1 = M_{i+1} \cdot M_i$ ;  $Sub = \overline{M_{i+1}} \cdot \overline{M_i}$

#### Algorithm

The proposed 2<sup>n</sup>-1 SRM algorithm is given below

- 1. Input: A & B (A, B  $\rightarrow$  n-bit signed numbers), where n = 4,8,16,32,etc..

- 2. Output  $P \leftarrow |A \times B|_{2^{n}-1}$ , where  $P \leftarrow n$  bit

- 3. Intermediate PPs Generation  $\rightarrow W, X, Y, Z$

- 4. Rearrange the Intermediate PPs into 4 rows as in Fig. 1.

- Split the arrangement in Fig. 1 into two equal halves

LSP (Least Significant Plane) ← Bit\_Pos(0 to (n-1))

MSP (Most Significant Plane) ← Bit\_Pos(n to (2n-1))

- 6. Fold the MSP towards LSP side as given in Fig. 2.

- 7.  $M \leftarrow Sum$  (LSP, Folded MSP, EAC)

- 8.  $P \leftarrow Sum(M,C_p)$

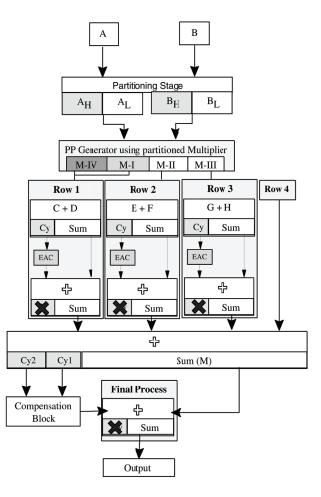

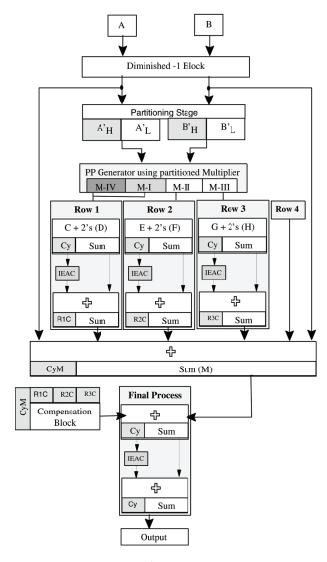

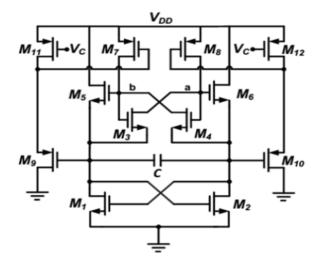

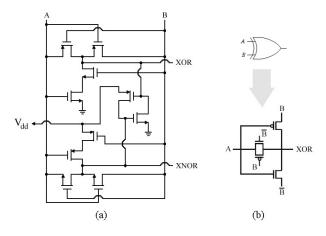

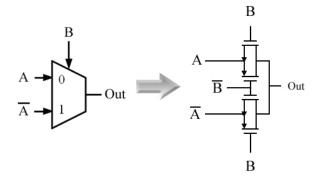

#### Architecture

The architecture of proposed 2<sup>n</sup>-1 residue multiplication is shown in Fig. 3. The architecture consists of three stages, namely the partitioning stage, intermediate PPs

generation stage, and adder stage. The four parallel modules in the intermediate PP generation stage M-I, M-II, M-III, M-IV indicates the hardware required for computing W, X, Y, Z given in [25]. The four independent parallel addition process observed in the architecture is the main reason for achieving high performance in the proposed array architecture. The compensation bits are gets added in the final stage to obtain modulo results. CSA and Han-Carlson parallel prefix adder structure is incorporated in Fig. 3 in order to analyze the performance. The results of the proposed work are further discussed in Section 5.

Figure 3: Architecture of 2<sup>n</sup>-1 SRM

#### 3.1.2. Proposed $2^n+1$ SRM

The 2<sup>n</sup>+1 residue multiplication problem is considered as a demanding operation in RNS Processor due to the increase in moduli output range compared to 2<sup>n</sup> and 2<sup>n</sup>-1 multiplications, as represented in Table 1. In the proposed scheme, the increased moduli output range is regulated using the diminished-1 approach for both multiplier and multiplicand. The primary advantage of using the proposed scheme is that this architecture can handle exceptional cases like 'all-zeros' input and

'all-ones' input, which consecutively produce the correct results. This architecture handles the bit positions higher than n-1 by complementing and mapping them to the LSBs. The mathematical background, algorithm, and the proposed architectures for signed 2<sup>n</sup>+1 residue multipliers are given in the below subsections.

#### Mathematical modeling

The diminished-1 representation of binary inputs A and B are modified as A' & B', which is given in Eq. (7) - (8)

$$A' = \left(-a_{n-1}2^{n-1} + \sum_{i=0}^{n-2}a_i2^i\right) - 1 \tag{7}$$

$$\mathbf{B'} = \left(-b_{n-1} 2^{n-1} + \sum_{i=0}^{n-2} b_i 2^i\right) - 1 \tag{8}$$

The residue product P is given by the following Eq.(9)

$$P = |A \times B|_{2^{n}+1} = |(A' \times B') + A' + B' + C_{b}|_{2^{n}+1}$$

(9)

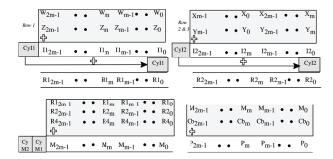

The methodology and arrangements of PP are the same as step 1 and step 2 of signed 2<sup>n</sup>-1, but the inputs are A' and B'. The final product is obtained by rearranging the PPs of Fig. 1 in such a way to obtain the result of 2<sup>n</sup>+1 residue multiplication. Fig. 4 shows the rearrangement of PPs, the position of PPs, and the addition process flow carried out for the 2<sup>n</sup>+1 multiplication, and the same is represented in Eq. (10) – (20). The mathematical operations performed between Row 1 to Row 4 are given below

#### **Row 1:**

$$I_{1(i-1)} = \left(\sum_{i=1}^{n} \left(W_{i-1} + \overline{Z_{1i-1}}\right) 2^{i-1} + 1\right)$$

(10)

$$R_{1(i\text{-}1)} = \sum\nolimits_{i=1}^{n} \! \left( I_{1(i\text{-}1)} \right) 2^{i\text{-}1} + \! \left( \overline{Cy_{11}} \right) \! 2^{0} \tag{11}$$

#### **Row 2:**

$$\begin{split} &I_{2(i\text{-}l)} \! = \! \sum_{i = \frac{n}{2} + l}^{n} \! \left( X_{l(i\text{-}(m+l))} \right) \! 2^{i\text{-}l} \! + \! \left( \sum_{i = 1}^{\frac{n}{2}} \! \left( \overline{X_{l(m+i\text{-}l)}} \right) \! 2^{i\text{-}l} \right) \\ &+ \! \sum_{i = \frac{n}{2} + l}^{n} \! \left( 1 \right) \! 2^{i\text{-}l} \! + \! \left( \sum_{i = 1}^{\frac{n}{2}} \! \left( 0 \right) \! 2^{i\text{-}l} \right) \! + \! 1 \end{split} \tag{12}$$

$$R_{2(i-1)} = \sum_{i=1}^{n} (I_{2(i-1)}) 2^{i-1} + (\overline{Cy_{12}}) 2^{0}$$

(13)

#### **Row 3:**

$$\begin{split} &I_{3(i\text{-}1)} \! = \! \sum_{i = \frac{n}{2} + 1}^{n} \! \left( Y_{l(i\text{-}(m+1))} \right) 2^{i\text{-}1} \! + \! \left( \sum_{i = 1}^{\frac{n}{2}} \! \left( \overline{Y_{l(m+i\text{-}1)}} \right) 2^{i\text{-}1} \right) \\ &+ \! \sum_{i = \frac{n}{2} + 1}^{n} \! \left( 1 \right) \! 2^{i\text{-}1} \! + \! \left( \sum_{i = 1}^{\frac{n}{2}} \! \left( 0 \right) \! 2^{i\text{-}1} \right) \! + \! 1 \end{split} \tag{14}$$

$$R_{3(i-1)} = \sum_{i=1}^{n} \left( I_{3(i-1)} \right) 2^{i-1} + \left( \overline{Cy_{13}} \right) 2^{0}$$

(15)

#### **Row 4:**

$$R_{4(i-1)} = (0)2^{n-1} + \sum_{i=1}^{n-1} (1)2^{i-1}$$

(16)

Figure 4: PP Rearrangement and addition process 2<sup>n</sup>+1 (nxn)

Finally, all four rows get added as per the following equations.

$$M_{(i-1)} = \sum_{i=1}^{n} \left( R_{1(i-1)} + R_{2(i-1)} + R_{3(i-1)} + R_{4(i-1)} + A_{i-1} + B_{i-1} \right) 2^{i-1}$$

(17)

$$Q_{i-1} = \left(\sum_{i=1}^{n} \left(M_{i-1} + C_{bi-1}\right) 2^{i-1}\right) + \sum_{i=1}^{2} \left(\overline{Cy_{Mi-1}}\right) + \sum_{i=1}^{2} \left(\overline{Cy_{Mi-1}}\right) + \sum_{i=1}^{2} \left(\overline{Cy_{Mi-1}}\right) 2^{i-1} + \left(\sum_{i=3}^{n} (1) 2^{i-1}\right) + 1$$

(18)

Where C<sub>h</sub> is given in Eq. (19)

$$C_{bi-1} = \left(\sum_{i=3}^{n} (1) 2^{i-1}\right) + \left(\sum_{i=1}^{2} \left(Ad_{i-1} + \overline{Sub_{i-1}}\right) 2^{i-1}\right) + 1$$

$$Ad_{0} = A'[n-1] \overline{\bigoplus} B'[n-1]$$

$$Ad_{1} = A'[n-1] | B'[n-1]$$

$$Sub_{0} = \left(R_{1c} \oplus R_{2c} \oplus R_{3c}\right)$$

$$Sub_{1} = \left(R_{1c} \cdot R_{2c}\right) | \left(R_{2c} \cdot R_{3c}\right) | \left(R_{3C} \cdot R_{1c}\right)$$

(19)

The 2<sup>n</sup>+1 multiplication is given in Eq. (20)

$$P_{[n:0]} = \left| A \times B \right|_{2^{n}+1} = \sum\nolimits_{i=1}^{n} \left( Q_{(i-1)} \right) 2^{i-1} + \overline{Cy_{Qi}} \tag{20}$$

#### Algorithm

The proposed 2<sup>n</sup>+1 SRM algorithm is given below

- 1. Input: A & B (A, B $\rightarrow$  n-bit signed numbers), where n=4,8,16,32,etc..

- 2. Output  $P \leftarrow |A \times B|_{2^{n}+1}$ , where  $P \leftarrow n+1$  bit

- 3.  $A' \leftarrow Diminished-1$  (A);  $B' \leftarrow Diminished-1$  (B);

- 3. Intermediate PPs Generation  $\rightarrow W, X, Y, Z$

- 4. Rearrange the Intermediate PPs into 4 rows as shown in Fig. 1.

- Split the arrangement in Fig. 1 into LSP ← Bit\_Pos(0 to (n-1)) MSP ← Bit\_Pos (n to (2n-1))

- 6. Fold the MSP towards LSP as given in Fig. 4.

- 7.  $R_1 \leftarrow Sum$  (LSP, 2's Comp. (MSP), IEAC);

- 8.  $R_3 \leftarrow Sum$  (LSP, 2's Comp. (MSP), IEAC);

- 9. R<sub>3</sub>←Sum (LSP, 2's Comp. (MSP), IEAC);

- 10.  $R_4 \leftarrow Sum$  (LSP, 2's Comp. (MSP), IEAC);

- 11. M  $\leftarrow$  Sum ((Rx,) A', B'), where x = 1,2,3,4

- 12. P ← Sum (M, 2's Complement (Cy<sub>M</sub>), C<sub>H</sub> IEAC)

#### Architecture

The overall architecture arrangement of 2<sup>n</sup>+1 is similar to that of 2<sup>n</sup>-1 except for the fact that it has some additional modules to perform 2's complement operation and Inverted End Around Carry (IEAC), as shown in Fig. 5. However, the compensation generation scheme is complicated compared to 2<sup>n</sup>-1 architecture.

#### 3.1.3 Signed 2<sup>n</sup> residue multiplier

#### Mathematical modeling

The operation required to obtain Module I (W) follows the same pattern as in 2<sup>n</sup>-1. The X & Y are given in Eq. (21) and (22). Z is not required for computing 2<sup>n</sup> because it has a higher weight position compared to 2<sup>n</sup> value.

$$X = \left(\overline{a_{n\text{-}1} \cdot b_0}\right) 2^{m\text{-}1} + \sum\nolimits_{i=m}^{n\text{-}2} \left(a_i \cdot b_0\right) 2^{i\text{-}m} + \sum\nolimits_{j=1}^{m\text{-}1} \sum\nolimits_{i=m}^{n\text{-}1 \cdot j} \left(a_i \cdot b_j\right) 2^{i\text{+}j\text{-}m} \quad \text{(21)}$$

$$Y = \overline{\left(b_{n-1} \cdot a_{0}\right)} 2^{m-1} + \sum_{i=m}^{n-2} \left(b_{i} \cdot a_{0}\right) 2^{i-m} + \sum_{j=1}^{m-1} \sum_{i=m}^{n-1-j} \left(b_{i} \cdot a_{j}\right) 2^{i+j-m} \tag{22}$$

The final 2<sup>n</sup> product is given in Eq. (23)

Figure 5: Architecture of 2<sup>n</sup>+1 SRM

$$P = |A \times B|_{2^{n}} = \sum_{i=0}^{2m-1} W_{i} 2^{i} + \sum_{k=m}^{2m-1} (X_{k-m} + Y_{k-m}) 2^{k}$$

(23)

#### 3.2 Proposed unbalanced word-length SRM

The unbalanced word-length moduli multiplier typically used in applications different bit-width proportion between input, moduli, and output is required. In unbalanced word-length residue multiplication, the number of bits required to represent the input, moduli, and output bit-width, which are summarized in Table 4. The strategy followed to design 2<sup>k</sup>-1 module is derived from the 2<sup>n</sup>-1 balanced module. However, the 2<sup>k</sup>+1 is not derived from the 2<sup>n</sup>+1 balanced module because it may lead to comparatively complex architecture with more delay penalty. Instead, 2<sup>n</sup>-1 balanced design is converted to an unbalanced 2<sup>k</sup>+1 by modifying the final result of 2<sup>n</sup>-1 multiplication.

**Table 4:** Unbalanced word-length moduli representation

| Moduli                     | 2 <sup>k</sup> -1 | 2 <sup>k</sup> | 2 <sup>k</sup> +1 |

|----------------------------|-------------------|----------------|-------------------|

| Number of input bits A & B |                   | n              |                   |

| Moduli representation bits | k                 | k              | k+1               |

| Number of output bits -P   | k                 | k              | k+1               |

#### 3.2.1. Proposed $2^{k}-1$ and $2^{k}+1$ SRM

#### Mathematical modeling

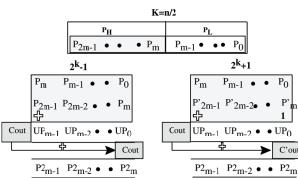

Let us consider the n bit output of balanced  $2^n-1$  multiplication given in Eq. (5). It is split into two halves  $P_L$  and  $P_H$ , as shown in Fig. 6 to obtain the result k=n/2 & k=n/4 bits, and the corresponding equations are given in (24) – (25).

For k=n/2

$$P_{L} = P\left[\frac{n}{2} - 1:0\right]$$

$$P_{H} = P\left[n - 1:\frac{n}{2}\right]$$

$$UP_{i-1} = \sum_{i=1}^{\frac{n}{2}} \left(P_{i-1} + P_{\frac{n}{2} + i - 1}\right) 2^{i-1}$$

$$P2_{i-1} = \sum_{i=1}^{\frac{n}{2}} \left(UP_{i-1}\right) 2^{i-1} + C_{out} 2^{0}$$

$$UP_{i-1} = \sum_{i=1}^{\frac{n}{2}} \left(P_{i-1} + \overline{P_{\frac{n}{2} + i - 1}}\right) 2^{i-1} + 2^{0}$$

$$P2_{[k:0]} = \sum_{i=1}^{\frac{n}{2}} \left(UP_{i-1}\right) 2^{i-1} + \overline{C_{out}} 2^{0}$$

$$E=n/2$$

$$K=n/2$$

**Figure 6:** Unbalanced PP Rearrangements and addition process

#### For k=n/4

k=n/4 design is derived from k=n/2. The output of k=n/2 acts as an input for the k=n/4 design.

$$P2_{L} = P2 \left[ \frac{n}{2} - 1:0 \right]$$

$$P2_{H} = P2 \left[ n-1: \frac{n}{2} \right]$$

$$NP_{i-1} = \sum_{i=1}^{\frac{n}{2}} \left( P2_{i-1} + P2_{\frac{n}{2} + i-1} \right) 2^{i-1}$$

$$P4_{i-1} = \sum_{i=1}^{\frac{n}{2}} \left( NP_{i-1} \right) 2^{i-1} + C_{out} 2^{0}$$

$$UP_{i-1} = \sum_{i=1}^{\frac{n}{2}} \left( P2_{i-1} + \overline{P2_{\frac{n}{2} + i-1}} \right) 2^{i-1} + 2^{0}$$

$$P4_{[k:0]} = \sum_{i=1}^{\frac{n}{2}} \left( UP_{i-1} \right) 2^{i-1} + \overline{C_{out} 2^{0}}$$

$$2^{k} + 1$$

$$P4_{[k:0]} = \sum_{i=1}^{\frac{n}{2}} \left( UP_{i-1} \right) 2^{i-1} + \overline{C_{out} 2^{0}}$$

#### Algorithm

The proposed SRM algorithm for the unbalanced  $2^{k}$ -1 and  $2^{k}$ +1 is given below

- 1. Input: A & B (A, B  $\rightarrow$  n bit signed numbers), where n=4,8,16,32,etc.

- 2. Output  $P \leftarrow |A \times B|$ , where  $P \leftarrow k$  bit for  $2^k 1$  and k+1 bit for  $2^k + 1$

- 3. Consider Eq.(5)  $P \leftarrow |A \times B|_{2^{n-1}}$ ,

- 4. Split the Eq. (5) into two equal halves  $P_{H} \leftarrow Bit\_Pos(0 \text{ to } (n/2)-1)$   $P_{L} \leftarrow Bit\_Pos((n/2) \text{ to } n-1)$

- 5. Fold the P<sub>u</sub> towards P<sub>i</sub> side as mentioned in Fig. 6.

#### If (2k-1) Operation

- 6.  $P_2 = Sum(P_1, P_2, EAC) \rightarrow k=n/2$

- 7.  $P_{A} = Sum(P_{21}, P_{2H}, EAC) \rightarrow k=n/4$

- 8.  $P_8 = Sum(P_{41}, P_{4H}, EAC) \rightarrow k=n/8$

#### If (2k+1) Operation

- 6.  $P_2 = Sum(P_1, 2's (P_1), EAC) \rightarrow k=n/2$

- 7.  $P_A = Sum(P_{21}, 2's (P_{2H}), EAC) \rightarrow k=n/4$

- 8.  $P_8 = Sum(P_{4L}, 2's (P_{4H}), EAC) \rightarrow k=n/8$

#### Architecture

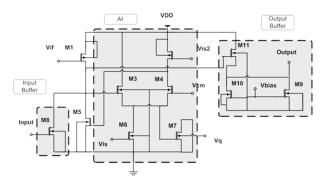

The unbalanced SRM architecture for 2<sup>k</sup>-1 and 2<sup>k</sup>+1 is depicted in Fig. 7. The architecture is derived from proposed 2<sup>n</sup>-1 SRM.

Figure 7: Architecture of 2k-1 & 2k+1 SRM

#### 3.2.2. 2k SRM

The residue multiplication  $P = |A \times B|_{x}$  is derived from a  $2^n$  balanced residue multiplier equation. The characteristic equations of  $2^k$  unbalanced residue multiplication are given in Eq. (26)

$$P = |A \times B|_{2^{k}} = \begin{cases} RP_{i-1} = \sum_{i=1}^{\frac{n}{2}} (P_{i-1}) 2^{i-1} \to k = \frac{n}{2} \\ P4_{i-1} = \sum_{i=1}^{\frac{n}{4}} (P_{i-1}) 2^{i-1} \to k = \frac{n}{4} \\ P8_{i-1} = \sum_{i=1}^{\frac{n}{8}} (P_{i-1}) 2^{i-1} \to k = \frac{n}{8} \end{cases}$$

(26)

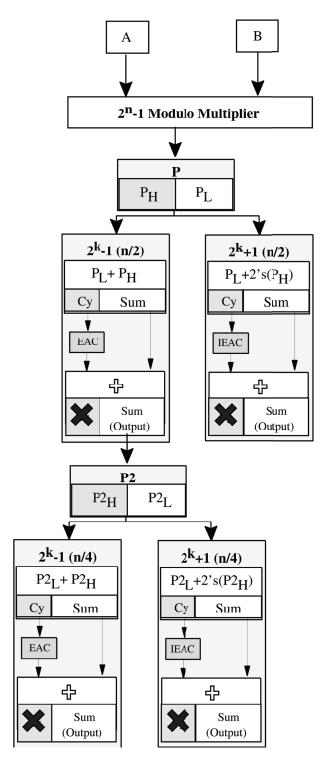

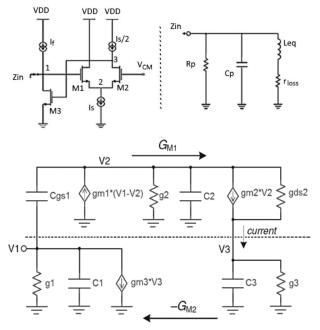

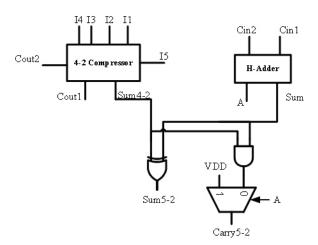

#### 4 RNS processor

#### 4.1 Architecture

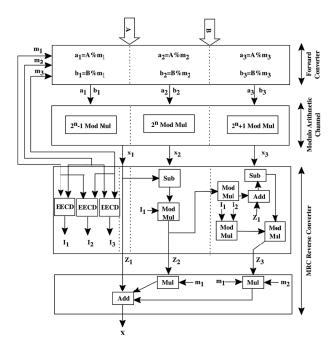

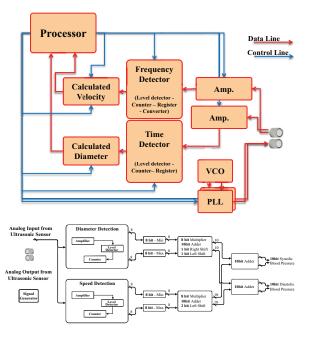

In general, the cryptographic algorithm requires many rounds of arithmetic operations in order to create the ciphertext. Instead of doing such lengthy arithmetic operations in binary representation, residue values can be used to save the area and time budget. The proposed balanced and unbalanced word-length residue multipliers are used for implementing special moduli set based RNS computing platforms, as given in Fig. 8. The RNS processing system consists of three blocks, namely Forward Converter (FC), Independent Modulo Arithmetic Processing Unit (IMAPU), and Reverse Converter (RC) [13], [27]. The proposed SRM architectures are used to design arithmetic channels and RC. The FC and RC blocks convert the binary number to residue number and vice versa. The IMAPU block consists of application-based arithmetic operations or any other desired operations in modulo representation. The RC operation can be performed using the Chinese Remainder Theorem (CRT) [28] or Mixed Radix Conversion (MRC) [29]. In this paper, the MRC technique [13,27] is considered for the conversion in the RC block. The characteristic equations of MRC given in Eq. (27) – (29) shows that the operation can be done by modulo subtractions, multiplicative inverses, and residue multiplication. Here the multiplicative inverse is computed using the Extended Euclidean algorithm (EECD) [30]. From [13,27] the decoded number is expressed in the following form for MRC technique

$$X=Z_{N}m_{N-1}m_{N-2}\cdots\cdots m_{1}+\cdots\cdots+Z_{3}m_{2}m_{1}+Z_{2}m_{1}+Z_{1}$$

(27)

where  $0 < Z_i < m_i$

The mixed-radix digits are derived as,

$$Z_{1}=x_{1}$$

$$Z_{2}=\left\|m_{1}^{-1}\right\|_{m_{2}}\times\left(x_{2}-Z_{1}\right)\right\|_{m_{2}}$$

$$Z_{3}=\left\|\left(m_{2}m_{1}\right)^{-1}\right\|_{m_{3}}\times\left(x_{3}-Z_{2}m_{1}+Z_{1}\right)\right\|_{m_{3}}$$

(28)

The finalized equation is derived for the value of N bit as,

$$Z_{N} = \left| \left( m_{1} m_{2} m_{3} \cdots m_{N-1} \right)^{-1} \right|_{m_{N}}$$

$$\times \left| \left( x_{N} - \left( x_{N-1} m_{N-2} \cdots Z_{2} m_{1} + Z_{1} \right) \right) \right|_{m_{N}}$$

(29)

Where  $m_1, m_2, m_3$  are moduli sets, and  $x_1, x_2, x_3$  are residue output of IMAPU.

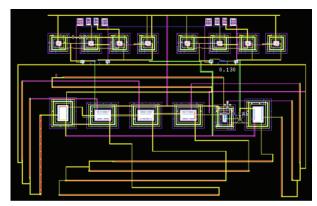

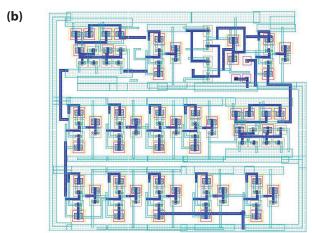

Figure 8: Hardware realization of signed RNS processor

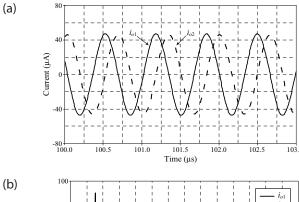

The effectiveness of the proposed multiplier is tested by designing decoupled modulo arithmetic channels and memoryless MRC reverse converter, as shown in Fig. 8. An example calculation depicting the dataflow in the architecture is given in Table 5.

Table 5: RNS processor computation

#### 4.2 Range analysis

The permissible number ranges for balanced and unbalanced word-length residue multipliers are shown in Table 6. The bit-width required to represent triple moduli set  $\{2^n-1, 2^n, 2^n+1\}$  balanced system is 3n+1 bits whereas the maximum number of bits required for unbalanced moduli  $\{2^k+1, 2^k, 2^{k-1}\}$  system is 3k+1.

#### 5 Results and Discussions

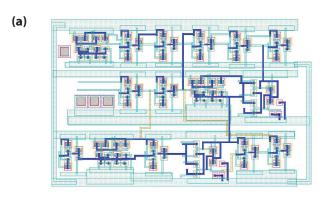

#### 5.1 FPGA synthesis

The architecture level functional verification of the proposed design is coded using Verilog HDL and simulated in the Xilinx ISIM tool. The results corresponding to hardware architectures are synthesized in Xilinx Synthesis Technology (XST) for balanced and unbalanced type residue multipliers. The results of the proposed architecture with CSA (Proposed-I) and prefix-based adders (Proposed-II) are presented in Table 7 and Table 8, respectively.

**Table 7:** FPGA synthesis results of balanced word-length SRM

|                   |    | Xilinx Zynq FPGA Board<br>(XC7Z020CLG484-1) |         |        |          |  |  |  |  |

|-------------------|----|---------------------------------------------|---------|--------|----------|--|--|--|--|

| Multiplier        | n  | Propo                                       | sed - I | Propo  | sed - II |  |  |  |  |

|                   |    | LUT                                         | Delay   | LUT    | Delay    |  |  |  |  |

|                   |    | (No's)                                      | (ns)    | (No's) | (ns)     |  |  |  |  |

|                   | 8  | 37                                          | 11.5    | 37     | 11.4     |  |  |  |  |

| 2 <sup>n</sup>    | 16 | 186                                         | 26.2    | 203    | 21.7     |  |  |  |  |

|                   | 32 | 928                                         | 70.3    | 1026   | 45.1     |  |  |  |  |

|                   | 8  | 112                                         | 18.6    | 144    | 17.7     |  |  |  |  |

| 2 <sup>n</sup> -1 | 16 | 530                                         | 51.3    | 697    | 28.7     |  |  |  |  |

|                   | 32 | 2134                                        | 155.7   | 2848   | 53.0     |  |  |  |  |

|                   | 8  | 235                                         | 29.4    | 270    | 27.4     |  |  |  |  |

| 2 <sup>n</sup> +1 | 16 | 688                                         | 85.8    | 861    | 44.1     |  |  |  |  |

|                   | 32 | 2215                                        | 196.7   | 3705   | 79.8     |  |  |  |  |

| A=600                                    | B=600                         | m₁=255                                          | m₂=256                                         | m₃=257                      |  |  |  |  |  |  |

|------------------------------------------|-------------------------------|-------------------------------------------------|------------------------------------------------|-----------------------------|--|--|--|--|--|--|

| Forward Conversion                       |                               |                                                 |                                                |                             |  |  |  |  |  |  |

| $a_1 =  600 _{255} = 90$                 | a                             | $a_2 =  600 _{256} = 88$                        |                                                | $a_3 =  600 _{257} = 86$    |  |  |  |  |  |  |

| b <sub>1</sub> = 600  <sub>255</sub> =90 | b                             | $o_2 =  600 _{256} = 88$                        |                                                | $b_3 =  600 _{257} = 86$    |  |  |  |  |  |  |

|                                          |                               | IMAPU                                           |                                                |                             |  |  |  |  |  |  |

| $x_1 =  90x90 _{255} = 195$              | X <sub>2</sub>                | $= 88x88 _{256}=64$                             |                                                | $x_3 =  86x86 _{257} = 200$ |  |  |  |  |  |  |

|                                          | MRC bas                       | ed Reverse Convers                              | ion                                            |                             |  |  |  |  |  |  |

| Z <sub>1</sub> = 195                     |                               |                                                 | $Z_2 =   255 ^{-1}_{256}$ $=  255x-13$ $= 131$ |                             |  |  |  |  |  |  |

|                                          | 131x255)+195)  <sub>257</sub> | X=(5x255x256)+ ((<br>=326400+33405-<br>X=360000 |                                                | )                           |  |  |  |  |  |  |

|                                          |                               | X=3,60,000                                      |                                                |                             |  |  |  |  |  |  |

**Table 6:** Range analysis of triple moduli set RNS processor

|                                          | Balanced                    | Word-Length                                                                                                                                                                                                                                                                                                                                                                  | Moduli                    | Unbalanc                    | ed Word-Lengtł                                                                                                                                                       | n Moduli                 |  |  |

|------------------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|--|

| Moduli                                   | 2 <sup>n</sup> -1           | 2 <sup>n</sup>                                                                                                                                                                                                                                                                                                                                                               | 2 <sup>n</sup> +1         | 2 <sup>k</sup> -1           | 2 <sup>k</sup>                                                                                                                                                       | 2 <sup>k</sup> +1        |  |  |

| Number of Input Bits – A & B             |                             | n                                                                                                                                                                                                                                                                                                                                                                            |                           |                             |                                                                                                                                                                      |                          |  |  |

| Number of Output Bits -P                 | n                           | n                                                                                                                                                                                                                                                                                                                                                                            | n+1                       | k                           | k                                                                                                                                                                    | k+1                      |  |  |

|                                          | Pe                          | ermissible Nur                                                                                                                                                                                                                                                                                                                                                               | mber Range                |                             |                                                                                                                                                                      |                          |  |  |

| Input Range<br>(Signed Integers)         |                             |                                                                                                                                                                                                                                                                                                                                                                              |                           |                             |                                                                                                                                                                      |                          |  |  |

| Input Range<br>(Unsigned Integers)       |                             | [0 ↔ 2n-1]                                                                                                                                                                                                                                                                                                                                                                   |                           |                             |                                                                                                                                                                      |                          |  |  |

| Output Range -P                          | $[0 \leftrightarrow 2^n-2]$ | $[0 \leftrightarrow 2^n-1]$                                                                                                                                                                                                                                                                                                                                                  | $[0 \leftrightarrow 2^n]$ | $[0 \leftrightarrow 2^k-2]$ | $[0 \leftrightarrow 2^k-1]$                                                                                                                                          | $0 \leftrightarrow 2^k]$ |  |  |

| Dynamic Range of the Moduli              |                             | $R = \{2^{3n}-2^n\}$                                                                                                                                                                                                                                                                                                                                                         |                           | $R = \{2^{3k} - 2^k\}$      |                                                                                                                                                                      |                          |  |  |

| Permissible Range<br>(Signed Integers)   | (                           | $R = \left\{ -\frac{\left[ \left( 2^{3n} - 2^{n} \right) \right]}{2} \leftrightarrow \frac{\left[ \left( 2^{3n} - 2^{n} \right) \right]}{2} - 1 \right\} \rightarrow \text{Even}(n)$ $R = \left\{ -\frac{\left[ \left( 2^{3n} - 2^{n} \right) - 1 \right]}{2} \leftrightarrow \frac{\left[ \left( 2^{3n} - 2^{n} \right) - 1 \right]}{2} \right\} \rightarrow \text{Odd}(n)$ |                           |                             | $ \frac{\left[\left(2^{3k}-2^{k}\right)\right]}{2}-1 $ $ \frac{\left[\left(2^{3k}-2^{k}\right)-1\right]}{2} $ $ \frac{\left[\left(2^{3k}-2^{k}\right)-1\right]}{2} $ |                          |  |  |

| Permissible Range<br>(Unsigned Integers) | R=                          | $\left\{0 \leftrightarrow \left(2^{3n} - 2^n\right) - \right\}$                                                                                                                                                                                                                                                                                                              | 1}                        | R=                          | $\left\{0 \leftrightarrow \left(2^{3k} - 2^{k}\right) - 1\right\}$                                                                                                   | }                        |  |  |

**Table 8:** FPGA synthesis results of unbalanced word-length SRM

| Mul. n            |    | Zynq       | FPGA Board (X | C7Z020CLG484 | -1)        |            |            |

|-------------------|----|------------|---------------|--------------|------------|------------|------------|

| Mul.              | n  | k=ı        | n/2           | k=r          | n/4        | k=         | n/8        |

|                   |    | LUT (No's) | Delay (ns)    | LUTs (No's)  | Delay (ns) | LUT (No's) | Delay (ns) |

|                   |    |            | Pr            | oposed -l    |            |            |            |

|                   | 8  | 6          | 8             | -            | -          | -          | -          |

| 2 <sup>k</sup>    | 16 | 41         | 15            | 5            | 7.9        | -          | -          |

|                   | 32 | 250        | 43            | 41           | 13.2       | 5          | 7.9        |

|                   | 8  | 120        | 20            | -            | -          | -          | -          |

| 2 <sup>k</sup> -1 | 16 | 645        | 67            | 654          | 68.8       | -          | -          |

|                   | 32 | 2577       | 162           | 2597         | 166.5      | 2605       | 168        |

|                   | 8  | 121        | 19            | -            | -          | -          | -          |

| 2 <sup>k</sup> +1 | 16 | 649        | 70            | 654          | 78.1       | -          | -          |

|                   | 32 | 2587       | 173           | 1580         | 176.0      | 2599       | 179        |

|                   |    |            | Pro           | oposed -II   |            |            |            |

|                   | 8  | 5          | 8             | -            | -          | -          | -          |

| 2 <sup>k</sup>    | 16 | 44         | 13            | 5            | 7.8        | -          | -          |

|                   | 32 | 255        | 25            | 44           | 15.0       | 5          | 7.8        |

|                   | 8  | 156        | 18            | -            | -          | -          | -          |

| 2 <sup>k</sup> -1 | 16 | 735        | 52            | 753          | 55.0       | -          | -          |

|                   | 32 | 2967       | 157           | 3018         | 61.9       | 3049       | 164        |

|                   | 8  | 163        | 21            | -            | -          | -          | -          |

| 2 <sup>k</sup> +1 | 16 | 960        | 54            | 980          | 36.0       | -          | -          |

|                   | 32 | 2996       | 160           | 3056         | 162.5      | 3081       | 165        |

<sup>\*</sup>LUT – Look Up Table & LE- Logic Element

**Table 9:** ASIC synthesis results of balanced word-length SRM

|               |         | Technology    |               |               |             |                            |               |               |             |               |               |               |             |  |

|---------------|---------|---------------|---------------|---------------|-------------|----------------------------|---------------|---------------|-------------|---------------|---------------|---------------|-------------|--|

| NA1           | <u></u> |               | 180           | nm            |             |                            | 90 nm         |               |             |               | 45 nm         |               |             |  |

| Mui.          | n       | Area<br>(μm²) | Power<br>(μW) | Delay<br>(ns) | PDP<br>(pJ) | Area<br>(μm²)              | Power<br>(μW) | Delay<br>(ns) | PDP<br>(pJ) | Area<br>(µm²) | Power<br>(μW) | Delay<br>(ns) | PDP<br>(pJ) |  |

|               |         |               |               |               |             | 2 <sup>n</sup>             | ,             |               |             |               |               |               |             |  |

|               | 8       | 2164          | 217           | 1.3           | 0.3         | 682                        | 30            | 0.8           | 0.02        | 369           | 20            | 0.5           | 0.0         |  |

| Proposed - I  | 16      | 10438         | 1677          | 7.4           | 12          | 2967                       | 308           | 4.2           | 1.3         | 1604          | 200           | 3.6           | 0.7         |  |

|               | 32      | 39171         | 6095          | 26.8          | 163         | 12273                      | 1218          | 15.2          | 18.5        | 6557          | 739           | 13            | 9.4         |  |

|               | 8       | 2044          | 228           | 1.2           | 0.3         | 652                        | 51            | 0.8           | 0.0         | 357           | 32            | 0.8           | 0.0         |  |

| Proposed - II | 16      | 11302         | 1809          | 6.7           | 12          | 3167                       | 407           | 4.7           | 1.9         | 1712          | 232           | 4.1           | 1.0         |  |

|               | 32      | 45784         | 6316          | 23.5          | 148         | 15787                      | 1264          | 16.7          | 21          | 8435          | 769           | 14            | 10.7        |  |

|               |         |               |               |               | r           | 2 <sup>n</sup> -1          | 1             | 1             | r           |               |               |               | 1           |  |

|               | 8       | 8668          | 849           | 6.8           | 6           | 2733                       | 169           | 4.2           | 1           | 1477          | 108           | 4.0           | 0.43        |  |

| [22]          | 16      | 34382         | 4328          | 29.1          | 126         | 9770                       | 797           | 16.4          | 13          | 5281          | 513           | 14.3          | 7           |  |

|               | 32      | 125346        | 19176         | 86.5          | 1658        | 39270                      | 3835          | 48.9          | 188         | 20981         | 2323          | 41.2          | 96          |  |

|               | 8       | 8148          | 781           | 6.2           | 5           | 2569                       | 156           | 3.8           | 1           | 1389          | 101           | 3.7           | 0.37        |  |

| [14]          | 16      | 32663         | 3983          | 26.5          | 105         | 9282                       | 732           | 15.0          | 11          | 5017          | 473           | 13.0          | 6           |  |

|               | 32      | 119079        | 17259         | 78.7          | 1357        | 37306                      | 3452          | 44.5          | 154         | 19932         | 2089          | 37.5          | 78          |  |

|               | 8       | 8235          | 798           | 6.4           | 5           | 2597                       | 158           | 3.9           | 1           | 1404          | 103           | 3.8           | 0.38        |  |

| [23]          | 16      | 32663         | 4069          | 27.0          | 110         | 9282                       | 748           | 15.3          | 11          | 5017          | 483           | 13.3          | 6           |  |

|               | 32      | 117825        | 18025         | 80.4          | 1449        | 36913                      | 3607          | 45.5          | 164         | 19722         | 2185          | 38.3          | 84          |  |

|               | 8       | 6518          | 789           | 5.1           | 4           | 2055                       | 163           | 3.2           | 1           | 1111          | 124           | 3.1           | 0.38        |  |

| Proposed - I  | 16      | 26447         | 4058          | 22.2          | 90          | 7516                       | 824           | 12.5          | 10          | 4063          | 537           | 10.9          | 6           |  |

|               | 32      | 97926         | 18282         | 67.0          | 1225        | 30679                      | 3689          | 37.9          | 140         | 16392         | 2211          | 31.9          | 71          |  |

|               | 8       | 6708          | 809           | 4.7           | 4           | 2081                       | 169           | 2.8           | 0           | 1141          | 127           | 2.8           | 0.35        |  |

| Proposea - II | 16      | 28937         | 4147          | 20.1          | 83          | 8120                       | 845           | 11.3          | 10          | 4389          | 548           | 9.7           | 5           |  |

|               | 32      | 114459        | 18447         | 58.8          | 1084        | 35859<br>2 <sup>n</sup> +1 | 3722          | 33.7          | 125         | 19159         | 2234          | 27.5          | 61          |  |

|               | 8       | 17659         | 1058          | 13.8          | 15          | 5588                       | 209           | 8.6           | 2           | 3020          | 135           | 8             | 1           |  |

| [21]          | 16      | 63121         | 5999          | 56.5          | 339         | 18179                      | 1104          | 31.6          | 35          | 9827          | 713           | 27.8          | 20          |  |

| [21]          | 32      | 254585        | 30713         | 170           | 5221        | 79827                      | 6145          | 96            | 590         | 41349         | 3719          | 81            | 301         |  |

|               | 8       | 15365         | 1049          | 13.6          | 14          | 4874                       | 207           | 8.3           | 2           | 2634          | 135           | 8             | 1           |  |

| [15]          | 16      | 59211         | 5894          | 54.9          | 324         | 16899                      | 1085          | 31            | 34          | 9135          | 699           | 27            | 19          |  |

| ,             | 32      | 237894        | 28951         | 168           | 4864        | 73352                      | 5792          | 95            | 550         | 39659         | 3508          | 80            | 281         |  |

|               | 8       | 13961         | 944           | 11.1          | 10          | 4402                       | 188           | 6.8           | 1           | 2380          | 122           | 6.6           | 1           |  |

| [16]          | 16      | 53425         | 5216          | 51.6          | 269         | 15182                      | 961           | 29.1          | 28          | 8207          | 618           | 25.4          | 16          |  |

|               | 32      | 210141        | 25176         | 159.6         | 4018        | 65835                      | 5036          | 90.3          | 455         | 35175         | 3049          | 76            | 232         |  |

| [22]          | 8       | 13251         | 870           | 12.2          | 11          | 4142                       | 173           | 7.5           | 1           | 2239          | 112           | 7.2           | 1           |  |

| [17]          | 16      | 52376         | 4658          | 46.7          | 218         | 14871                      | 859           | 26.4          | 23          | 8039          | 554           | 23            | 13          |  |

|               | 32      | 224280        | 22582         | 141.1         | 3186        | 68951                      | 4518          | 79.8          | 361         | 37280         | 2736          | 67.2          | 184         |  |

|               | 8       | 12565         | 954           | 13.3          | 13          | 3962                       | 190           | 8.2           | 2           | 2142          | 122           | 7.9           | 1           |  |

| [18]          | 16      | 48617         | 5306          | 57            | 302         | 13816                      | 977           | 34            | 33          | 7468          | 629           | 29            | 18          |  |

|               | 32      | 187025        | 26057         | 155           | 4039        | 58593                      | 5211          | 81            | 422         | 31305         | 3155          | 78            | 246         |  |

|               | 8       | 15058         | 975           | 14            | 14          | 4776                       | 194           | 9             | 2           | 2582          | 125           | 8.5           | 1           |  |

| [19]          | 16      | 52698         | 5130          | 55.1          | 283         | 15040                      | 945           | 32            | 30          | 8130          | 610           | 28            | 17          |  |

|               | 32      | 166526        | 23163         | 154           | 3567        | 51347                      | 4633          | 80            | 371         | 27762         | 2805          | 74            | 208         |  |

|               | 8       | 8796          | 916           | 12.4          | 11          | 2773                       | 182           | 8.3           | 2           | 1499          | 118           | 7.4           | 1           |  |

| [20]          | 16      | 38893         | 4882          | 44.6          | 218         | 11053                      | 899           | 26.6          | 24          | 5974          | 581           | 22.5          | 13          |  |

|               | 32      | 158971        | 21889         | 134.7         | 2948        | 49804                      | 4379          | 64.7          | 283         | 26610         | 2650          | 60.5          | 160         |  |

|               | 8       | 8356          | 908           | 11.7          | 11          | 2635                       | 186           | 7.9           | 1           | 1424          | 143           | 7.1           | 1           |  |

| Proposed - I  | 16      | 33059         | 4787          | 41.4          | 198         | 9395                       | 972           | 24.5          | 24          | 5078          | 637           | 20.2          | 13          |  |

|               | 32      | 122408        | 21797         | 120.2         | 2620        | 38349                      | 4439          | 57.6          | 256         | 20489         | 2670          | 55.6          | 148         |  |

|               | 8       | 8831          | 929           | 11            | 10          | 2825                       | 192           | 7.2           | 1           | 1495          | 148           | 6.5           | 1           |  |

| Proposed - II | 16      | 36171         | 4841          | 37            | 179         | 10279                      | 1004          | 22            | 22          | 5556          | 653           | 18.1          | 12          |  |

|               | 32      | 143074        | 22127         | 102           | 2257        | 44857                      | 4472          | 50.7          | 227         | 23982         | 2683          | 49.8          | 134         |  |

#### 5.2 ASIC synthesis

#### 5.2.1 Performance analysis

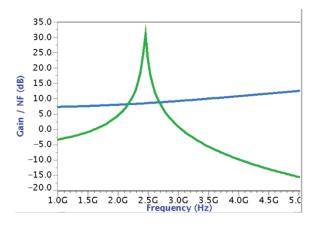

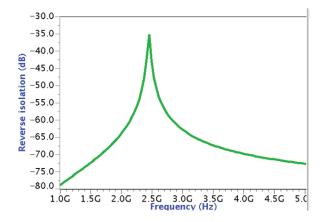

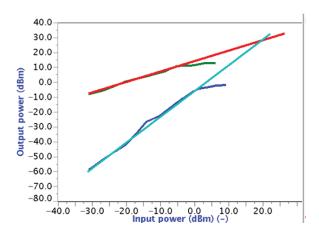

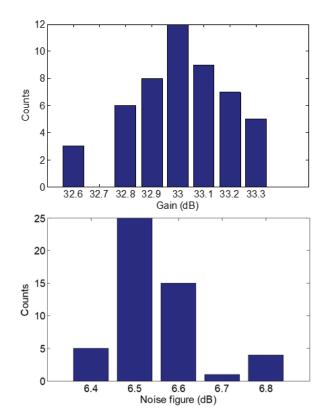

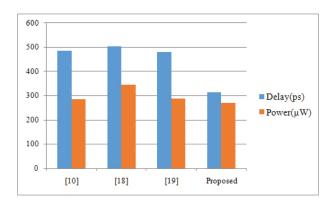

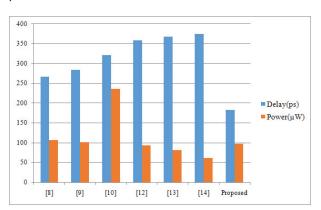

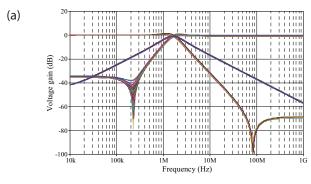

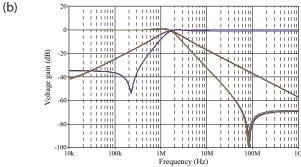

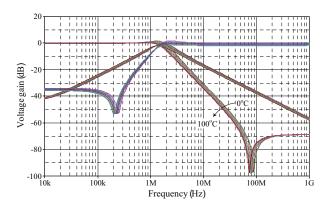

From Table 9, the area comparison of 2<sup>n</sup>-1 SRM shows that the proposed architecture I & II requires less area compared to other multipliers [14][22][23]. The synthesis results show that the proposed design I occupy 17% - 22%, and design II occupies a 10% lesser area than existing modulo MBE. Delay analysis indicates that the proposed-I has a 17% - 24% speed improvement, and Proposed-II excels in speed by 26% - 30%. Power analysis shows that the total power required for the design is almost the same compared to recent works.

In 2<sup>n</sup>+1 SRM architectures, the proposed designs outperforms the other multipliers in area efficiency and speed improvement [15,16,17,18,19,20,21]. Proposed architecture I save area in the range of 23% - 44%, whereas the proposed architecture II reduces the area in the range of 10% - 32% compared to existing MBE architectures. The speed improvement of proposed-I and II lies between the ranges of 10% - 35% and 20% - 39%, respectively. The power profiles of the proposed

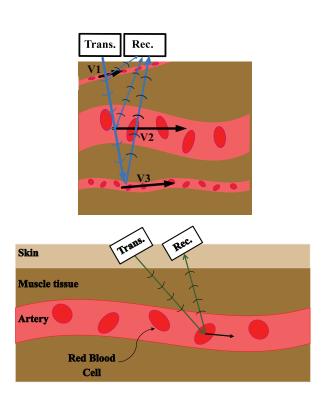

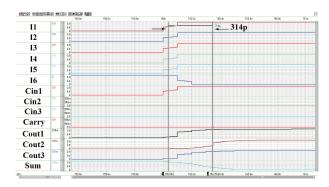

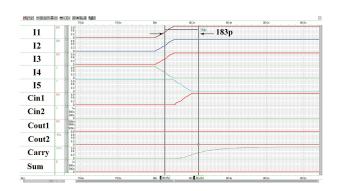

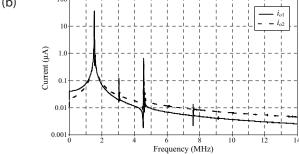

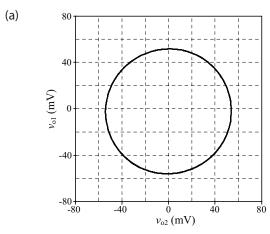

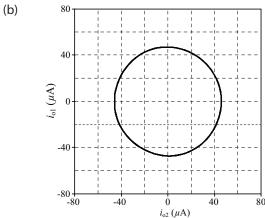

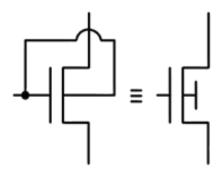

Figure 9: Simulation result of RNS processor

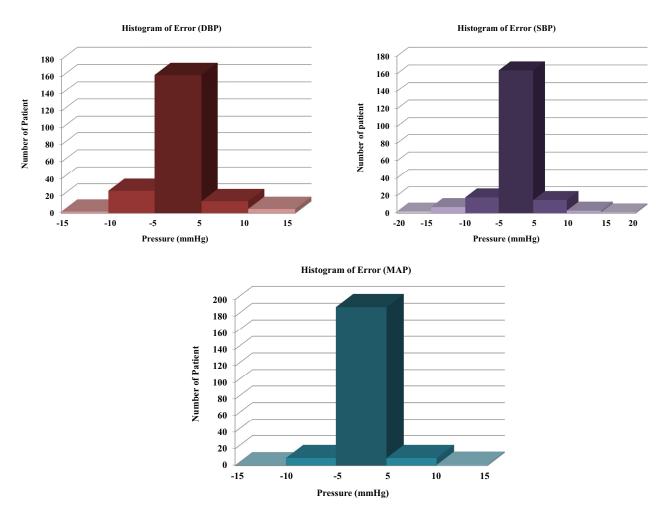

multipliers are almost the same as that of recent works. Since the proposed unbalanced residue multipliers are derived from proposed balanced residue multipliers, they follow the same trend in the area, delay, and power metrics, which are presented in Table 10.