# structuration d'un systeme téléphonique informatisé

m.exel m.mekinda b.popovič

UDK 621,395,345:681,3.06

\*Institut J.Stefan, Jamova 39, 61000 Ljubljana Iskra, ATC Labora, Savska Loka 4, 64000 Kranj

Dans le présent article nous appliquons les principes de la programmation structurée et (pseudo)parallète pour analyser et restructurer – au mayen d'un langage de haut niveau utilisant le concept de moniteur – un système téléphonique informatisé concret.

Članek opisuje aplikacijo principov strukturiranega in (navidezno) paralelnega programiranja. Predmet aplikacije je analiza in strukturiranje konkretnega programskega sistema telefonske centrale s pomočjo-visoko nivojskega programskega jezika, ki upo-rablja monitorski koncept.

#### I. INTRODUCTION

Nous nous proposons ici d'analyser et de restructurer un système téléphonique informatisé concret en nous appuyant sur les concepts de programmation structurée et de programmation (pseudo-)parallèle. Ceci n'est pas une étude théorique; nous essayons simplement d'éxaminer l'applicabilité des concepts mentionnés à un système en temps réel: le système téléphonique considéré. La parution récente de quelques articles (5,14) traitont de la programmation en temps réel en liaison avec les méthodes de structuration des systèmes d'exploitation et avec les langages pour la programmation parallèle nous a encouragé à pracéder de la sorte.

Les motivations de cette étude sont pratiques: il s'agit de la maintenance, de l'adaptation et des modifications du système informatisé des centraux téléphoniques du type Metaconta 10C Local, réalisé avec les ordinateurs ITT-1600 et 3200. Le logiciel du système est programmé en assembleur et toute modification est difficile. Ceci nous a amené à étudier une restructuration possible du système qui permette:

- des modifications aisées et facilement vérifiables;

- une compréhension meilleure du système et, éventuellement,

une amélioration du degré de parallélisme (potentiel) des

- une amélioration du degré de parallélisme (potentiel) des différents éléments du système.

Nous présentons dans les chapitres suivants une analyse et une structuration de ce système téléphonique en termes de procéssus coopérants, une description de cette structuration dans un langage qui est pratiquement le Pascal parallèle (2,16) et, finalement, nous discutons des problèmes que pose l'organisation de cette structuration.

## II. PRÉSENTATION ET ANALYSE DU SYSTEME

#### 1. Présentation schématique du système

Le système du central téléphonique considéré comprend le matériel suivant: un ou deux ordinateurs 17T-1600 et une périphérie téléphonique comprenant des terminaux d'entrées-sorties, des terminaux de liaison, des éléments de liaison entre ces terminaux et des circuits de tests, de marquage et de pilotage dirigeant ces terminaux. Les terminaux d'E/S sont reliés par des canaux à l'envitonnement que composent des appareils téléphoniques, d'autres centraux etc...

L'organisation physique de la périphérie téléphonique est modulaire: cette périphérie se compose d'un module de signalisation et au plus de dix modules périphériques. Un module périphérique est composé d'un certain nombre de terminaux (d'E/S et de liaison) et d'éléments de liaison que dirigent un circuit de marquage, trois circuits de tests de types différents et jusqu'à trois circuits de pilotage de types lent, normal et rapide. Nous ne tiendrons pos compte dans la suite de la périphérie classique des ordinateurs.

Fonctionnellement nous distinguons dans ce système du central deux sous-systèmes: le système de contrôle réalisé sur les ordinateurs et le système de coopération avec l'environnement réalisé par la périphérie téléphonique. Le système de contrôle contrôle le système de coopération et traite les messages que ce dernier lui communique alors que le système de coopération détecte les signaux provenant do l'environnement, envoie des signaux à ce dernier et établit des ligisons entre les conaux connectés à l'environnement.

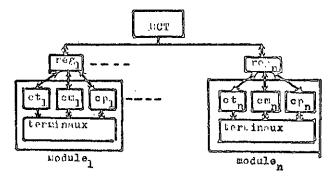

Dans la suite nous considérerons un système simplifié comprenant une seule unité centrale de traitement et n modules périphériques dont chacun, relié à l'UCT par un registro périphérique, contient un circuit de tests, un circuit de marquage et un circuit de pilotage de type normal. Un schéma partiel de ce système est présenté dans la figure 1.

ct: circuit de teste

em: circuit de marquage

eps circuit de pilotage normal

Figure 1.

## 2. Processus du systeme: identification et coopération

Nous analysons ici les deux systèmes de contrôle et de coopération en termes de processeurs et de processus séquentiels permanents et coopérants.

Le système du central comprend un processeur principal (l'UCT), un processeur d'horloge à période de 10 msec et les trois fais n processeurs périphériques de tests, de marquage et de pilotage qui sont constitués des circuits correspondants des n modules périphériques et des terminaux de la périphérie téléphonique multipléxés sur ces circuits.

Les processus du système de contrôle se déroulent sur le processeur principal et sur le processeur d'harlage et sont appelés processus internes alors que les processus du système de coopération se deroulent sur les processeurs périphériques de tests, de marquage et de pilotage et sont appelés processus externes (voir la terminologie de (1)) de même nom, respectivement.

Les processus externes de tests réalisent la détection - par l'examen des points de tests des terminaux - des signaux parvenant de l'environnement; les processus externes de pilotage réalisent l'envoi des signaux à l'environnement par l'établissement des l'aisons entre les terminaux et les canaux de l'environnement; enfin, les processus externes de marquage réalisent des liaisons entre les terminaux. Il y a quatre groupes de processus internes: les processus internes de tests, de traitement, de marquage et de pilotage, dénotés de facon générique par pt, ptr, pm et pp, respectivement.

Les fonctions de ces processus sont les suivantes: un processus pt détermine un ensemble de points de tests et active un processus externe de tests sur un processour périphérique donné en lui envoyant une commande par le registre périphérique associé au processeur. Le processus externe prépare sa "réponse" dans le meme registre périphérique qui doit rester occupé par ce processus pendant son activité. Le processus pt analyse ensuite la réponse, envoie un message par l'intermédiaire d'une mémoire-tampon à un processus ptr couplé a pt et reprend la procédure au début jusqu'à ce que l'ensemble de points de tests soit traité. Les processus internes de tests sont activés périodiquement par l'interruption de l'horloge et les différents processus pt se déroulent alors sequentiellement.

Un processus ptr analyse les messages reçus de pt et envoie, en fonction du message reçu, un message à un processus pm ou pp par l'intermediaire d'une mémoire-tampon ce qui entraîne une interruption activant op ou pm.

Un processus pp ou pm reçoit des messages des processus ptr et active un processus externe de pilotage ou de marquage, en lui envoyant une commande par le registre périphérique. Le processus externe activé occupe le registre tant que la commande n'est par lue et indique la fin de son activité par une interruption ce qui permet de continuer le processus interne qui l'a activé. Le processus externe n'envoie pas d'autre "réponse".

Nous voyons danc qu'il existe une communication entre les processus internes et externes et entre les différents processus internes. Cette communication se fait par les registres périphériques et les mémoires tampons; ces éléments représentent des ressources partagées que les processus devrans allouer et déallouer dans notre description du système. D'autres ressources partagées sont les processeurs périphériques qui devront être alloués avant l'activation des processus externes se déraulant sur ces processeurs.

L'occupation exclusive des ressources partagées est assurée dans le système actuel par l'exécution sérielle des processus internes. La communication entre les processus du système actuel n'est ni sûre (des messages peuvent se perdre) ni

suffisamment souple pour permettre d'exploiter le parallétisme potentiel des processus du système. Nous proposons donc une restructuration du système exposée ci-dessous.

### Structuration du système

Le système est envisagé comme un ensemble de processus internes séquentiels et permanents (cyclant indéfiniment) dont la coopération est assurée par un unsemble de moniteurs (pour le concept de moniteur voir 1,2,3,4,7,11,12,13,16), disposés en hierarchie et gérant les ressources du système.

Le noyau du système n'est pas explicité; nous supposons qu'il contient essentiellement un programme d'ordonnancement ("scheduler – dispatcher") des processus internes, les routines pour le traitement des interruptions et deux primitives de communication entre les processus: "bloquer" et "déblaquer". Ces deux primitives sont appelées dans les moniteurs et appellent à leur tour le programme d'ordonnancement. Nous supposons un ordonnancement tres simple des processus internes: absence de priorités et stratégie "premier arrivé – premier servi". Notons que la procédure "débloquer" ne provoque pas nécessairement l'activation immédiate du processus débloqué éventuel (nous ne suivons danc pos la stratégie de Hoare et de Brinch Hansen – cf. 2,7 – mais celle, plus générale, exposée dans 18).

Dans le système observé n'existent que deux types d'interruptions: l'interruption de l'horloge et les interruptions provoquées par les processeurs de marquage et de pilotage. Ces interruptions sont "interceptées" par le noyau (qui active par la suite le programme d'ordonnancement) et finalement "acheminées" aux procédures adéquates des moniteurs gérant les processeurs de marquage, de pilotage et l'horloge.

L'occupation exclusive des ressources partagées est assurde par l'inhibition des interruptions dans les procédures des moniteurs ce qui a pour effet l'exclusion "globale" (cf. 11) de ces procédures.

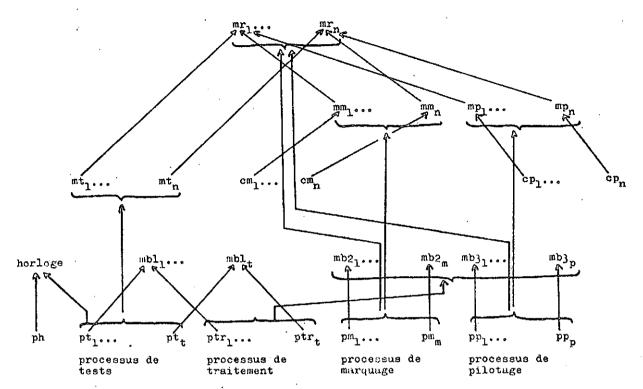

Le système proposé se compose d'éléments suivants;

- processus internes:

- les processus de tests, notés pt;, i = 1...t

- les processus de traitement, notés ptr;, i=1...t

- les processus de marquage, notés  $pm_1$ , i = 1 ... m

- les processus de pilotage, notés pp;; i = 1..p;

moniteurs:

- les moniteurs des processeurs de tests, notés mt; , i = 1...n

- les moniteurs des processeurs de marquage, notés mm;

i = 1...n

- les moniteurs des processeurs de pilotage, notés mp; ,i=1..n

- les moniteurs des registres périphériques, notés mri, i=1..n

- les moniteurs notés mbli, i=1...t, gérant la communication entre les paires des processus pti - ptri

- les moniteurs notés mb2; , i=1..m, gérant la communication entre les processus ptr et les processus pm;

- les moniteurs notés mb3;, i=1..p, gérant la communication entre les processus ptr et les processus pp; et

- le moniteur noté miemp gérant l'interruption de l'hortage.

L'organisation du système est représentée par le graphe de la figure 2. Sur ce graphe apparaissent aussi le processus d'horloge noté ph et les processus externes de marquage et de pilotage, notés cp; et cmi, i=1..n. Les arcs du graphe représentent les accès (appels) admis dans le système (une interruption étant ici interprétée comme un appel à la procédure d'interruption – de moniteur – correspondante). L'arc partant d'une accolade (resp. aboutissant à une accolade) représente autant d'arcs partants (resp. aboutis-sants) qu'il y a de processus ou de moniteurs reunis par l'accolade.

Figure 2.

### III. DESCRIPTION DE LA STRUCTURATION PROPOSÉE

Différentes structurations du système sont possibles; elles sont essentiellement fonction du choix des moniteurs. La structure choisie a les effets suivants:

- en allouant d'abord les processeurs de tests, de marquage et de pilotage et ensuite les registres correspondants nous obtenons des files d'attende (sur ces ressources) plus courtes que dans le cas des séquences d'allocation inverses;

- il est possible que les processus externes de marquage et de pilotage d'un même madule périphérique se déroulent en parallèle;

- en définissant un moniteur pour chaque ressource nous diminuons le temps passé dans chacune des procédures des moniteurs.

# 1. Données globales

Ces données globales peuvent être référencées dans tous les moniteurs et dans tous les processus.

Les constantes: t,m,p,n,blon1,blon2,blon3.

Les types:

```

type liste-t = array[1..t] of queue;

liste-m = array[1..m] of queue;

liste-p = array[1..p] of queue;

liste-r = array [1..2] of queue;

mess1 = { ... }; mess2 = { ... }; mess3 = { ... };

tamp1 = array[1..blon1] of mess1;

tamp2 = array[1,.blon2] of mess2;

tamp3 = array [1..blon3] of mess3;

```

type paps = closs (long: integer); { cf.(15), p.169: une file "premier arrivé - premier servi" |

var tête,q,1: integer; function entry arrivé: integer; begin arrivé:=q; q:=q mod long + 1; 1:=1 + 1; end; function entry déport: integer; begin départ:=tête, tête:=tête mod long + 1; 1:=1 - 1;end; function entry vide; boolean; hegin vide:=(1=0) end;

function entry plein: boolean; begin plein:=(1=long) end; begin tête:=1; q:=1; 1:=0; end; Les primitives du noyau: procedure bloquer (var q:queue); bloquer le processus courant dans q; quitter le moniteur et oppeler le programme d'ordonnancements; procedure débloquer (var q: queue); {débloquer le processus dans q; quitter le moniteur et appeler le programme d'ordonnancement { ; function vide (var q:queue):boolean; vrai si pas de processus en attente dans q ? .

## 2. Moniteurs

a) Allocateur de processeurs de tests type mit= monitor(monreg: mr) var libre: boolean; liste: liste-t; prochain: paps; procedure entry allouer; begin while not libre do bloquer (liste [prochain.arrive]); libre: = folse; monreg.allover; end; procedure entry deallouer; begin monreg. déallouer; libre; = true; if not prochain.vide then debloquer(liste[prochain.depart]); end; begin libre;≈true; init prochain(t) end; On peut declarer alors n moniteurs du type mt dont chacun est associé à un moniteur du type mr (voir plus bas): var mtl:mt; ovec init mtl(mrl);

b) Allocateurs de processeurs de marquage et de pilotage type mm= monitor(monreg:mr) var libre:boolean; liste:liste-m; prochain:paps; inter:boolean; attinter:queue; procedure entry allouer;

```

On déclarera m moniteurs du type mb2 et p moniteurs

begin while not libre do bloquer(liste[prochain.arrive]);

du type mb3:

libre: = false:

var mb21: mb2,...

mb31: mb3, . . .

monreg.allover;

inter:=false; { le signal d'interruption }

f) Le moniteur de l'horloge

end;

type mtemp=

procedure entry déallover;

monitor

begin if not inter then bloquer(attinter);

var attliste: liste-t; {contient les processus pt; qui ant fini leurs

{attendre l'interruption }

cycles et attendent l'interruption de l'horloge pour

libre: = true:

recommencer un nouveau cycle}

if not prachain.vide then debloquer(liste[prochain.depart]);

prochain:paps;

procedure entry ottendre;

procedure entry minter; ["intercepte" l'interruption du circuit

begin bloquer(attliste [prochain.arrive]) end;

de marquage }.

procedure entry tempinter; { l'interruption de l'horloge }

begin inter:=true;

begin while not prochain vide

if not vide(attinter) then debloquer(attinter);

do débloquer(attliste[prochain.départ])

end:

begin libre:=true; inter:=folse; init prochain(m) end;

begin init prochain(t) end;

type mp=∫analogue au type mm }.

Declaration: var horloge:mtemp;

On pourra déclarer n moniteurs du type mm et n moniteurs

du type

Processus

mp par:

a) Processus de tests

var mml;mm; avec init mml(mrl); etc...

type pt=

c) Allocateur de registre périphérique

process (heure:mtemp; buf:mb1; accestl', {...}, accestn: mt);

type mr≈

var circuitest: 1...n; mess:mess1;

monitor

begin

var libre:boolean; liste:liste-r; prochain:paps;

cycle

procedure entry allover; .

[initialisation: déterminer les tests }

begin while not libre do bloquer(liste[prochain.arrive]);

repeat

libre: = false;

case circuitest of liaccestlallouer;

end:

envoi de la commande au processeur de tests

procedure entry déallouer;

correspondant en utilisant le registre correspondant;

begin libre:=true;

delai "actif"A; examen de la reponse reçue dans le

if not prochain vide then debloquer

registre }

(liste[prochain.depart]);

case circuitest of 1:accest1.deallouer;

end;

On déclarera n moniteurs du type mr par:

{preparer le message pour le processus ptr correspondant}

buf.envoyer(mess);

vor mrl; mr; etc...

until } fin de tests du cycle };

d) Allocateur de mémoire-tampon du type mb1

heure attendre;

type mb1=

end:

monitor

var mb:tamp1; prochain:paps; source, destination:queue;

Les processus de type pt sont déclarés et initialisés par:

procedure entry envoyer(m: mess1);

var ptl:pt; init ptl(horloge,mbl1,mtl,mt2,{...\,mtn); etc..

begin if prochain.plein then bloquer(source);

mb[prochain.arrive]: = m;

b) Processus de traitement

if not vide (destination) then debloquer (destination);

type ptr=

end;

process(buf: mb1; tamp1, \{...\}, tampm: mb2; tam\{...\},

procedure entry recevoir(var m:mess1);

tamp: mb3);

begin if prochain.vide then bloquer(destination);

var ml:massl; m2:mass2; m3:mass3;

m:= mb[prochain.depart];

begin

if not vide(source) then debloquer(source);

cycle buf.recevoir(ml);

end:

{traitement du message}

begin init prochain(blon!) end;

\ldots { tamp; . envoyer(m2) \ldots tam; . envoyer(m3) \} \ldots

On déclarera i moniteurs de type mb1: var mb11: mb1; etc....

end:

end;

a) Allocateurs des mémoires-tampons du type mb2 et mb3

Ces processus sont déclarés et initialises par:

type mb2=

var ptrl :ptr;    init ptr}(mbl1,mb21,{...},mb31,{...},mb3p);

monitor

var mb: tamp2; prochainproc, prochaintamp: paps;

c) Processus de pilotage et de marquage

source: liste-t; destination: queue;

type pm=

procedure entry envoyer(m: mess2);

process/huf: mb2; accesm1, {...}, accesmn: mn;

begin while prochaintamp.plein do bloquer

accessif, { . . . }, accessin : mr);

(source | prochainproc.arrive |);

var circuitmarq: 1..n; mess: mess2; .

mb[prochaintamp.arrive] := m;

if not vide(destination) then débloquer(destination);

{initialisation}

end;

.cycle buf.recevoir(mess);

{preparer l'action adéquate}

procedure entry recevoir(var m: mess2);

begin if prochaintamp.vide then bloquer(destination);

case circuitmarq of 1:accèsml.ollover;

m:=mb[prochaintamp.depart];

fenvoi de la commande au processeur de marquage

if not prochainproc.vide then

correspondant en utilisant le registre correspondant?

debloquer(source [ prochainproc.départ ]);

case circuitmary of 1: begin access1.deallouer;

accesmi.deallover;

begin init prochainproc(t), prochaintamp(blon2) end;

end:

type mb3 = \{analogue au type <math>mb2\}.

```

endi

end:

Ces processus sont déclarés et initialisés par: var pml:pm; init pml(mb21,mml,{...},mmn,mrl,mr2,{...},mrn); etc... type pp= { analogue au type pm}.

#### IV. CONCLUSION

Le fonctionnement correct du système décrit en III (ainsi que celui du système original) est basé sur l'hypothèse suivante: l'intervalle de temps entre deux interruptions de l'horloge est sufisamment long pour que, en fin d'intervalle:

- tous les processus pt soient bloqués dans la liste "attliste",

- aucun des messages ne soit perdu et ,

- tous les processus externes soient terminés.

Partant de cette hypothèse de base nous pouvons supposer que le système structure proposé ici assure un déroulement harmonieux des processus du système c.a.d. sans bloquage des processus (cf. 1).

En effet, d'une part, nous avons dans le système une allocation hiérarchique des ressources permanentes (processeurs périphériques et registres) et, d'autre part, une communication de messages hiérarchique entre les processus internes du système (les processus pt envoient des messages aux processus ptr et ces derniers envoient des messages aux processus pm et pp).

L'implantation du système propose est basée sur l'hypothèse d'un seul processeur central et est la plus simple possible (les moniteurs sont réalises par l'inhibition des interruptions). On peut bien évidemment envisager une implantation plus sophistiquée et plus complexe (cf. 17):

- en supposant plusieurs processeurs centraux et/ou

- en introduisant les sémophores pour assurer une exclusion "localé" des procédures des moniteurs.

Une telle implantation rendrait possible une amélioration théorique du degre de parallélisme des differents processus du système mais – etant donné les temps très courts des cycles des processus – serait probablement prohibitive relativement aux temps d'accès aux moniteurs.

Nous pensons que la restructuration proposée du système du central peut, d'une part, servir à modéliser le système et à le simuler et, d'autre part, peut servir comme point de depart d'une configuration nouvelle du système.

## **BIBLIOGRAPHIE**

- (1) Brinch Hansen P.: Operating system principles, Prentice-Hall, 1973.

- (2) Brinch Hansen P.: The programming language Concurrent Pascal, IEEE trans. on software eng.vol. SE-1, no. 2, 1975.

- (3) Brinch Hansen P.: A programming methodology for operating system design, IFIP 1974.

- (4) Dijkstro E.W.: Hierarchical ordering of sequential processes, Operating systems techniques, Academic Press, 1972.

- (5) Gordon R.L.: Systems of cooperating schedulers, IFAC-IFIP workshop on real-time programming, 1975.

- (6) Haberman A.N.: Introduction to operating system design, SRA 1976.

- (7) Hoare C.A.R.: Monitors: an operating system structuring concept, CACM, oct. 1974, p. 549.

- (8) Horning J.J., Rondell B.: Process structuring, Computing surveys, vol. 5, no.1, 1973.

- (9) 177: Standard computer modules 177 1600, 160 177 11000E, 1968.

- (10) Jensen K., Wirth N.: Pascal-user manual and report, Springer-Verlag, 1975.

- (11) Lister A.M., Maynard K.J.: An implementation of monitors, Software-practice & experience, vol. 6, 377– 385, 1976.

- (12) Lister A.M., Sayer P.J.: Hierarchical monitors, Proc. 1976 internat. conf. on parallel processing.

- (13) Schmid H.A.: On the efficient implementation of conditional critical regions & the construction of monitors, Acta Informatica 6, 1976.

- (14) Smedema C.H.: Real-time concepts and Concurrent Pascal, IFAC-IFIP workshop on real-time programming, 1975.

- (15) Brinch Hansen P.: The solo operating system: processes, monitors & classes, Software-practice & experience, vol.6, 165-200, 1976.

- (16) Brinch Hansen P.: Concurrent Pascal report, Cal.tech.,

- (17) Wettstein H.: The implementation of synchronizing operations in various environments, Software-practice & experience, vol.7, 115-126, 1977.

- (18) Wettstein H.: The problem of nested monitor culls revisited, Oper Systems Review, vol.12, no.1, 1978.

- (19) Popović B., Exel M., Mekinda M.: Primjena monitorskog koncepta u izgradnji operacionog sistema za periodično aktiviranje programa. J. Informatica, 1977, no. 2.

- (20) Mekinda M., Exel M., Popović B.: Strukturiranje programsko vodjenog sistemo telefonske centrale, XII. jug. medn. simpozij o obravnovanju podatkov, Bled, oktober 1977, 6-116.