# Informacije MIDEM

Journal of Microelectronics, Electronic Components and Materials Vol. 50, No. 1(2020), March 2020

Revija za mikroelektroniko, elektronske sestavne dele in materiale letnik 50, številka 1(2020), Marec 2020

## Informacije MIDEM 1-2020 Journal of Microelectronics, Electronic Components and Materials

#### VOLUME 50, NO. 1(173), LJUBLJANA, MARCH 2020 | LETNIK 50, NO. 1(173), LJUBLJANA, MAREC 2020

Published quarterly (March, June, September, December) by Society for Microelectronics, Electronic Components and Materials - MIDEM. Copyright © 2020. All rights reserved. | Revija izhaja trimesečno (marec, junij, september, december). Izdaja Strokovno društvo za mikroelektroniko, elektronske sestavne dele in materiale – Društvo MIDEM. Copyright © 2020. Vse pravice pridržane.

#### Editor in Chief | Glavni in odgovorni urednik

Marko Topič, University of Ljubljana (UL), Faculty of Electrical Engineering, Slovenia

#### Editor of Electronic Edition | Urednik elektronske izdaje

Kristijan Brecl, UL, Faculty of Electrical Engineering, Slovenia

#### Associate Editors | Odgovorni področni uredniki

Vanja Ambrožič, UL, Faculty of Electrical Engineering, Slovenia Arpad Bürmen, UL, Faculty of Electrical Engineering, Slovenia Danjela Kuščer Hrovatín, Jožef Stefan Institute, Slovenia Franc Smole, UL, Faculty of Electrical Engineering, Slovenia Matjaž Vidmar, UL, Faculty of Electrical Engineering, Slovenia

#### Editorial Board | Uredniški odbor

Mohamed Akil, ESIEE PARIS, France Giuseppe Buja, University of Padova, Italy Gian-Franco Dalla Betta, University of Trento, Italy Martyn Fice, University College London, United Kingdom Ciprian Iliescu, Institute of Bioengineering and Nanotechnology, A\*STAR, Singapore Marc Lethiecq, University of Tours, France Teresa Orlowska-Kowalska, Wroclaw University of Technology, Poland Luca Palmieri, University of Padova, Italy Goran Stojanović, University of Novi Sad, Serbia

#### International Advisory Board | Časopisni svet

Janez Trontelj, UL, Faculty of Electrical Engineering, Slovenia - Chairman Cor Claeys, IMEC, Leuven, Belgium Denis Đonlagić, University of Maribor, Faculty of Elec. Eng. and Computer Science, Slovenia Zvonko Fazarinc, CIS, Stanford University, Stanford, USA Leszek J. Golonka, Technical University Wroclaw, Wroclaw, Poland Jean-Marie Haussonne, EIC-LUŚAC, Octeville, France Barbara Malič, Jožef Stefan Institute, Slovenia Miran Mozetič, Jožef Stefan Institute, Slovenia Stane Pejovnik, UL, Faculty of Chemistry and Chemical Technology, Slovenia Giorgio Pignatel, University of Perugia, Italy Giovanni Soncini, University of Trento, Trento, Italy Iztok Šorli, MIKROIKS d.o.o., Ljubljana, Slovenia Hong Wang, Xi'an Jiaotong University, China

#### Headquarters | Naslov uredništva

Uredništvo Informacije MIDEM MIDEM pri MIKROIKS Stegne 11, 1521 Ljubljana, Slovenia T. +386 (0)1 513 37 68 F. + 386 (0)1 513 37 71 E. info@midem-drustvo.si www.midem-drustvo.si

Annual subscription rate is 160 EUR, separate issue is 40 EUR. MIDEM members and Society sponsors receive current issues for free. Scientific Council for Technical Sciences of Slovenian Research Agency has recognized Informacije MIDEM as scientific Journal for microelectronics, electronic components and materials. Publishing of the Journal is cofinanced by Slovenian Research Agency and by Society sponsors. Scientific and professional papers published in the journal are indexed and abstracted in COBISS and INSPEC databases. The Journal is indexed by ISI o for Sci Search ``, Research Alert ``and Material Science Citation Index '``. '

Letna naročnina je 160 EUR, cena posamezne številke pa 40 EUR. Člani in sponzorji MIDEM prejemajo posamezne številke brezplačno. Znanstveni svet za tehnične vede je podal pozitivno mnenje o reviji kot znanstveno-strokovni reviji za mikroelektroniko, elektronske sestavne dele in materiale. Izdajo revije sofinancirajo ARRS in sponzorji društva. Znanstveno-strokovne prispevke objavljene v Informacijah MIDEM zajemamo v podatkovne baze COBISS in INSPEC. Prispevke iz revije zajema ISI® v naslednje svoje produkte: Sci Search®, Research Alert® in Materials Science Citation Index™

## Content | Vsebina

| Original scientific papers                                                                                                                                                                                                       |    | Izvirni znanstveni članki                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Editorial                                                                                                                                                                                                                        | 2  | Uvodnik                                                                                                                                                                                                   |

| F. K. Jérôme, W. T. Evariste, E. Z. Bernard,<br>M. L. Crespo, A. Cicuttin, M. B. I. Reaz,<br>M. A. S. Bhuiyan, M. E. H. Chowdhury:<br>A 0.35µm Low-Noise Stable Charge Sensitive<br>Amplifier for Silicon Detectors Applications | 3  | F. K. Jérôme, W. T. Evariste, E. Z. Bernard,<br>M. L. Crespo, A. Cicuttin, M. B. I. Reaz,<br>M. A. S. Bhuiyan, M. E. H. Chowdhury:<br>Nizkošumen stabilen ojačevalnik za silicijeve<br>detektorje         |

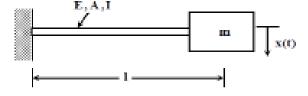

| X. Huang, D. Zhang, Z. Wang:<br>Back Propagation Neural Network in Predicting the<br>Thermal Fatigue Life of Microelectronic Chips                                                                                               | 15 | X. Huang, D. Zhang, Z. Wang:<br>Nevronske mreže z vzvratnim širjenjem pri<br>napovedovanju temičnega utrujenosti<br>mikroelektronskega čipa                                                               |

| M. Kikelj, B. Lipovšek, M. Topič:<br>Optimisation of Front Metallisation Pattern in<br>Silicon Solar Cells for Annual Energy Yield                                                                                               | 25 | M. Kikelj, B. Lipovšek, M. Topič:<br>Optimizacija sprednje metalizacije silicijevih<br>sončnih celic na nivoju letnega donosa energije                                                                    |

| P. B. Petrović:<br>Simple CMOS Square Wave Generator<br>with Variable Mode Output                                                                                                                                                | 35 | P. B. Petrović:<br>Enostaven CMOS generator kvadratnega vala s<br>spremenljivim izhodom                                                                                                                   |

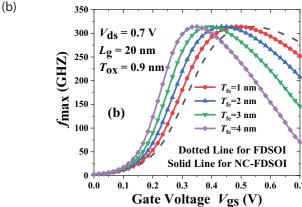

| P. Si, K. Zhang, T. Yu, Z. Zhao, W. Lü:<br>Analog / Radio-Frequency Performance Analysis of<br>Nanometer Negative Capacitance Fully Depleted<br>Silicon-On-Insulator Transistors                                                 | 47 | P. Si, K. Zhang, T. Yu, Z. Zhao, W. Lü:<br>Analogna in radio frekvenčna analiza učinkovitosti<br>nanometrskega polno osiromašenega silicijevega<br>tranzistorja na izolatorju z negativno kapacitivnostjo |

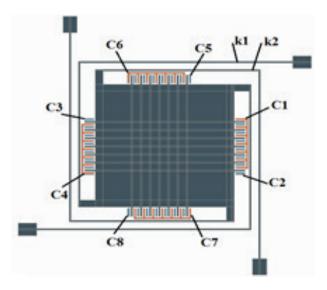

| B. A. Ganji, K. D. Hemmati:<br>A Design and Optimization of a New, Three-Axis<br>MEMS Capacitive Accelerometer with High<br>Dynamic Range and Sensitivity                                                                        | 55 | B. A. Ganji, K. D. Hemmati:<br>Zasnova in optimizacija novega troosnega<br>MEMS kapacitivnega pospeškometra z velikim<br>dinamičnim območjem in visoko občutljivostjo                                     |

| Announcement and Call for Papers 56 <sup>th</sup> international Conference on Microelectronics, Devices and Materials with the Workshop on Personal Sensor for Remote Health Care Monitoring                                     | 67 | Napoved in vabilo k udeležbi:<br>56. Mednarodna konferenca o mikroelektroniki,<br>napravah in materialih z delavnico o osebnem<br>senzorju za daljinsko spremljanje zdravstvene nege                      |

| Front page:<br>Bottom-up, spatially resolved solar cell modelling.<br>(M. Kikelj et al.)                                                                                                                                         |    | Naslovnica: Prostorno modeliranje sončnih celic od spodaj navzgor. (M. Kikelj et al.)                                                                                                                     |

### Editorial | Uvodnik

#### Dear reader,

Year 2019 ran out and this editorial brings up some statistics about manuscripts submitted in the previous year. In 2019 we received more than 110 manuscripts, out of which only 19 have been accepted for publication so far, while 22 were out of scope and 56 manuscripts were rejected. The number of manuscript submissions that are out of the journal's scope has been drastically reduced. The success rate remains below 20% in 2019 and reflects determination for quality that will path long-term quality growth. Citation metrics with JCR IF-2018=0.476, SNIP-2018=0.265 and CiteScore-2018=0,61 is an important performance indicator. In 2019 we published 26 original scientific papers and I sincerely thank all reviewers and Editorial Board Members for their valuable contribution to the journal.

Year 2019 was also a milestone year for our journal. On 25 Sep 2019 our journal was accepted to the growing DOAJ family of open-access journals (Informacije MIDEM – Journal of Microelectronics, Electronic Components and Materials). Next to a digital object identifier (DOI) to all papers, the papers are accessible from WoS, Scopus or DOAJ by a single mouse click. We sincerely hope that the open-access papers will help us in wider dissemination and larger readeship.

This issue marks another milestone. We have been publishing our journal for half of a century and it is my great honor and privilege to express gratitude to all, who served as editors, reviewers and authors of Informacije MIDEM – Journal of Microelectronics, Electronic Components and Materials in 49 volumes so far. Certainly, with this editorial we are starting the 50th volume and the 50th year of continuous publishing. As a part of your success in science and engineering we commit ourselves to continue serving you and look forward to receiving your future manuscript(s) on our submission page (http://ojs.midem-drustvo.si/).

Last but not least, do not let the covid-19 pandemic harm joy and peace in each home, office or research laboratory. Stay safe and healthy!

Prof. Marko Topič Editor-in-Chief

31 March 2020

https://doi.org/10.33180/InfMIDEM2020.101

## A 0.35µm Low-Noise Stable Charge Sensitive Amplifier for Silicon Detectors Applications

Folla Kamdem Jérôme<sup>1,3</sup>, Wembe Tafo Evariste<sup>2</sup>, Essimbi Zobo Bernard<sup>1</sup>, Maria Liz Crespo<sup>3</sup>, Andres Cicuttin<sup>3</sup>, Mamun Bin Ibne Reaz<sup>4</sup>, Mohammad Arif Sobhan Bhuiyan<sup>5</sup>, Muhammad Enamul Hoque Chowdhury<sup>6</sup>

**Abstract:** The Charge Sensitive Amplifier (CSA) is the key module of the front-end electronics of various types of Silicon detectors and most radiation detection systems. High gain, stability, and low input noise are the major concerns of a typical CSA circuit in order to achieve amplified susceptible input charge (current) for further processing. To design such a low-noise, stable, and low power dissipation solution, a CSA is required to be realized in a complementary metal-oxide-semiconductor (CMOS) technology with a compact design. This research reports a low-noise highly stabile CSA design for Silicon detectors applications, which has been designed and validated in TSMC 0.35 um CMOS process. In a typical CSA design, the detector capacitance and the input transistor's width are the dominant parameters for achieving low noise performance. Therefore, the Equivalent Noise Charge (ENC) with respect to those parameters has been optimized, for a range of detector capacitance from 0.2 pF – 2 pF. However, the parallel noise of the feedback was removed by adopting a voltage-controlled NMOS resistor, which in turn helped to achieve high stability of the circuit. The simulation results provided a baseline gain of 9.92 mV/fC and show that ENC was found to be 42.5 e–with 3.72 e–/pF noise slope. The Corner frequency exhibited by the CSA is 1.023 GHz and the output magnitude was controlled at -56.8 dB; it dissipates 0.23 mW with a single voltage supply of 3.3 V with an active die area of 0.0049 mm².

Keywords: CMOS; CSA; Front-End; Low- noise; Silicon detector

## Nizkošumen stabilen ojačevalnik za silicijeve detektorje

**Izvleček:** Na naboj občutljiv ojačevalnik (Charge Sensitive Amplifier - CSA) je osnovni del vhodne elektronike različnih silicijevih senzorjev in večine sistemov detekcije sevanja. Veliko ojačenje, stabilnost in nizek šum so glavne zahteve tipičnih CSA vezij za doseganje zadovoljivega ojačenja naboja (toka) za nadaljnje procesiranje. Za razvoj nizko šumne, stabilne rešitve z nizko porabo mora biti CSA realiziran v kompaktni CMOS tehnologiji. V delu predstavljamo nizko šumen, stabilen CSA za silicijev detektor, ki je bil preverjen v TSMC 0.35 um CMOS tehnologiji. V tipičnem CSA sta kapacitiven detektor in vhodna širina tranzistorja glavna parametra za doseganje nizkega šuma. Ekvivalenten šumni naboj ej bil optimiran za detektiranja kapacitivnosti v razponu od 0.2 pF – 2 pF. Paralelni šum povratne vezave je bil odstranjen z napetostno krmiljenim uporom, ki je pripomogel tudi k stabilnosti vezja. Simulacije so pokazale ojačenje 9.92 mV/fC in ENC 42. 5 e– z naklonom 3.72 e–/pF. Vogalna frekvenca CSA je 1.023 GHz, in kontroliranim izhodnim signalom pri -56.8 dB. Poraba moči je 0.23 mW pri 3.3 V napajanju in aktivni površini 0.0049 mm².

Ključne besede: CMOS; CSA; vhod; nizek šum; silicijev detektor

<sup>&</sup>lt;sup>1</sup>University of Yaoundé I, Faculty of Science, Department of Physics, Cameroon

<sup>&</sup>lt;sup>2</sup>University of Douala. Faculty of Science, Department of Physics, Cameroon

<sup>&</sup>lt;sup>3</sup>International Center for Theoretical Physics (ICTP), Trieste, Italy

<sup>&</sup>lt;sup>4</sup>Universiti Kebangsaan Malaysia, Centre of Advanced Electronic and Communication Engineering, Selangor, Malaysia

<sup>&</sup>lt;sup>5</sup>Xiamen University Malaysia, Electrical and Electronics Engineering, Selangor, Malaysia.

<sup>&</sup>lt;sup>6</sup>Qatar University, Department of Electrical Engineering, Qatar

<sup>\*</sup> Corresponding Author's e-mail: jfollure@yahoo.fr, arifsobhan.bhuiyan@xmu.edu.my, mchowdhury@qu.edu.qa

#### 1 Introduction

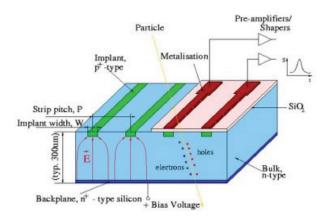

The Modern Front-End Electronics (FEE) for High Energy Physics Experiment (HEPE) are mixed-signal circuits in which the ultimate performance is set by the analog circuit applied to Solid State Detectors. The X-Rays-Sensors interaction produces a very small current and has to be amplified in a low noise circuit before any further signal processing either on-chip or off-chip with digital techniques. In multi-detector systems, multiple channels create several complications. In order to limit the power dissipation-noise problem, the sensor should be placed adjacent to the front-end amplifier. However, this results in decreased detector resolution because of heat transfer. Moreover, the process technology utilized for designing a preamplifier determines the overall size and price of the silicon-based detector systems. When a soft X-rays strikes a semiconductor detector, charges are generated. Various types of X-ray detectors including Silicon PIN Detectors, Silicon Drift Detectors (SDDs), Silicon Strip Detector (SSD), etc. have been extensively used in order to quantify the energy and photon count of incident X-rays. This type of detectors designed with a thick Si substrate is very useful for 2-D tracking in a high multiplicity environment because of the large charge collection area along with low anode capacitance [1]. Through going X-rays, create electron-hole pairs in the depletion zone of the detector and these charges drift towards the electrodes as illustrated in Fig.1. This drift (current) creates the signal (voltage) which is very weak and must be amplified by a CSA connected to each strip.

**Figure 1:** Principle of operation of a silicon strip detector [2].

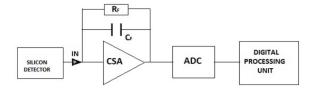

From the signals on the individual CSA, the amplitude of the output voltage is realized. That voltage depends on the energy of the incident particles and must be measured with the highest accuracy and precision [3]. The input node voltage of the CSA increases and the voltage with the opposite polarity is generated at the output terminal simultaneously. Hence, the output po-

**Figure 2:** Silicon detector readout architecture for digital processing, the CSA is used for extracting the charge at each strip and convert it into voltage.

tential through feedback loop forces the input potential of the CSA to become zero because of high open-loop gain as evident from Fig.2. The total amount of the current pulses is integrated on the feedback capacitor and the corresponding output is a step voltage pulse [3, 4] as described in equation (1).

$$V_{CSA}(t) = \frac{1}{C_f} \int_0^T i_e(t) dt + V_0$$

(1)

Where, VCSA(t) is the output voltage of the CSA at the time t,  $i_e(t)$  is the input current injected in the detector, T is the integration period,  $C_f$  the feedback capacitor and  $V_o$  is the offset voltage of the circuit.

As the input signals intercepted by CSA are generally very low. For a given signal source, the CSA noise performance depends on the noise created within the amplifier itself and the signal impedance seen by the amplifier input. Therefore, the CSA input stage must ensure that optimum noise matching is obtained for the given source impedance. The choice of the design parameters of the input stage of CSA influences the noise matching. So the total equivalent input noise should be kept as small as possible for a given detector capacitance up to 2pF. The main problem in the design of nuclear spectroscopy Very Large Scale Integration (VLSI) readout front ends is the implementation of lownoise; low power Charge Sensitive Amplifier (CSA). The selection of the process (CMOS or BiCMOS) determines the performance and generally the noise-related design methodology. A VLSI preamplifier costs much less than a hybrid one or a preamplifier unit [5]. CMOS exhibits several advantages over other concurrent technologies and and is preferred in VLSI circuit design [6-7]. A very popular approach in designing the VLSI CSA is the usage of an operational amplifier (Op-amp), with the R-C feedback network. Since Cdet (the detector parasitic capacitance) is quite large, about 15pF, the stability becomes a critical issue in that design [8]. For a complete validation of the CSA with CMOS technology, the overall system specifications are needed [8, 9]. In [10] H. Wang et al, proposed a CSA based Polyvinylidene Fluoride (PVDF) transducers. The circuit

works for low power dissipation and low frequency; but it iss prone to low conversion gain, high feedback capacitance that occupies more die area. A. Baschirotto et al [11], designed a CSA using a single-ended amplifier. The circuit works at high frequency and very low voltage; however, the disadvantages of that circuit are high power consumption and high Equivalent Noise Charge (ENC); furthermore, the circuit was prone to the parallel noise generated by the feedback resistor. The single-ended amplifier is a good architecture despite it is prone to both process variations and signal degradation. Indeed, the current mirrors, which generate the bias voltage for proper operation of the amplifier, contribute the common-mode noise. Thus, increasing the size of the input transistor of such an amplifier does not improve noise performance because of the bias current limitation [4]. Therefore, it is necessary to propose an optimal circuit to avoid unnecessary power dissipation and heat in closely packed pixel arrays. Secondly, the ENC should be optimized with respect to detector capacitance and the input transistor width, by performing AC and transient analysis.

In this article, a low-noise CSA designed in 0.35 µm CMOS technology process is proposed. The circuit consists of a single-ended gain block and a feedback network. The CSA bandwidth is compromised by a large detector capacitance. In order to compensate this, a common-source (CS) input design is adopted to isolate the capacitance, preventing it from affecting the bandwidth. Furthermore, CS topology is linear and power-efficient [12]. The feedback resistor stabilizes the gain-bandwidth product of the circuit. The resistor is an NMOS transistor operating as a voltage-controlled resistor; it also reduces the parallel noise contribution. The proposed circuit works with a low-energy capacitive silicon detector for X-ray detection applications.

#### 2 Materials and methods

The CSA has been designed for a 0.35  $\mu$ m TSMC process, to perform the initial conversion of current pulses into voltage pulses. Table 1 below presents the design specifications of a CSA circuit for Silicon-PIN detector applications.

**Table 1:** CSA specifications required for silicon detector for two vendors.

| Vendor<br>Parameters | Hamamatsu<br>(H4083) | Amptek<br>(A250) |

|----------------------|----------------------|------------------|

| Power consumption    | 150 mW@12V           | 14 mW@6 V        |

| Count rate           | 2.6 MHz              | 2.5MHz           |

| Detector capacitance | 0 — 25 pF      | 0 — 250 pF      |

|----------------------|----------------|-----------------|

| ENC<br>(Cin = 5pF)   | 240 e-         | 76 e-           |

| Noise slope          | 4 e-/pF        | 11.5 e-/pF      |

| Sensitivity          | 22 mV/MeV (Si) | 176 mV/MeV (Si) |

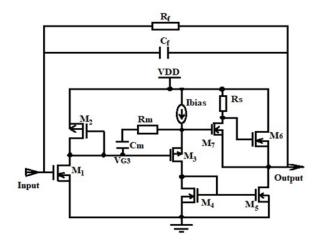

In order to increase the gain of the CSA, we choose a three-stage configuration for the design. The single-ended configuration of the circuit in Fig. 3, is preferred to the differential one for the reduction of power consumption. The choice of the N-channel input transistor relies on the lower thermal noise compared to the P-type at high frequency, since the 1/f noise is negligible in the frequency region after 10 kHz [13, 14]; in addition, N-channel MOS, gives a lower series white noise with respect to the P-channel counterpart, because of its higher transconductance [13]. The current source at M1's drain is provided by M2, a P-channel MOSFET with smaller transconductance.

The second stage is the Miller stage. In this stage, the transistors M3 and M4 are connected in cascade whereas the transistor M5 forms the current mirror. Such a stage in the CSA incorporates a higher output resistance. The maximum signal swing must be kept limited so that all the transistors remain in the saturation region of operation, i.e., VGS> VT and VDS> VGS-VT [13]. Therefore, the bias current of M3 is kept at a specific low value (12.5 uA) in order to keep its output impedance high. Capacitor Cm provides a gain and the dominant pole in that stage; so, resistor Rm suppresses direct transmission through Cm at high frequencies.

**Figure 3:** Schematic of the proposed structure of the CSA.

The third stage consists of an N-channel MOSFET M7 which results in a negative gain of the entire circuit so that one can apply the negative feedback. It is biased by a low current through RS. The value of Rs is set to

300  $\Omega$  so that M7 operates in the saturation region. Feedback from Vout is connected to one of the two inputs through an on-chip feedback capacitor up to 20 pF and a resistor of 30 M $\Omega$  at the top-level design. The circuit was designed with thick oxide transistors that allow a relatively high supply voltage of 3.3 V in a standard 0.35  $\mu$ m CMOS technology process.

#### 2.1 Analysis of the CSA circuit

The first stage is a cascade topology based on a common source amplifier so that the input is free from parasitic capacitance and the feedback amplifier controls the gate voltage. Therefore, the CSA input becomes a virtual ground and the detector capacitance is less significant to the CSA bandwidth.

The drains of M1 and M2 are common. When M1 is in the saturation region, we have the equation bellow:

$$V_{G3} = |V_{THP2}| + |(V_{in} - V_{THN1})| \sqrt{\frac{\mu_n}{\mu_p} \left(\frac{W_1}{L_1}\right) \left(\frac{L_2}{W_2}\right)}$$

(2)

When M1 enters in the triode region, the following equation (2) holds

$$\mu_{n} \left( \frac{W_{1}}{L_{1}} \right) \left[ 2 \left( V_{in} - V_{THN1} \right) V_{G3} - V_{G3}^{2} \right] = \mu_{p} \left( \frac{W_{2}}{L_{2}} \right) \left( V_{G3} - V_{THP2} \right)^{2}$$

(3)

with this topology, the dopants are not concentrated near the surface, so their effect is less than expected. Therefore, the voltage at the gates of M2 and M3 should depend on Rm and the reference current of M2.

In the second stage of CSA circuit, transistor M3 is in the saturation region and its drain-source current is defined by the formula:

$$I_{x} = \frac{1}{2} C_{ox} \mu_{p} \left( \frac{W_{3}}{L_{3}} \right) (V_{G3} - V_{THP3})^{2}$$

(4)

Transistor M3 remains in the saturation region until the device enters the triode region where

$$V_{G3} = V_{THP3} + \sqrt{\frac{2I_{bias} + 2V_{THP3} / R_m}{C_{ox}\mu_p \left(\frac{W_3}{L_3}\right)}}$$

(5)

As the whole circuit is designed to work in the saturation region, equations (2) and (5) involve:

$$I_{bias} = C_{ax} \mu_p \left( \frac{W_3}{L_3} \right) \left[ V_{THP2} - V_{THP3} + \left| \left( V_{in} - V_{THN1} \right) \right| \sqrt{\frac{\mu_n}{\mu_p} \left( \frac{L_2}{W_2} \right)} \right]^2 - \frac{V_{THP3}}{R_m}$$

(6)

The biasing current helps to deplete a larger portion of the substrate and the p-well. That current depends on both the geometric and threshold voltage of transistors M1, M2 and M3. Those parameters are influenced by the mismatch of the circuit. At threshold voltage of the transistor, the instantaneous current flowing from source to drain gets a sudden boost and the additional gate voltage rise causes an exponential increase of the current. The threshold voltage of a transistor is not constant and depends on physical, electrical, and environmental factors. It has two parts:  $\Delta V_{\text{THO}}$  that is supposed to be persistent for a given technology, device, etc. [15] and  $\Delta V_{\text{TH}}$  that depends on operational parameters. The  $V_{\text{TH}}$  can be expressed in the equation (6) as

$$V_{TH} = V_{TH0} + \Delta V_{TH} \tag{7}$$

Assuming  $V_{THO}$  constant for each transistor and  $\Delta V_{TH}$  identical for each type of transistor, the final expression of Ibias can be expressed as follows:

$$I_{bias} = C_{ox} \mu_n \left( \frac{W_1 \times W_3}{L_3 \times W_2} \right) \left( V_{GS1} - V_{THN0} - \Delta V_{THN0} \right)^2 - \frac{V_{THP0}}{R_m} - \frac{\Delta V_{THP}}{R_m}$$

(8)

Fluctuations in  $\Delta VTH$  occur mainly because of temperature and voltage variations which initiate effects such as Drain Induced Barrier Lowering (DIBL), short channel effects, narrow width effect, back bias dependent threshold shift, hot carrier effect, etc. So, the biasing current as a function of the threshold voltage was computed for the limited amount of current for the circuit [15] [16].

#### 2.1 Noise optimization of the CSA circuit

One of the primary objectives of a typical CSA design is the minimization of the ENC and this necessitates a precise input stage design. In general, the noise associated with the drain current of the input device is the vital part of the ultra-low-noise design, [17]. Past research on ENC noise minimization in the CSA focused on the geometric characteristics (W and L) or the transconductance (gm) of the input transistor. However, the leakage current is a crucial parameter of the detector which seriously affects the resolution and reliability of the detector. It is related to many factors, such as the quality of silicon, process flow, temperature, etc. which is difficult to accurately express by analytical formula. Gate-controlled diodes have been frequently used to characterize leakage current components and extract minority carrier lifetime [16] [24]. Some detailed leakage current analyses with gate-controlled diodes have been performed in regular thickness wafer for a radiation detector [16]. This research, presents the ENC as a function of the detector capacitor and the feedback for a fixed value of W and L, according to the adopted

CMOS process. The leakage current is 10nA. The different contributions are evaluated as follows:

The most prominent thermal noise contribution can be calculated as:

$$ENC_{th}^{2} = 4K_{B}Tn\gamma\alpha_{n} \frac{\left(C_{det} + C_{f} + C_{g}\right)^{2}}{g_{m}C_{g}} \frac{N_{th}}{\tau_{p}}$$

(9)

In which KB is the Boltzmann constant, T is the room temperature,  $\eta$  is the body factor,  $\gamma$  is the inversion factor, an the excess noise factor, Nth is the shaper noise index for the thermal noise,  $\tau p$  is the peaking time, Cdet the detector capacitance, Cf the feedback capacitance, Cg the gate capacitance and gm the input MOSFET transconductance.

The flicker noise or the noise due to 1/f is expressed as:

$$ENC_f^2 = K_f \frac{\left(C_{\text{det}} + C_f + C_g\right)^2}{C_e} N_f$$

(10)

Where Kf is the flicker noise coefficient and Nf the shaper noise index for flicker noise. Considering the

fact that,

$$g_m = \sqrt{2\mu \frac{C_g I_D}{L^2}}$$

with Cg = Cox WL [12],

equations (9) and (10) are respectively written as:

$$ENC_{th}^{2} = 4K_{B}Tn\gamma\alpha_{n} \frac{\left(C_{det} + C_{f} + C_{ox}WL\right)^{2}L}{\sqrt{2\mu I_{D}}\left(C_{ox}WL\right)^{\frac{3}{2}}} \frac{N_{th}}{\tau_{p}}$$

(11)

$$ENC_f^2 = K_f \frac{\left(C_{\text{det}} + C_f + C_{ox}WL\right)^2}{C_{ox}WL} N_f$$

(12)

The white parallel noise contribution to the MOSFET gate current due to the detector leakage current, can be written as:

$$ENC_i^2 = 2qI_{leak}N_i\tau_p \tag{13}$$

Where, Ileak is the leakage current associated with shot noise, and Ni is the shaper noise index for the shot noise. This term doesn't depends on W and ID.

Different components of the ENC were optimized with respect W and ID first, and the with respect to Cg. A first-order (n = 1) shaper has been used. Therefore the thermal noise is optimal if

$$\frac{\partial ENC_{th}^2}{\partial W} = 0 \tag{14}$$

Equation (14) is satisfied. The solution of that equation (14) is Wth = ((Cdet + Cf)/3CoxL), where, Wth = 42  $\mu$ m for Cdet=Cf = 0.2 pF. Similarly, the flicker noise is optimal when equation (15) is satisfied.

$$\frac{\partial ENC_f^2}{\partial W} = 0 \tag{15}$$

The solution of that equation (15) is: Wf= 3 Wth with (Wf=126  $\mu$ m).

The ENC as a function of ID and W is computed for both the thermal and the flicker noise. In this study, the lowest width (Wth= 42 µm) has been considered for achieving a minimal thermal noise contribution. The flicker (1/f) noise of the drain current of the preamplifier is associated with the input transistor. This is because of the generation and recombination of carriers in the two depleted regions from impurity atoms and lattice defects [16]. The instability of the drain current (ID) is established by the variation of charge in the depletion region, which constitutes the channel width. Therefore, an optimal width involves an optimal drain current of 70µA. If the trapping and releasing of carriers were purely random, the noise spectrum would be uniform. The ENC of the whole CSA circuit is calculated by adding the contributions of thermal noise, flicker noise and the shot noise [14, 17, 18]. In order to make noise as small as possible, Kf is needs to be as small as possible. Its value depends on the adopted technology process as well. Therefore, the total ENC can be expressed as:

$$ENC_{total}^2 = ENC_{th}^2 + ENC_f^2 + ENC_i^2$$

(16)

$$ENC_{total}^2 = 4K_f N_f (C_f + C_{det}) +$$

$$+\frac{64}{3}K_{B}Tn\gamma\alpha_{n}\frac{N_{th}}{\tau_{p}}\frac{\sqrt{C_{\text{det}}+C_{f}}}{\sqrt{6\mu_{n}I_{D}}}+2qI_{leak}N_{i}\tau_{p}$$

(17)

Where,  $ENC_{th'}$   $ENC_f$  and  $ENC_i$  are the thermal flicker and shot noise components respectively. Mostly,  $ENC_{th}$  is the dominant part of overall ENC noise. Equation (14) is computed and the ENC could be represented by the following expression.

$$ENC = 42.5e^{-} + 3.72e^{-} / pF$$

(18)

Input transistor capacitance, Cin, contributes to the total capacitance of the input of the preamplifier, Ctot, which affects the series white noise and the 1/f noise contribution to the total noise. If the width of the gatechannel is reduced, Cin as well as the transconductance (gm) decrease, which results in higher series white noise spectral density. In order for the transconduct-

ance to be as large as possible, a relatively large width transistor is preferred [15, 18]. Moreover, if the detector capacitance dominates over the transistor capacitance, a large Cin value results in a small noise increment. However, such a Cin can be balanced by matching it to the detector capacitance. Table 2 and Table 3 illustrate the constant parameters used for this design and the transistor sizing for the proposed CSA design.

Table 2: Main constant parameters.

| Symbol     | Quantity                             | Values                                               |

|------------|--------------------------------------|------------------------------------------------------|

| n          | body factor                          | 1.5                                                  |

| $\alpha_n$ | excess noise factor                  | 0.93                                                 |

| γ          | inversion factor                     | 0.53                                                 |

| $N_f$      | shaper noise index for flicker noise | 3.69                                                 |

| $N_{th}$   | shaper noise index the thermal noise | 0.92                                                 |

| $K_f$      | flicker noise coefficient            | 8.5.10 <sup>-25</sup> C <sup>2</sup> m <sup>-2</sup> |

| $g_m$      | input transistor transconductance    | 614 μS                                               |

Table 3: Transistor parameters (W/L).

| Transistors | W/L (µm)  |

|-------------|-----------|

| M1          | 42/0.35   |

| M2          | 0.84/0.35 |

| M3          | 18/0.35   |

| M4          | 18/0.35   |

| M5          | 12/0.35   |

| M6          | 12/0.35   |

| M7          | 9/0.35    |

#### 3 Results and discussions

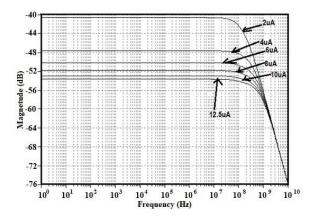

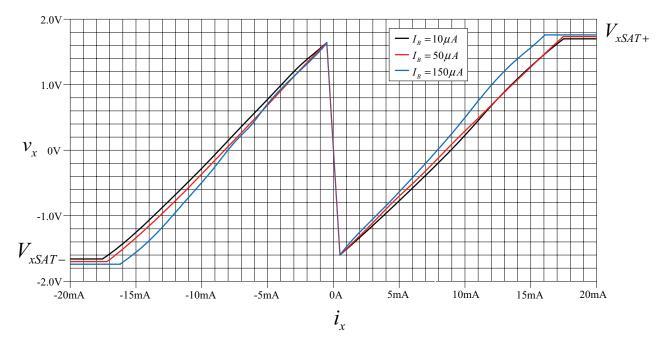

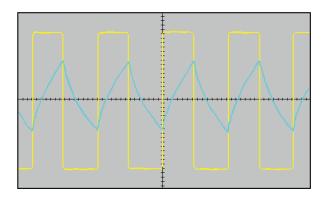

The proposed CSA circuit performance was verified using LTspice simulator and the layout was implemented in 0.35 µm CMOS technology process from TSMC, using Electric VLSI, which is an open source tool for integrated circuit design. Fig. 4 shows the gain of the proposed CSA. It is controlled by the Ibias value for a feedback loop of Rf = 150 k $\Omega$  and Cf = 2 pF. Frequency domain analysis was performed from 1Hz to 10 GHz. The bias current is adjusted by changing the value of the external resistor allowing changing the transconductance as represented in equation (7). The gain (absolute value) varied from 40.6 dB to 53.8 dB. The highest bandwidth of the amplifier is achieved for 12.5µA bias current, and is equal to 1.023 GHz. The optimization of the bias current of the second stage is very important for stabilizing the gain-bandwidth product and maintaining signal integrity [19]. The capacitor of the detector was set to 1 pF and the parasitic capacitance of the input transistor is around 20 fF. So, total input capacitance was 1.02 pF.

Figure 4: Influence of Ibias on the gain.

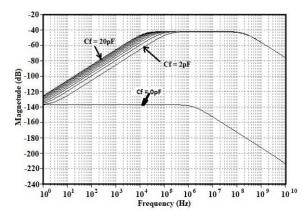

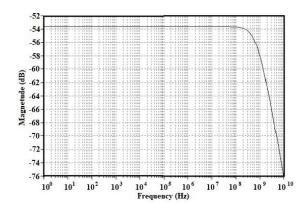

One of the most critical points in CSA is the loop gain stability, which is determined by its feedback capacitance. Nevertheless, a resistor has a parasitic capacitance and a capacitance has a parasitic resistance. Thus, an RC feedback network (Rf-Cf) models the feedback circuit. Loop-gain stability has been evaluated during the charge vs voltage conversion when Rf-Cf is bypassed [9]. The Opamp equivalent load capacitors are also taken into consideration by varying Cf. For achieving the highest stability of the circuit, the gain is adjusted by the Rf-Cf sizing. Rf was implemented by associating the drain-source resistance of a N-channel MOSFET device biased to be in the triode strong inversion region. Under this condition, the parallel noise was eliminated; the circuit is therefore stable and continuously sensitive and can be maintained in this condition without adjustment for spectroscopy purpose [10, 22, 23 and 24]. Thus, with that technique, we achieved a feedback resistance of 30 M $\Omega$  with a W/L = 25. The magnitude of the gain is therefore represented for each parameter of the feedback network. Thus, for Rf = 150 k $\Omega$ , Cf is varied from 2 pF to 20 pF. Fig.5 shows the variations of the gain for different values of Cf. For frequencies lower than 100 kHz, the parasitic capacitance of the input transistor and the resistive feedback affect the gain of the CSA and its bandwidth. The closed loop bandwidth achieved in this topology is 459.6 MHz. The circuit is immune to those parasitic effects for frequencies greater than 100 kHz. The same analysis could be applied to Fig. 6, where a MOSFET controller resistor, sized to be 150 k $\Omega$ , substituted the resistive feedback. The gain is immune to the resistive feedback and the parasitic capacitance. These results confirm the stability of the circuit with a feedback MOSFET resistor. A bandwidth of 1.023 GHz can be achieved without compromising the stability of the circuit (with output magnitude of -56.8 dB). By adjusting Ibias as shown in

Fig. 4, the bandwidth could be increased to more than 1.9 GHz.

Figure 5: Influence of Cf on the gain with Rf feedback.

**Figure 6:** Influence of Cf on the gain using a MOSFET equivalent of Rf.

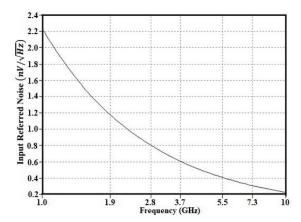

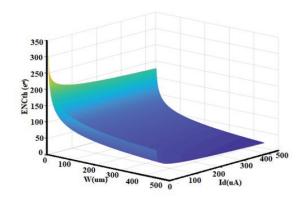

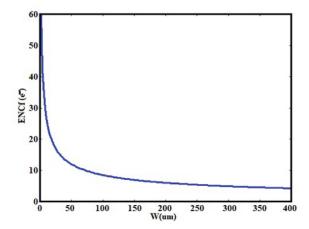

In Fig. 7 the Input-referred-noise (IRN) is plotted in the frequency range of 1 GHz to 10 GHz. The IRN (noise density) value extracted is 2.38 nV/√Hz. Furthermore, while designing a recording analog front-end (AFE), a lower IRN ensures the better signal quality and low power consumption will extend the lifetime of the device [19]. However, in the CSA, the parameter that embodies the noise performance is the ENC (Equivalent-Noise-Charge), namely the input charge necessary to get at the output a signal equal to noise. Its calculus was based on this intrinsic definition, neglecting the standard calculus depending on the post-CSA circuit, not present in this design [10]. Therefore, the ENC was computed and extracted based on equation (14); it presents a constant value of 42.5 e- for a detector capacitance of OpF and noise performance increases with a slope of 3.72 e-/pF. For exhibiting the dominant component of the input noise, the ENC as a function of ID and W for the thermal component is computed in Fig. 8, and compared to the flicker noise component, which depends on W as shown in Fig. 8 and Fig. 9. In Fig. 8, when increasing the current in the input transistor, its thermal noise decreases but the bandwidth over which the thermal noise is integrated increases by the same amount; both effects cancel each other out. It can be depicted in Fig.8 and Fig .9 that the most dominant component of the ENC noise is the thermal noise component. Thus, if the device operates in a low count rate environment, substantial reductions in power consumption can be obtained with little or no noise penalty by reducing the bias current of the input transistor provided a good separation between the preamplifier rise and fall time is ensured [25].

Figure 7: CSA Input-Referred Noise.

Figure 8: ENCth as a function of W and Id.

Figure 9: ENCf as a function of W.

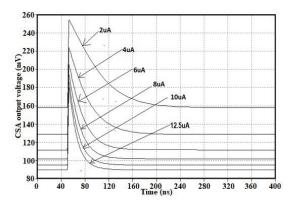

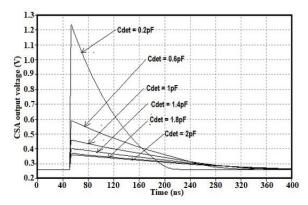

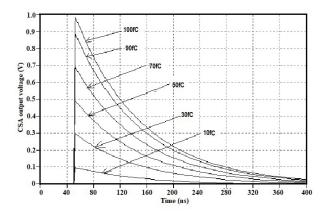

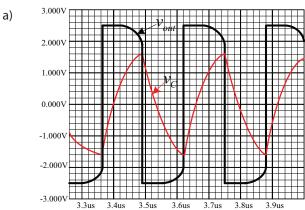

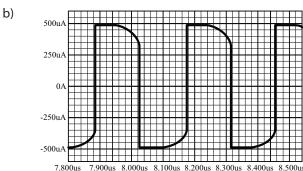

The transient response of CSA is shown in Fig.10 and Fig.11. A current pulse with an amplitude of 33 µA and width of 1ns (206250 electrons) is injected into the detector. The output of CSA achieves a peak of 330mV and decreases thereafter because of the feedback action. For a detector capacitor of 0.2 pF, the bias current of M3 is varied and the results are shown in Fig.10. It is evident that Ibias helps to keep a lower offset and better resolution of the circuit. The same analysis is made by fixing the bias current at 12.5 µA and varying the detector capacitor from 0.2 pF to 2 pF on Fig.11. The highest amplitude (1.23 V) is obtained with 0.2 pF detector capacitance; while the highest capacitor (2 pF) generates saturation of the CSA. The output voltage is distorted and the energy information is lost which results in a circuit with low resolution. [5][26]. The fall time of the signal is about 300ns (determined by Cf and Rf).

Figure 10: Ibias effect on CSA output voltage.

The amplitude of the signal charge obtained with a semiconductor detector is determined by the input particle energy such as soft X-rays and gamma rays and by the material of the semiconductor [14]. For Si-PIN diodes, the capacitance scales with area, so large area detectors exhibit more noise [21]. For SDDs, the capacitance is much lower and nearly independent of area. This noise is weakly dependent on temperature and leakage current. Since leakage current increases exponentially with temperature, reducing temperature helps dramatically [1].

Figure 11: Cdet effect on CSA output voltage.

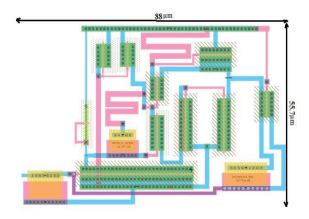

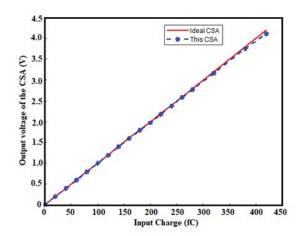

The total core layout area occupied by the proposed CSA is (88x55.7) µm2 as shown in Fig. 12. Parasitic extraction was used to extract the netlist with parasitic. The voltage supply is 3.3 V; the total power consumption is about 0.23 mW for the whole circuit. In this research, the gain-bandwidth product of the circuit was stabilized by means of a high-frequency feedback loop, which operates according to the voltage controlled NMOS resistor (Rf) technique [10] with resistance between 30 k $\Omega$  and 30 M $\Omega$  and a capacitance of 2 pF. The response of the circuit to different input charges results in good amplification. The gain linearity of the specific preamplifier implementation was extracted and the circuit energy response is shown on Fig. 13. The nonlinearity of the CSA's gain shown on Fig. 14 (within 4.6% up to Qin=420 fC, and within 0.8% up to 300 fC) is mostly due to the second order effect of the dependence of Rf (MOSFET) on the input charge. The single MOSFET feedback network provides minimum thermal noise and high linearity, but requires baseline stabilization, and can be realized in multiple stages. [22]. The absolute value of the conversion gain is 9.92mV/fC.

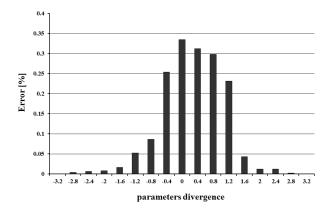

Fig. 15 shows the Monte-Carlo results of the proposed circuit for 500 runs. The output signal and the histogram of the conversion gain of the circuit are shown for 10 fC injected at the input of the detector. The output signal varies from 100mV to 50 mV due to the variations of the different parameters of the circuits with the tolerance of 10%. In fact, the process variation of Ibias increases the dc-gain of the core amplifier as explained in the previous sections. The highest sensitivity of the design is then presented on Fig. 15a, for a weak amount of injected charge (10fC); the circuit achieved an amplitude of 100mV. However, the histogram of conversion gain observed on Fig.15b shows a mean value of 9.79 mV/fC, and a standard deviation of 1.64 mV/fC. This indicates that the results obtained with Monte-Carlo models do not differ significantly for 500 runs and the CSA performance is quite stable and reliable.

Figure 12: The core layout of the CSA circuit.

Figure 13: CSA output voltage for different input charge

**Figure 14:** Output voltage vs input charge of the CSA circuit

As a summary, in Table 4 the overall features of the CSA circuit are shown. The effort in reducing power consumption, ENC and active die area of the chip comes in the parallel with similar application design present in literature [5, 8, 10, 11, 14, 21, 26]. Considering the significant difference in the input capacitance, the results are encouraging. Therefore, the preamplifier performance is in agreement with the initial specifications

**Table 4:** CSA performance summery and comparison.

**Figure 15:** Post-layout Monte-Carlo simulation results (a) Output voltage (b) Conversion gain.

required. On the one hand, the design of the input and feedback transistors allowed us to achieve high linearity, wide bandwidth and sufficient low noise to ensure the good resolution of the below-threshold part of the spectrum in [26]. On the other hand, the optimization of Ibias helps to control the dc gain of the circuit and avoid saturation of the device. Operational Amplifier stability has been guaranteed with a 53.8 dB minimum dc-gain.

#### 4 Conclusions

In this research, a 0.35  $\mu$ m low-noise stable CSA circuit has been designed for Silicon detector applications.

| Parameter                   | This Work          | [5]               | [8]       | [17]                | [21]     | [10]               |

|-----------------------------|--------------------|-------------------|-----------|---------------------|----------|--------------------|

| CMOS Technology             | 0.35 μm            | 0.35 μm           | 0.13 μm   | 0.13 μm             | 0.35 μm  | 0.18 μm            |

| Power Supply                | 3.3 V              | 1.65 V            | 1.8 V     | 1.2 V               | 3.3 V    | 1.8 V              |

| Power Consumption           | 0.23 mW            | 0.165 mW          | 1.1 mW    | 4.8 mW              |          | 2.1 μW             |

| Input Parasitic Capacitance | 0.2 pF – 2 pF      | 2 pF              | 15 pF     | 5 pF                | 10 pF    |                    |

| ENC                         | 42.5 e + 3.72 e/pF | 254 e- +13.5 e/pF | 418 e     | 600 e +<br>100 e/pF | 650 e    |                    |

| Amplifier Gain              | 9.92 mV/fC         | 2.81 mV/fC        | 0.5 mV/fC | 10 mV/fC            | 15 mV/fC | 0.8 μV/fC          |

| Active area (mm²)           | 0.0049             | 0.004212          |           | 0.7225              | 0.75     | 0.038              |

| Input Dynamic Range         | 0- 480 fC          | 0 – 120 fC        |           | 0 – 60 fC           | 80 fC    | 150 pC –<br>450 pC |

As per CSA, design requirements, the detector capacitance and the input stage transistor aspect ratio have been optimized in order to achieve the possible low noise and high gain performance. Moreover, adopting NMOS feedback voltage-controlled resistor technique, parallel noise that could be generated by the feedback resistance is removed which in turn ensures high stability of the design. This CSA operates at the amplification of 53.8 dB and works up to 1.023 GHz. It achieved a Charge-Voltage Conversion Factor of 9.92 mV/fC, which is compatible with the state-of-the-art. With a supply voltage of 3.3 V, it dissipates very low power of 0.23 mW. Furthermore, the proposed CSA active die area is only 0.0049 mm2. The satisfactory linearity of this circuit could be used to improve the energy resolution of X-ray radiation detection systems. The achieved results make the proposed CSA a compatible candidate for multi-channel front-end readout ASIC for Silicon detectors applications.

#### 5 Acknowledgments

The support from the ICTP/IAEA Sandwich Training Educational Programme for this research is gratefully acknowledged. Besides, this research was partially funded by the UKM research university grant DIP-2018-017 and by the Qatar National Research Foundation (QNRF) grant UREP 23-027-2-012.

#### 6 Conflict of Interest

The authors declare no conflict of interest. Besides, the founding sponsors had no role in the design of the study; in the collection, analyses, or interpretation of data; in the writing of the manuscript, and in the decision to publish the results.

#### 7 References

- [1] A. Walenta, et al., Vertex Detection in a Stack of Si-drift Detectors for High Resolution Gamma-ray Imaging. "Proceedings of the IEEE NSS-MIC 2003, M3-40, USA, 2003, pp. 1815-18, https://doi.org/10.1109/NSSMIC.2003.1352231.

- [2] D. Bortoletto, How and why silicon sensors are becoming more and more intelligent? 'Journal of Instrumentation, 2015, 10, art. no.C08016. https://doi.org/10.1088/1748-0221/10/08/C08016

- [3] E. J. Schioppa, et al, "Study of Charge Diffusion in a Silicon Detector Using an Energy Sensitive Pixel

- Readout Chip," IEEE Tran.Nucl. Sci., vol. 62, no. 5, pp. 2349 –2359, 2015,

- https://doi.org/10.1109/TNS.2015.2475124.

- [4] I. Peric, "A novel monolithic pixel detector implemented in high-voltage CMOS technology, "in IEEE Nuclear Science Symposium Conference Record, USA, Oct, 2007, pp. 1033–1039. https://doi.org/10.1109/NSSMIC.2007.4437188.

- [5] T. Noulis et al, "Noise optimized charge-sensitive CMOS amplifier for capacitive radiation detectors," IET Circ. Dev. Syst . vol. 2, pp. 324 - 334, 2008 <a href="https://doi.org/10.1049/iet-cds:20070223">https://doi.org/10.1049/iet-cds:20070223</a>

- [6] T.I. Badal, M.B.I. Reaz, M.A.S.Bhuiyan, and N. Kamal, "CMOS Transmitters for 2.4-GHz RF Devices: Design Architectures of the 2.4-GHz CMOS Transmitter for RF Devices," IEEE Microwave Magazine, vol.20, no. 1, pp. 38-61, 2019, https://doi.org/10.1109/MMM.2018.2875607

- [7] M.A.S. Bhuiyan, M.T.I. Badal,M.B.I. Reaz, M.L.Crespo, and A. Cicuttin, "Design Architectures of the CMOS Power Amplifier for 2.4 GHz ISM Band Applications: An Overview.," Electronics,vol 8, no. 5, pp. 477, 2019, https://doi.org/10.3390/electronics8050477

- [8] A. Costantini, et al., "A Low-Power CMOS 0.13 μm Charge-Sensitive Preamplifier for GEM Detectors," Proceedings of the 2013 International Conference on IC Design & Technology 2013, Italy, 2013, pp.147-150,

- https://doi.org/10.1109/ICICDT.2013.6563324

- [9] V. Valente et al, "Design of a wideband CMOS Impedance Spectroscopy ASIC Analog Front-End for Multichannel Biosensor Interfaces", Proceedings of the 37th Annual International Conference of the IEEE Engineering in Medicine and Biology Society. Milan, Italy, pp. 885-888, 2015, https://doi.org/10.1109/EMBC.2015.7318504

- [10] H. Wang et al, "A Charge Sensitive Pre-Amplifier for Smart point-of Care Devices Employing Polymer Based Lab-on-a-Chip", IEEE Trans. Cir, Syst II, 2018, vol. 65, pp.984 988, https://doi.org/10.1109/TCSII.2018.2798929.

- [11] A. Baschirotto et al, A fast and low noise charge sensitive preamplifier in 90nm technology; Journal of Instrumentation, 2012, vol. 7, art. No. C01003, pp. 1-8,

- https://doi.org/10.1088/1748-0221/7/01/C01003

- [12] N. Deferm, P. Reynaert, "CMOS Front Ends for Millimeter Wave Wireless Communication System", ACSP. Analog Circuits And Signal Processing;; 1st edition, Springer. ISBN 978-3-319-13951-7

- [13] V. Re et al, "Survey of Noise Performances and Scaling Effects in Deep Submicron CMOS Devices from Different Foundries", Proceedings of the IEEE

Symposium Conference Record Nuclear Science, Italy, pp. 1368-72, 2004,

#### https://doi.org/10.1109/NSSMIC.2004.1462496

- [14] A. Seljak et al., "A fast, low power and low noise charge sensitive amplifier ASIC for a UV imaging single photon detector", Journal of Instrumentation, vol. 7, Art. no. C01003, 2017,

- https://doi.org/10.1088/1748-0221/12/04/T04007.

- [15] G. Bertuccio and S. Caccia, "Progress in ultra-low-noise ASICs for radiation detectors," Nucl. Instrum. Methods Phys. Res. A, vol.579, no. 1, pp.243–246, 2007,

#### https://doi.org/10.1016/j.nima.2007.04.042

[16] N. Cong Dao et al, "An enhanced MOSFET threshold voltage model for 6-300K t emperature range", Journal of Microelectronics reliability, vol. 69, pp. 36-39,2017,

#### https://doi.org/10.1016/j.microrel.2016.12.007

- [17] H. Zhao, X. Liu, "Modeling of a standard 0.35µm CMOS technology operating from 77K to 300K", Cryogenics vol. 59, pp. 49–59, 2014, https://doi.org/10.1016/j.cryogenics.2013.10.003.

- [18] F. Faccio and G. Cervelli, "Radiation-induced edge effects in deep submicron CMOS transistors", IEEE Trans. Nucl. Sci, vol. 52, no. 6, pp. 2413–2420, 2005.

#### https://doi.org/10.1109/TNS.2005.860698

[19] T. Tang et al, "An Integrated Multichannel Neural Recording Analog Front-End ASIC with Area-Efficient Driven Right Leg Circuit", Proceedings of the IEEE Eng Med Biol Soc. Seogwipo, South Korea, 2017, 217-220,

#### https://doi.org/10.1109/EMBC.2017.8036801.

[20] Z. Zhou et al, "An Analog Integrated Front-Ent Amplifier For Neural Applications", Proceedings of the 2016 International Conference on Integrated Circuits and Microsystems, Chengdu, China, November, 2016, 135-139,

#### https://doi.org/10.1109/ICAM.2016.7813579

[21] F. Ciciriello et al, "A new Front-End ASIC for GEM detectors with time and charge measurement capabilities", Nucl. Instrum. Methods Phys. Res. A, vol. 824, pp. 265-267, 2016,

#### https://doi.org/10.1016/j.nima.2015.12.048

- [22] R. Baur et al, "Frond-Electronics for the CERES TPC-detector", Nucl. Instrum. Methods Phys. Res. A, vol.409, no. 1, pp. 278–285, 1998,

- https://doi.org/10.1016/S0168-9002(97)01280-1

- [23] P. O'Connor et al, "Ultra Low Noise CMOS preamplifier-shaper for X-ray spectroscopy", Nucl. Instrum. Methods Phys. Res. A, vol.409, no. 1, pp. 315–321, 1998,

#### https://doi.org/10.1016/S0168-9002(97)01289-8

[24] Bernd J. Pichler, et al, "Integrated low-Noise Low-Power Fast Charge Sensitive Preamfier for Avalanche Photodiodes in JFET-CMOS Technology "IEEE Trans. Nucl. Sci, vol. 48, no. 6, pp. 2370 – 2374, 2001.

#### https://doi.org/10.1109/23.983270

- [25] X. Llopart et al, "Study of low power front-ends for hybrid pixel detectors with sub-ns time tagging", vol. 14, article no. C01024, 2019,

- https://doi.org/10.1088/1748-0221/14/01/C01024

- [26] A. Pullia and S. Capra, "Experimental performance of a highly-innovative low-noise charge-sensitive preamplifier with integrated range-boosted", vol. 13, article no. C12004,2018,

- https://doi.org/10.1088/1748-0221/13/12/c12004

Copyright © 2020 by the Authors. This is an open access article distributed under the Creative Com-

mons Attribution (CC BY) License (https://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Arrived: 23. 09. 2019 Accepted: 20. 01. 2020

https://doi.org/10.33180/InfMIDEM2020.102

## Back Propagation Neural Network in Predicting the Thermal Fatigue Life of Microelectronic Chips

Xiaoguang Huang, Dianhao Zhang, Zhiqiang Wang

China University of Petroleum (East China), College of Pipeline and Civil Engineering, Qingdao, China

**Abstract:** The present study gives an efficient approach to predict the thermal fatigue lives of microelectronic chips under cyclic thermal load using back propagation (BP) artificial neural network method. Strain based and stress-strain based thermal fatigue life models are established, respectively, according to the experimental results of thermal fatigue tests and the singularity parameters at the failure interface calculated by finite element method (FEM). According to the existing FEM results, the BP approach is configured to predict the singularity parameters at the failure interface in the new chips once the dimensions and thermal-mechanical properties of solders are obtained. By comparison, the predicted thermal fatigue lives according to the established thermal fatigue life models are in good agreement with the experimental results. The thermal fatigue life prediction of microelectronic chips based on the BP network approach is feasible.

**Keywords:** thermal fatigue, microelectronic chips, BP, singularity parameters, life prediction

## Nevronske mreže z vzvratnim širjenjem pri napovedovanju temičnega utrujenosti mikroelektronskega čipa

**Izvleček:** Članek predstavlja učinkovit način napovedovanja življenjske dobe mikroelektronskega čipa zaradi termičnega staranja pri cikličnih termičnih obremenitvah z uporabo nevronskih mrež z vzvratnim širjenjem. Vzpostavljeni so modeli termične utrujenosti glede na rezultate poskusov in izračunov parametrov singularnosti po metodi FEM. Primerjava novih in obstoječih modelov je pokazala dobro ujemanje z rezultati meritev. Napovedovanje termične utrujenosti čipov na osnovi BP mrež je mogoče.

Ključne besede: termična utrujenost; mikorelektronski čip; BP; singularnost; napovedovanje življenjske dobe

#### 1. Introduction

The electronics industry is mainly driven by the demand for smaller size with lower power consumption while having increased functionality and lower cost. Because of high-density and cost-effective performance, microelectronic chip has been widely used as the core component of automatic control and power converters in various industrial field [1, 2]. Exposed to the switching on-off and random fluctuations of power in the actual operation, the microelectronic chipset is often subjected to cyclic temperature loads. At the same time, the multi-layer package structure inherent in power electronics has an interface layer of a plurality of different materials inside. When the interface layer is under the

action of cyclic temperature load, the irreversible plastic deformation accumulates from the interface, due to the mismatch of the coefficients of thermal expansion in different layers. When the cumulative plastic deformation reaches a critical level, the crack begins to nucleate and grow, and finally the device is permanently ineffective [3-6]. The solder layer plays an important role in the mechanical and electric connections, therefore, its performance, especially, thermo-mechanical properties, has become an important factor affecting the whole reliability of the microelectronic chips. Generally, the strength and failure properties joints are dominated by the properties of both the solder material itself and the interface bonding [7, 8]. To obtain the

<sup>\*</sup>Corresponding Author's e-mail: huangupc@126.com

excellent interface bonding, usually the solder material needs to satisfy the following requirements: 1) proper melt temperature; 2) excellent wettability or adhesive properties; 3) enough strength for bonding. Besides, adaptation to surroundings becomes much more important from the social requirements [9, 10]. However, such requirements for the solder materials cannot give a quantitative evaluation of strength and thermal fatique life for older joints. To give a proper estimation of strength and thermal fatigue life, numerical analysis and failure criterion (including thermal fatigue law) are necessary to obtain the parameters describing the stress or strain state and the evaluation criteria [11-13]. Since Hattori et al. [14] suggested a singularity parameter approach for the interface reliability of plastic IC packages using two stress intensity parameters that characterize the stress distribution near a bonded edge along the interface, similar methods had been widely adopted to predict the crack initiation or delamination of the microelectronic chip [15, 16]. However, such a method, strictly, is based on the concept of point failure, which may difficultly be observed by the physical experiment, and is valid only for the cases that the geometric shape of the solder joints and the loading conditions are the same with that used to build up the fatigue law [17, 18]. Meanwhile, the stress intensity factor at the edge of the interface is always dependent on the test condition, assembly geometry, mechanical property of materials and their interactions, as well as the impact of process parameters [19, 20], which leads to the result that the precise models and a large amount of calculation are necessary to obtain the stress intensity factors at the failure interfaces of different chips. Soft-computing is doubtless a good alternative for handling this complex problem as it is tolerant of imprecision and uncertainty. Up to date, various soft-computing methods, e.g. artificial neural network [21-23], and genetic programming (GP) [24, 25] have been used in the field of thermal fatigue.

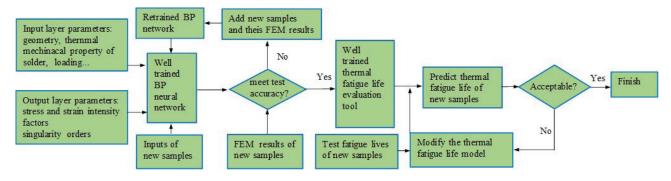

In the present work, the thermal fatigue life models of microelectronic chips based on interfacial singular stress-strain fields are established. Thermal fatigue tests are carried out to obtain the thermal fatigue lives of the chips, and the three dimensional finite element thermal mechanical analysis is also conducted to get the singularity parameters at the failure interface. Therefore, the parameters in the established model are determined. Also, to save the workload of calculating singularity parameters of new chips, an attempt has been made to predict these parameters by applying the BP neural network approach and accordingly, the thermal fatigue lives of these chips can be calculated.

#### 2. Thermal fatigue prediction model

#### 2.1 Thermal fatigue test

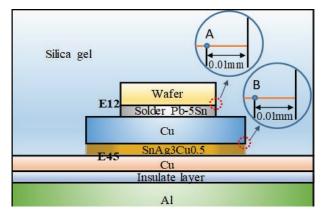

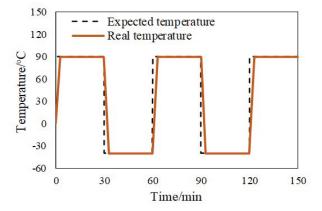

Five types of chips, denoting as I-V chips, are packaged in one chipset. The working powers of I-V chips are 35.7, 33.3, 25.8, 20.0 and 14.5 w, respectively. Each chip has the same layered stacking structure, and the materials from top to bottom are, in order, silica gel, wafer (silicon), solder Pb-5Sn, Cu, solder SnAg3Cu0.5, Cu, insulate layer, and the substrate, as shown in Fig. 1. Before the thermal fatigue tests, the silica gel protector is cleaned and the chips are cut out from the chipset by a wire cutter. The cyclic temperature varies from -40 to 90 °C in the thermal fatigue test, as shown in Fig. 2. It is accomplished by the specially designed heating box inserted in a bigger low temperature container which is always kept -40 °C by the liquid nitrogen. When the chips are heated, the sliding door of the heating box is close, the embedded heating tubes work. When cooled, and the sliding door is open and the heating tubes are powered off. All the chips are put into a same heating box to undergo the cyclic temperature load.

Figure 1: Structure of the chip

Figure 2: Ambient temperature cycles

To detect the fatigue failure, the electric resistance of the chips measured by a digital resistance meter for certain

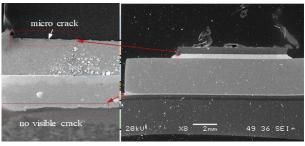

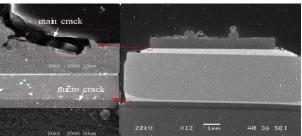

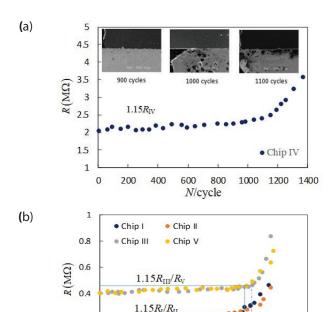

intervals. According to the sketch of electronic resistance variation during the thermal cycles, the crack morphology of chip IV when the electronic resistance increasing (RI) reaches 10 % and 15 % are respectively observed by the JSM-6301F scanning electron microscope (SEM) (JEOL, Tokyo, Japan). The samples are covered by carbon before and the analysis is conducted under 20 kV in the SEI mode, the observed SEM images are shown in Fig. 3. It can be seen that many micro-cracks appear at the interface between the wafer and solder Sn-5Pb (E12) at 10 % RI, and the micro cracks have gradually merged into a main crack when RI reaches 15 %. While at this time micro cracks start to appear at the interface between solder SnAg3Cu0.5 and Cu (E45). The locations of the E12 and E45 have been demonstrated in Fig. 1, and the representative data points at the E12 and E45 are also selected to analyze the connection between cyclic stressstrain variations from FEM analysis to the experimental thermal fatigue cracking. It is interesting that the main crack also comes into being firstly from the E12 in the other four chips. For the convenience, we define the fatique life limit Nf when the electronic resistance increasing reaches 15 % [26]. Fig. 4 shows the measured electronic resistance variations of each chip, and the tested fatigue life Nf is listed in Table 1.

**Figure 3:** SEM observations of fatigue crack morphology of IV chip: (a-c) 10% RI, (d-f) 15% RI

**Table 1:** Fatigue life limit N, for the tested I-V chips

| Chip type              | l chip | II chip | III chip | IV chip | V chip |

|------------------------|--------|---------|----------|---------|--------|

| N <sub>f</sub> /cycles | 910    | 830     | 1030     | 980     | 1040   |

#### 2.2 FEM analysis

Three dimensional thermal conduction and thermal stress analysis have been carried out to obtain inter-

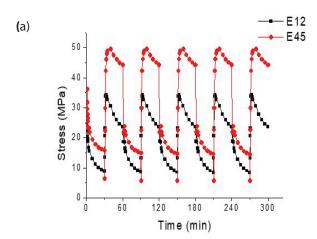

**Figure 4:** (a) Electronic RI with thermal cycles and (b) the corresponding thermal fatigue lives

400

600

800

N/cycle

1000 1200 1400

0.2

0 6

200

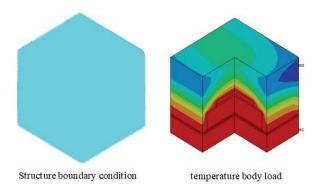

facial stress-strain fields of the chips undergoing the cyclic thermal load. The load condition is the same as what applied in the thermal fatigue tests. Here IV chip is taken as an example to depict the general features. To obtain the accurate stress and strain distribution at the interface, FEM submodel analysis is carried out, and the boundary condition of the submodel is obtained from the former thermal conduction and stress analysis of the whole chipset by automatic interpolation, as shown in Fig. 5.

Figure 5: Boundary condition interpolation

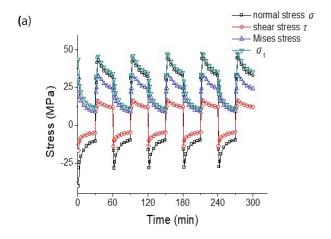

Fig. 6 shows the stress variation at the E12 and E45 with thermal cycles, where  $\sigma t = (\sigma^2 + \tau^2)^{1/2}$  donates the maximum traction when the normal stress is tensile at the interface. It can be found that the E12 is under compress, while the E45 is under tension at the heating

**Figure 6:** Stress variation near the interface edge: (a) E12; (b) E45

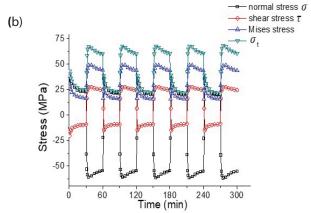

step. However, the opposite is true at the cooling step. There are two stress shocks, one is in the heating process and the other in the cooling process. The second shock is much stronger than the first one. The stress near the edge varies in the first several cycles, but it is saturated after 3 cycles. Fig. 7 shows the variations of Mises stress and equivalent strain at the E12 and E45. It can be seen that the stress range is severe at the E45, but the strain range is severe at the E12 since Pb5Sn is softer. Therefore, it follows that the actual fatigue failure mode is determined by the coupling stress and strain controlled mechanism.

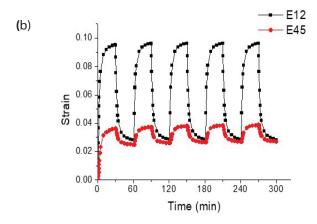

**Figure 7:** Comparison of E12 and E45: (a) Mises stress (b) Equivalent strain.

According to the instant singular field theory [27-29],

$$\sigma_{i} = \frac{K_{i}(t)}{r^{\delta_{i}(t)}}, \ \varepsilon_{e} = \frac{K_{\varepsilon}(t)}{r^{\varsigma(t)}} \tag{1}$$

where  $K_i(t)$  and  $K_s(t)$  denote the stress and strain intensity factors,  $\delta i(t)$  and  $\varsigma(t)$  are the stress and strain singular orders,  $i=\sigma,\tau$  denotes the normal and shear stress, respectively, and r denotes the distance from the singular edge.

Picking up the stress and strain distributions at the corresponding steady states along the interface edge, the

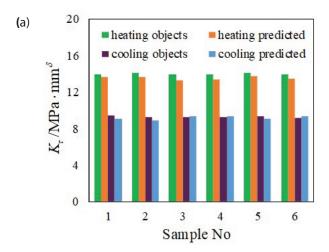

Table 2: Singular stress field parameters at the E12 interface edge

| <b>CI</b> . | Maximum stress state in the heating step |                                     |                |                                | Maximum stress state in the cooling step |                              |                |                                |

|-------------|------------------------------------------|-------------------------------------|----------------|--------------------------------|------------------------------------------|------------------------------|----------------|--------------------------------|

| Chip<br>No. | Normal Stress                            |                                     | Shear Stress   |                                | Normal Stress                            |                              | Shear Stress   |                                |

| NO.         | $\delta_{\sigma}$                        | K <sub>σ</sub> /MPa.mm <sup>δ</sup> | $\delta_{	au}$ | $K_{\tau}$ /MPa.mm $^{\delta}$ | $\delta_{\sigma}$                        | $K_{\sigma}/MPa.mm^{\delta}$ | $\delta_{	au}$ | $K_{\tau}$ /MPa.mm $^{\delta}$ |

| I           | 0.04119                                  | -20.53                              | 0.03882        | -9.382                         | 0.1551                                   | 13.59                        | 0.04223        | 14.00                          |

| П           | 0.04305                                  | -19.98                              | 0.04005        | -9.202                         | 0.1524                                   | 12.99                        | 0.04350        | 13.59                          |

| III         | 0.05363                                  | -18.12                              | 0.03861        | -9.241                         | 0.1627                                   | 12.55                        | 0.04298        | 13.75                          |

| IV          | 0.04186                                  | -19.55                              | 0.04144        | -8.939                         | 0.1559                                   | 12.63                        | 0.04431        | 13.45                          |

| V           | 0.05254                                  | -17.77                              | 0.03867        | -9.134                         | 0.1758                                   | 11.30                        | 0.04137        | 13.66                          |

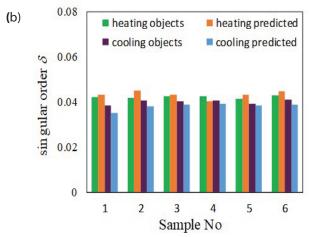

| <b>Table 3:</b> Singular stress field parameters at the E45 interface e | Table | e 3: Singular | stress field | parameters at the | E45 interface ed | ae |

|-------------------------------------------------------------------------|-------|---------------|--------------|-------------------|------------------|----|

|-------------------------------------------------------------------------|-------|---------------|--------------|-------------------|------------------|----|

| GI I        | Maxii             | mum stress stat                  | te in the he   | ating step                      | Maximum stress state in the cooling step |                              |                |                                |

|-------------|-------------------|----------------------------------|----------------|---------------------------------|------------------------------------------|------------------------------|----------------|--------------------------------|

| Chip<br>No. | Normal Stress     |                                  | Shear Stress   |                                 | Normal Stress                            |                              | Shear Stress   |                                |

| INO.        | $\delta_{\sigma}$ | $K_{\sigma}$ /MPa.mm $^{\delta}$ | $\delta_{	au}$ | $K_{\tau}$ /MPa.mm <sup>δ</sup> | $\delta_{\sigma}$                        | $K_{\sigma}/MPa.mm^{\delta}$ | $\delta_{	au}$ | $K_{\tau}$ /MPa.mm $^{\delta}$ |

| I           | 0.04012           | 27.18                            | 0.03184        | -12.87                          | 0.01688                                  | -53.85                       | 0.04195        | 19.78                          |

| Ш           | 0.03348           | 28.71                            | 0.03523        | -12.14                          | 0.01957                                  | -52.44                       | 0.04322        | 19.18                          |

| III         | 0.07525           | 21.58                            | 0.02823        | -13.35                          | 0.07769                                  | -35.02                       | 0.03464        | 21.57                          |

| IV          | 0.07966           | 21.23                            | 0.02806        | -13.40                          | 0.11488                                  | -27.59                       | 0.03080        | 22.52                          |

| V           | 0.1171            | 16.42                            | 0.02805        | -13.36                          | 0.1629                                   | -19.83                       | 0.03049        | 22.53                          |

If a unit length is taken, Eq. (3) can be simplified as

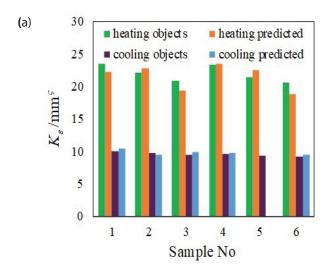

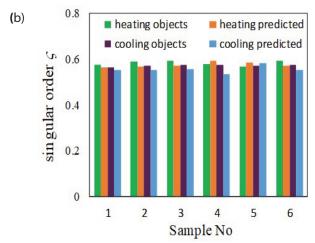

Table 4: Singular strain field parameters at the E12 and E45 interface edges

| cl .        |               | E1:                              | 2             |                                  | E45           |                                  |               |                                  |

|-------------|---------------|----------------------------------|---------------|----------------------------------|---------------|----------------------------------|---------------|----------------------------------|

| Chip<br>No. | Maximum state |                                  | Minimum state |                                  | Maximum state |                                  | Minimum state |                                  |

| NO.         | ς             | K <sub>ε</sub> / mm <sup>ς</sup> |

| I           | 0.5855        | 2.166E-03                        | 0.5660        | 9.871E-04                        | 0.5482        | 1.156E-03                        | 0.6585        | 1.297E-04                        |

| II          | 0.5829        | 1.853E-03                        | 0.5768        | 7.819E-04                        | 0.5647        | 8.242E-04                        | 0.7642        | 2.398E-05                        |

| III         | 0.5745        | 1.661E-3                         | 0.5588        | 7.514E-04                        | 0.4760        | 2.433E-03                        | 0.6023        | 2.093E-04                        |

| IV          | 0.5883        | 1.322E-03                        | 0.5854        | 5.773E-04                        | 0.4654        | 2.823E-03                        | 0.6011        | 2.429E-04                        |

| V           | 0.5775        | 1.312E-03                        | 0.5599        | 6.341E-04                        | 0.4384        | 3.728E-03                        | 0.5710        | 2.785E-04                        |

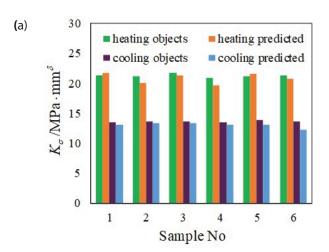

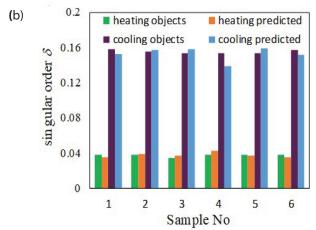

stress and strain intensity factors and singular orders can be determined numerically. Applying the FEM submodel analysis to each chip, the singularity parameters as described above are summarized and listed in Tables 2-4, respectively.

## 2.3 Thermal fatigue models based on interfacial singularity

Thermal cycles lead to the coupled stress and strain cycles, though their peaks do not appear simultaneously, which attributes to the visco-properties of solder materials. This fact means that both stress and strain cycles contribute to thermal fatigue failures. Instead of using stress or strain as the parameters for thermal fatigue life evaluation, here the stress and strain intensity factor ranges and their corresponding singular orders are adopted to formulate the thermal fatigue law. At the interface edge, the ranges of stress and strain are written as

$$\Delta \sigma_{j} = \frac{K_{j \max}}{r^{\delta_{\max}}} - \frac{K_{j \min}}{r^{\delta_{\min}}}, \Delta \varepsilon = \frac{K_{\varepsilon \max}}{r^{\varsigma_{\max}}} - \frac{K_{\varepsilon \min}}{r^{\varsigma_{\max}}}$$

(2)

For the materials with tiny defects, the fatigue strengths and thresholds of fatigue crack propagation match those without defects. Namely, only several points with large stress in materials generally cannot affect fatigue characteristics. Therefore, using the stress-strain range within a region to describe the thermal fatigue behavior is more accurate than only by one or two points.

Here the concept of characteristic length of fatigue failure is introduced, i.e., when the average stress or strain range within a characteristic length l arrives at or exceeds the fatigue limit, the thermal fatigue crack begins to initiate or propagate [30]. The average stress range  $\Delta \overline{\sigma}$  within l at the interface edge can be expressed as

$$\Delta \overline{\sigma} = \frac{1}{l} \left[ \int_{0}^{l} \frac{K_{\text{max}}}{r^{\delta_{\text{max}}}} dr - \int_{0}^{l} \frac{K_{\text{min}}}{r^{\delta_{\text{min}}}} dr \right] =

= \frac{1}{l^{\delta_{\text{max}}}} \frac{K_{\text{max}}}{1 - \delta_{\text{max}}} - \frac{1}{l^{\delta_{\text{min}}}} \frac{K_{\text{min}}}{1 - \delta_{\text{min}}} \tag{3}$$

If a unit length is taken, Eq. (3) can be simplified as

$$\Delta \overline{\sigma} = \frac{K_{\text{max}}}{1 - \delta_{\text{max}}} - \frac{K_{\text{min}}}{1 - \delta_{\text{min}}}$$

(4)

Then the range of stress and strain intensity factors can be written as

$$\begin{split} & \Delta K_{\sigma} = \frac{K_{\sigma \max}}{1 - \mathcal{S}_{\sigma \max}} - \frac{K_{\sigma \min}}{1 - \mathcal{S}_{\sigma \min}}, \Delta K_{\tau} = \\ & = \frac{K_{\tau \max}}{1 - \mathcal{S}_{\tau \max}} - \frac{K_{\tau \min}}{1 - \mathcal{S}_{\tau \min}}, \Delta K_{\varepsilon} = \frac{K_{\varepsilon \max}}{1 - \mathcal{S}_{\max}} - \frac{K_{\varepsilon \min}}{1 - \mathcal{S}_{\min}} \end{split} \tag{5}$$

where  $\Delta K_{\sigma}$  and  $\Delta K_{\tau}$  represent the multi-axes effects when both normal and shear stress are considered.

Therefore, strain-controlled and stress-strain controlled fatigue laws are respectively considered, as shown in Eqs. (6-7).

$$\left(\Delta K_{\varepsilon}\right)^{m_{\rm l}} N_{\rm f} = C_{\varepsilon} \tag{6}$$

$$\left(\Delta K_{\varepsilon}\right)^{m_{\rm i}} \left[ \left(\Delta K_{\sigma}\right)^2 + \left(\Delta K_{\tau}\right)^2 \right]^{m_2} N_{\rm f} = C_{\varepsilon\sigma} \tag{7}$$

where  $m_1,\, m_2,\, C_\epsilon,$  and  $C_{\epsilon\sigma}$  are constants determined by test results.

By fitting the results of thermal fatigue tests and the singularity parameters at the failure interface obtained from FEM analysis, one obtains

$$\left(\Delta K_{\varepsilon}\right)^{0.4} N_{\rm f} = 87.9 \tag{8}$$

$$(\Delta K_{\varepsilon})^{0.4} [(\Delta K_{\sigma})^2 + (\Delta K_{\tau})^2]^{1.74} N_{\rm f} = 3.93 \times 10^7$$

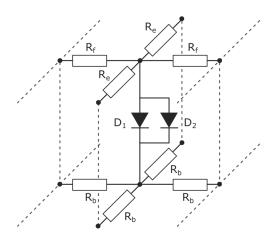

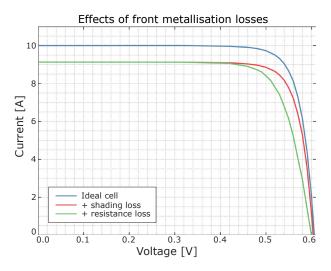

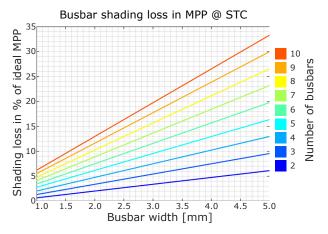

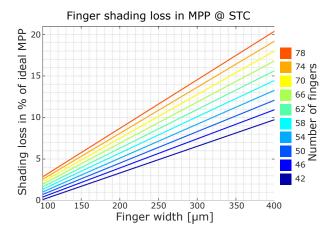

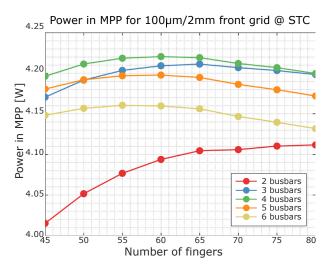

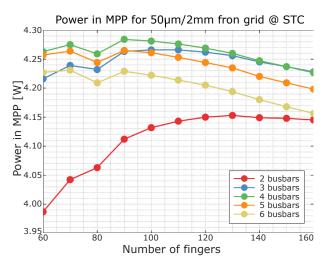

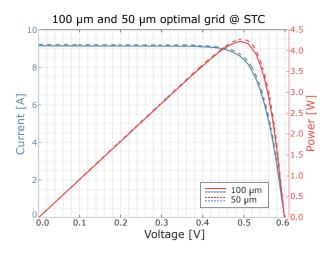

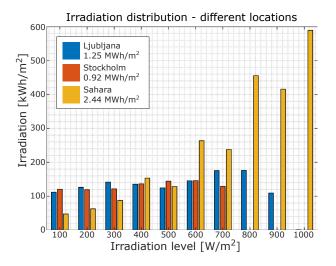

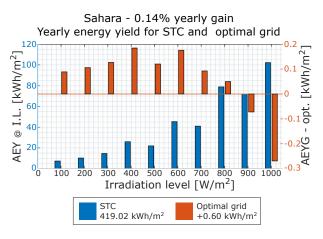

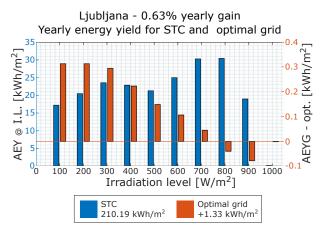

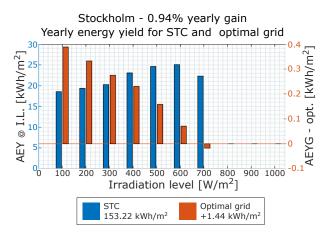

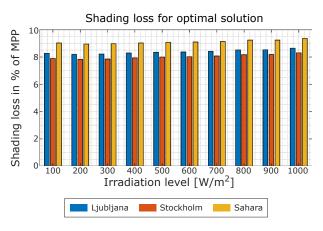

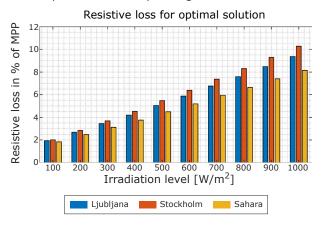

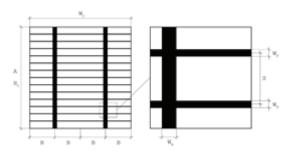

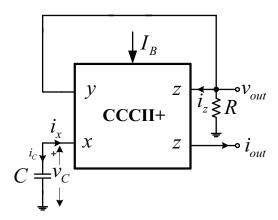

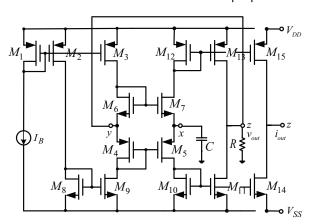

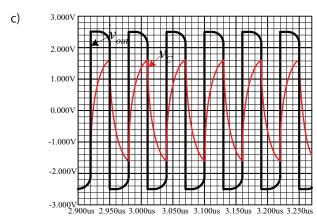

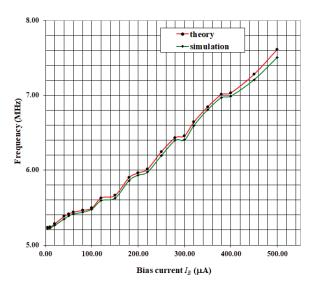

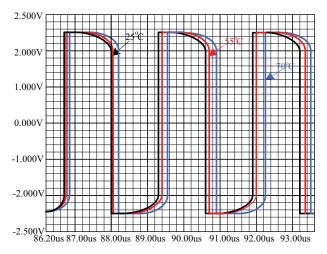

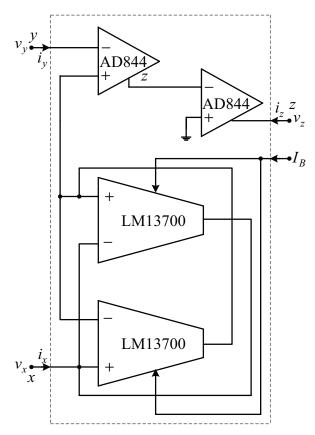

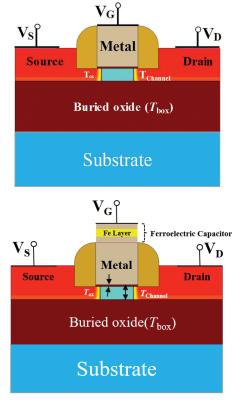

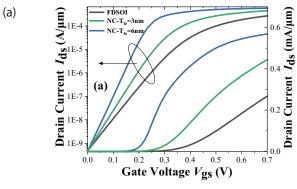

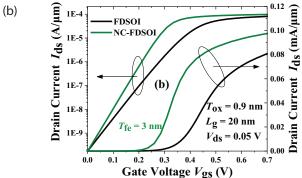

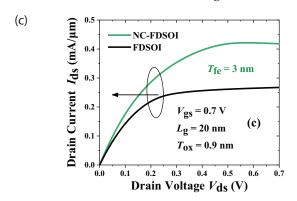

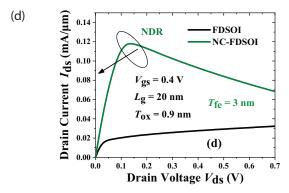

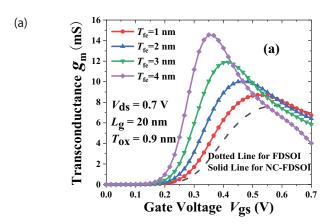

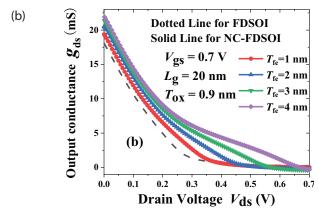

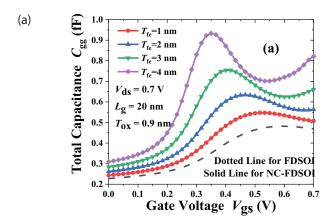

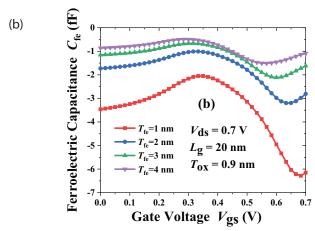

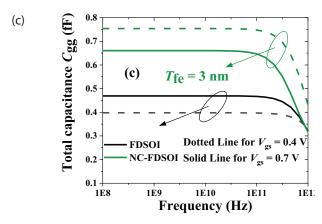

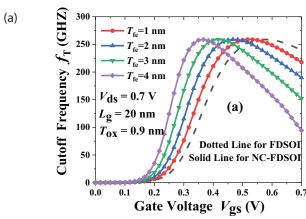

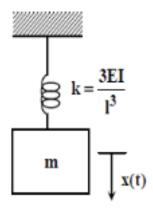

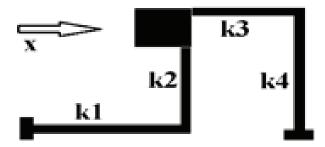

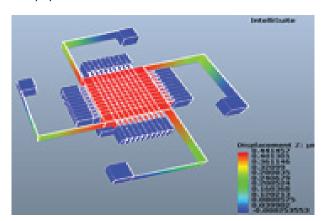

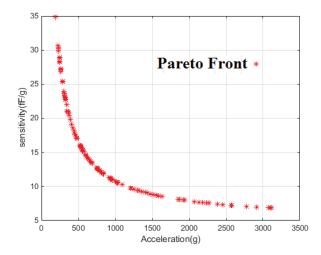

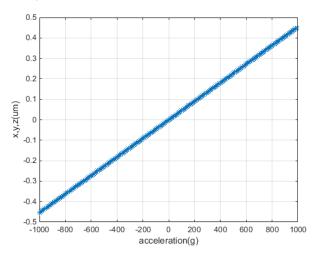

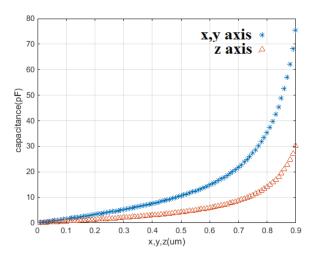

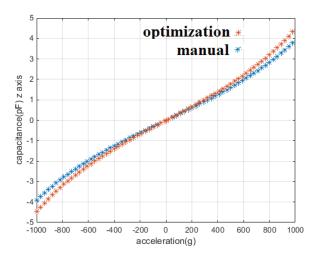

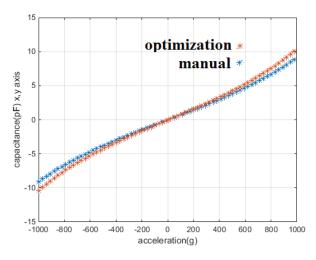

(9)